在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

限制FPGA最大频率的因素:

(1)组合逻辑延时

越多的门电路,所构成的组合逻辑延时越大,以ALTERA C4为例,FPGA实际上是用四输入查找表(LUT, Look-Up-Tables)的方式实现门电路的,变量数目小于4的所有组合逻辑延时相同,大于4时需要多个查找表组合,延时增加。

(2)信号路径延时

路径延时是所有延时中最需要考虑的,甚至可以占到总延时的一半以上,一般EDA工具不会寻找最快的路径,需要施加时序约束。

(3)时钟偏移、抖动和延时

时钟传到每个触发器的时间会由于距离时钟源路径长度不同而有偏移,时钟偏移可以通过走时钟树的结构解决,但时钟偏斜永远存在,不可能消除。时钟抖动是由于温度分布,信号串扰等因素使得晶振、PLL等产生的时钟信号周期不会严格相等而造成的。

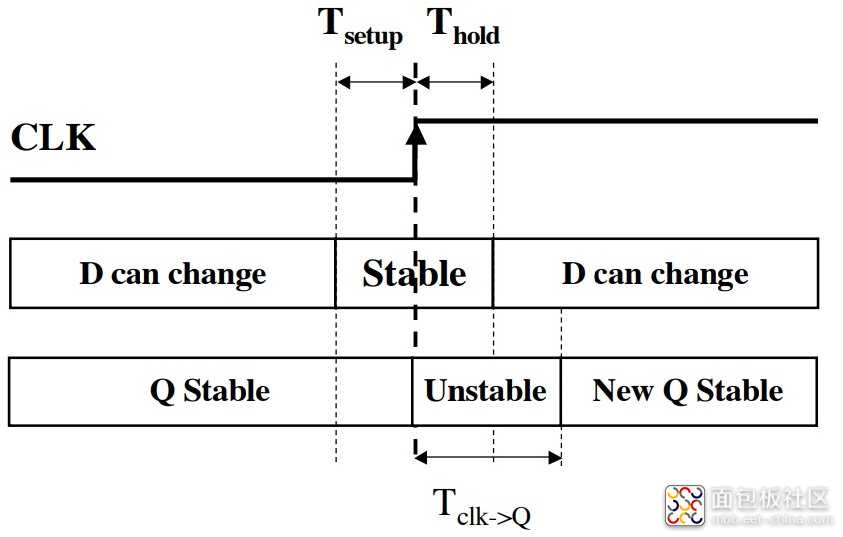

(4)触发器建立时间Tsu、保持时间Th

输入管脚的数据必须在时钟有效之前提前出现的时间称为建立时间Tsu;保持时间Th是指在时钟上跳沿后,数据必须保持的最小时间。

(5)触发器时钟到输出时间Tco

在时钟有效后,D的数据并不能立即传到Q端,这段等待的时间就是触发器的时钟到输出时间。

以上时间是触发器固有时间,无法更改。

(6)功耗

合理的时序约束可以提高运行频率,但往往会使得功耗增加, 在性能要求不高的移动设备中,需要综合考虑。

(7)高扇出信号延时

高扇出信号是指带多负载的信号,在多负载情况下,信号的延时会增大,信号到达某些负载的时间增加,从而可能造成该信号相对时钟信号是一个晚到的信号。

/4

/4