电子电路发展史——从真空管、晶体管到集成电路

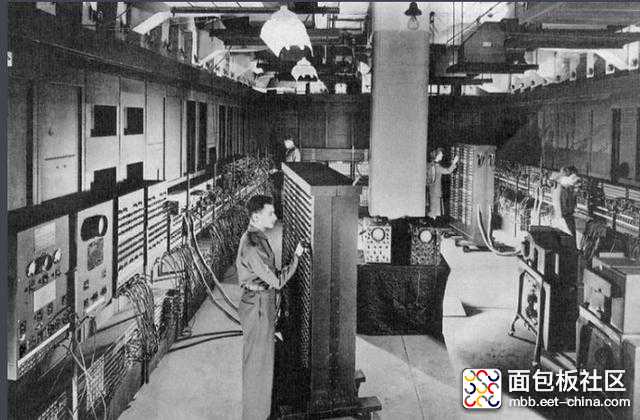

真空管和ENIAC

计算机的终计算是通过数字电路的开关状态的切换来实现的,包括信息传递和设备联通等。数字电路的发展初,是在上个世纪50年代之前,电路是由真空管组成。由弗莱明发明的二极管,德福雷斯特改良的真空三极管,在此基础上产生了台通用计算机ENIAC(Electronic Numerical Integrator And Compute)。

晶体管

晶体管的发明源于贝尔实验室的研究,立足于找到一种价格便宜,耗电少或无耗电且不会升温的元件。该元件还必须易于制造,切换速度快,体积小。1974年由William Shockley领导下,John Bardeen和Walter Brattain发明了满足这些特性的晶体管。晶体管体积小,电阻也小,没有活动部件(因此损耗很小),并且可靠,几乎不发热。晶体管的发明,使得电子电路的研究空前活跃,晶体管性能,尺寸和可靠性的新发展几乎每个月都会发生。

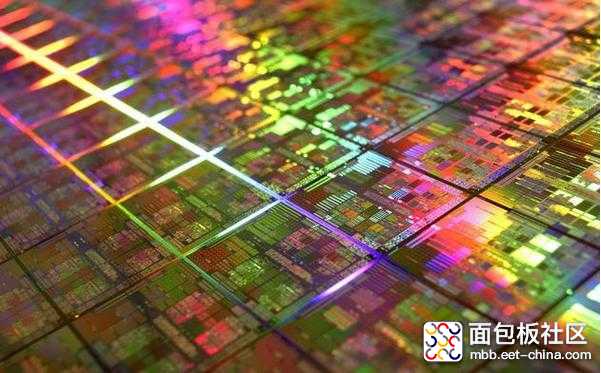

德州仪器(Texas Instruments)的杰克基尔比(Jack Kilby)是世界上个向世界展示将很多这些晶体管放在单个晶圆(硅片)上的人之一。1959年,他为个IC或集成电路申请了。到了20世纪60年代,晶体管变得越来越小,我们制造复杂的IC并构建更快,更小的"计算机"。

摩尔定律

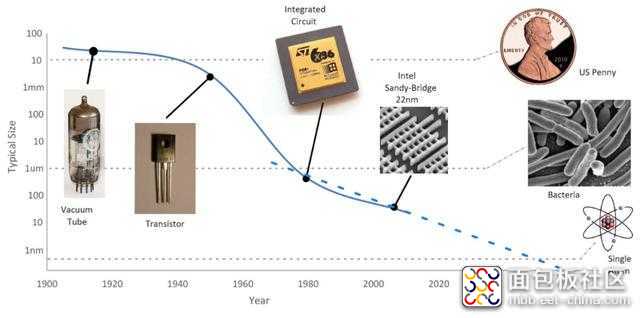

上世纪五十年年代,飞兆半导体和英特尔的联合创始人戈登摩尔(Gordon Moore)发表了一篇论文,指出每个集成电路的元件数量将在未来十年每年增加一倍。1975年,他回顾了他的预测,并表示组件的数量现在每两年增加一倍。这就是着名的摩尔定律。

1971年个半导体工艺之一是10微米(或者比一米小10万倍)。到2001年,它是130纳米,比1971年小近80倍。

截至2017年,的晶体管工艺为10纳米,相比较人头发直径是100微米,比今晶体管大近10,000倍。

摩尔定律危机

随着大规模电路发展,晶体管越来越小,集成数量成几何级增加,其制造工艺却越来越难了。克服这些技术和工艺壁垒不仅需要大量的时间和研究,还需要大量的资金和投资。因此,摩尔定律也中的时间也逐渐放缓,甚至可它可能会很快不成立,摩尔定律危机爆发(当然如果没有巨大变革这是必然的)。

英特尔花了大约两年半的时间才从2012年的22纳米工艺发展到2014年的14纳米工艺,之后10纳米的研究和开发一直就问题不断,多次延迟,可能要到2019年才能上市,不过好消息是AMD 7纳米的显卡和CPU会在2019年上市(见虫虫近一篇文章《AMD未来产品展望...》)。因为摩尔定律不是真正的定律,只是一种预测或推测。尽管芯片制造商一直致力于实现并保持目标,但这样做变得越来越困难。

援引摩尔本人2015年的话:"我认为摩尔定律将在未来十年左右在消亡"。

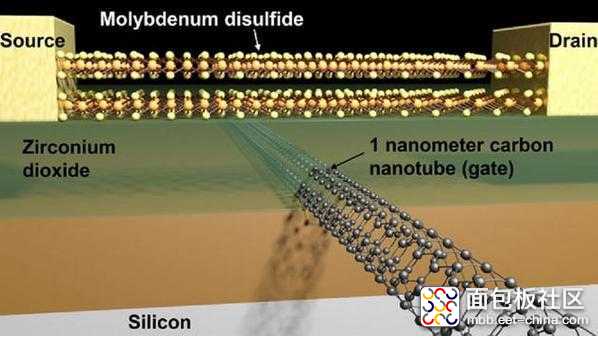

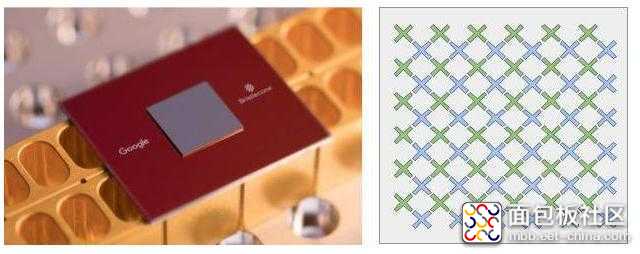

量子隧穿

随着电子元件越来越小(纳米级),量子特性和效应逐渐显现。随着我们不断减小晶体管的尺寸,其Pn结耗尽层的尺寸也越来减小。耗尽层非常重要,用于阻止电子的流动。研究人员通过计算得出,由于电子在其耗尽区中的隧道效应,小于5nm的晶体管将无法阻止电子流动。由于隧穿,电子将不会感知耗尽区域,直接 "跨穿"。如果不能阻止电子流动,晶体管就会失效。

电流和加热效应

除了量子隧穿和物理极限,还有两个很制约的工艺问题,那就是晶体管小尺寸的加热效应。随着晶体管变小,晶体管往往会变得更"漏",即使在OFF状态下。也不可避免要让一些电流通过。这称为漏电流。如果我们将漏电流设为100 nA如果CPU有1亿个晶体管,那么泄漏电流将为10A。这将在几分钟内耗尽手机电池。较高的栅极电压可以减少漏电流量,但这会导致更多的加热效应。即使不考虑到它,每个时钟计算本身也消耗了大量的热量。制造商必须使用这些属性并使它们恰到好处地防止这些影响。随着流程变得越来越小,工艺越来越难。

高漏电流还会导致暗硅和暗记忆的问题。即使我们芯片中可能有很多晶体管,但大多数晶体管必须保持关断以防止芯片过热和熔化。所有这些OFF状态的晶体管大量占用了可用于放置其他元件的空间。这导致一个问题:我们真的需要更小,还是我们改进现有的芯片设计?

未来展望

5纳米设计

考虑到所有这些因素,英特尔执行官和国际半导体技术路线图表示,5纳米可能是能达到的极限尺寸。预计5纳米将在2021年首次亮相。那么在那之后我们还能期待什么呢?

Dennard's Scaling-Dennard Scaling被认为是摩尔定律的姊妹法。它由Robert Dennard于1974年制定,并指出随着晶体管变小,它们的功率密度也会降低。这意味着随着晶体管变小,操作它们所需的电压和电流量也将减少。这个定律允许制造商减少晶体管的尺寸,并通过每次迭代的大幅跳跃来提高时钟速度。然而在2007年左右,Dennard的Scaling崩溃了。这是因为在较小的尺寸下,泄漏电流会导致晶体管升温并产生进一步的损耗。

我们可能已经注意到,尽管晶体管变得更小,但是在过去十年中CPU计算速率并没有上升,这是由于Dennard Scaling崩溃。高时钟速率下的高损耗也是智能手机芯片使用较低时钟速度(通常为1.5 GHz)的原因。

库梅定律

通过改进当前的芯片实现并具有更好的指令流水线,我们可以改善芯片的性能。所以斯坦福的教授乔纳森·库梅提出了库梅(Koomey)定律:每焦耳能量的计算次数将每1.5年翻一番。预计这种情况将持续到2048年,届时Landauer的原理和热力学简单定律将阻止进一步的改进。目前,Landauer Limits的计算机效率约为0.00001%。

多核架构

传统的编程语言(如Java,C ++和Python)只能在单个设备上运行。但随着设备变得越来越小和越来越便宜,我们可以在许多芯片上同时或并行地运行相同的程序,从而进一步提高性能。在这方面,像Golang,Node这样的语言将扮演更重要的角色。

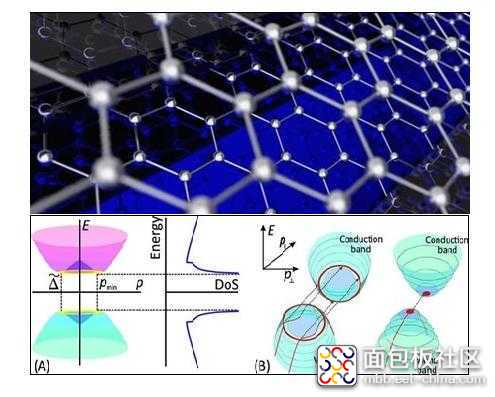

新材料研究

世界各地的研究人员正在寻找更新,更创新的方法来制造更小更快的晶体管。已经证明,氮化镓和石墨烯等材料在更快的开关频率下具有更小的损耗。

/5

/5