由于CMOS电路具有极高的输入阻抗,极易感应干扰电压而造成逻辑混乱,甚至损坏。因此,对于CMOS数字电路空闲的引脚不能简单地不管,应根据CMOS数字电路的种类、引脚功能和电路的逻辑要求,分不同情况进行处置。

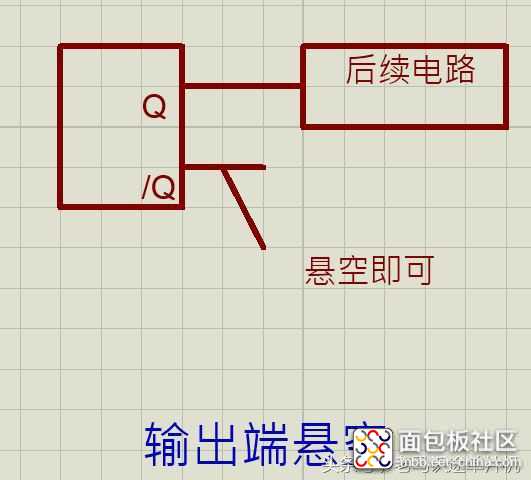

1、对于多余的输出端,一般将其悬空即可。如下图所示;

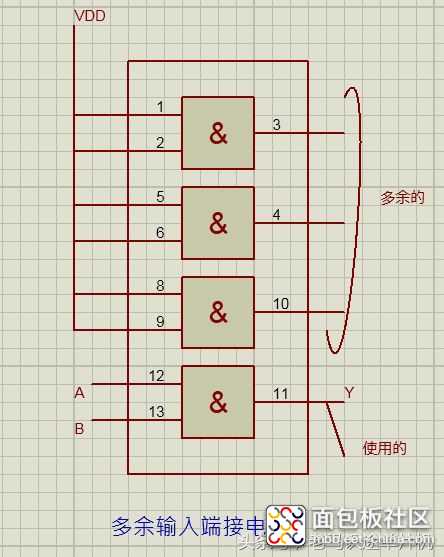

2、CMOS数字电路往往在一个集成块中包含有若干个互相独立的门电路或触发器。对于一个集成块中多余不用的门电路或触发器,应将其所有输入端接到系统的正电源VDD,如下图所示。

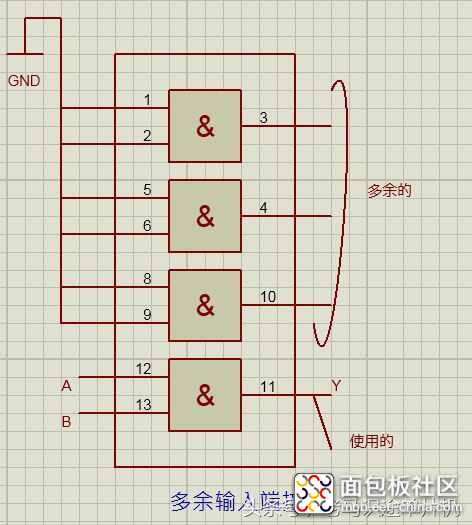

也可将一个集成块中多余不用的门电路或触发器的所有输入端接到系统的地端。

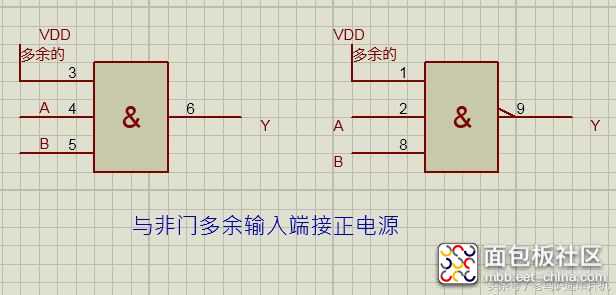

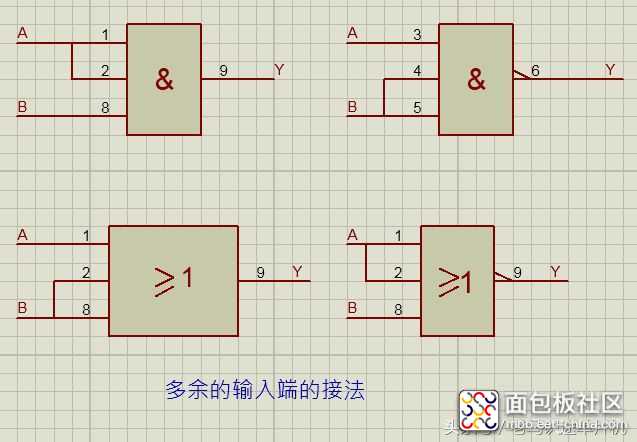

3、门电路往往具有多个输入端,而这些输入端不一定全都用上。对于与门、与非门多余的输入端,应将其接正电源VDD,如下图所示,以保证其逻辑功能正常。

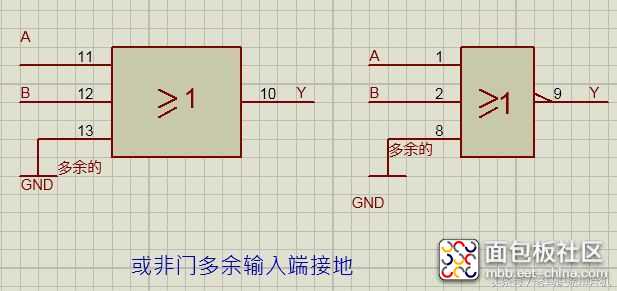

4、对于或门或非门多余的输入端,应将其接地,如下图所示,以保证其逻辑功能正确。

5、对于与门、与非门、或非门多余的输入端,还可以将其与使用中的输入端并接在一起,如下图所示,也能保证其正常的逻辑功能。

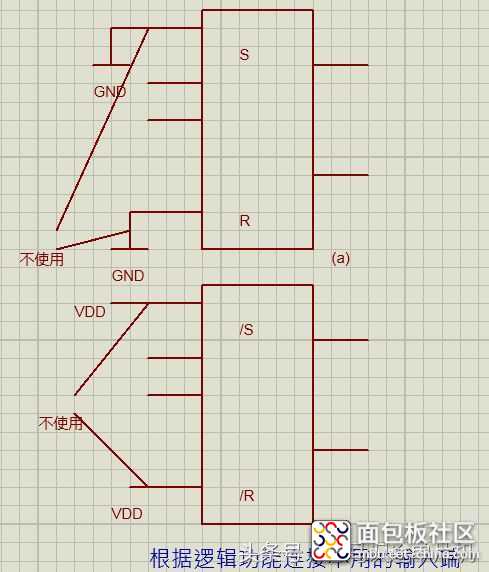

6、对于触发器、计数器、译码器、寄存器等数字电路不用的输入端,应根据电路逻辑功能的要求,将其接系统的正电源VDD或地端。例如,对于不用的清零端R(“1”电平清零)或置位端S(“1”电平置位),应将其接地。如下图(a)所示。而对于不用的清零端/R(“0”电平清零)或置位端/S(“0”电平置位),应将其接正电源VDD。

/4

/4