使用 HDI 技术的主要目的是在更小的电路板上封装更多的组件。为 HDI 选择更小的封装可增加电路板功能和组件密度。

因此,虽然设计高密度互连板有许多问题需要解决。使用占用空间较小的组件可以实现密集的住宿。在本文中,我们将从以下几个方面进行研究:

目录

1什么是 HDI 布局?

2高密度互连的元件选择

2.1正确放置元件的重要性

3什么是 HDI PCB 封装?

4用于 HDI 的 SMD 封装尺寸更小

4.1占用空间更少的标准 IC 封装

4.1.1小外形封装 (SOP)

4.1.2BGA

4.1.3QFP

4.1.4QFN

什么是 HDI 布局?

HDI 布局可在有限的电路板空间内容纳更多组件。这种设计面临以下挑战:

- 董事会工作区有限

- 使用占用空间较小的组件

- 组件和其他物理特征之间的密集间距

- 电路板两侧的元件数量增加

- 更长的轨迹会增加信号传播延迟

- 电路板将需要更多的走线

带有封装的 HDI PCB 布局

这过孔类型的选择显着影响高密度布局。关于 HDI 板中使用的过孔类型没有硬性规定。设计人员可以选择从盲/埋微孔到传统的通孔微孔。

盲/埋微孔可以交错或堆叠排列,根据电路板设计要求. 过孔的选择将决定工艺持续时间、步骤和成本。因此,应考虑这些因素以优化成本和制造复杂性。

高密度互连的元件选择

HDI的组件选择

组件选择是一个耗时的过程HDI设计. 安装在电路板上的元件将决定走线宽度、布线要求、钻孔尺寸和叠起. PCB 上有限的可用区域限制了元件封装的尺寸。同时,细间距元件会增加正确布线所需的层数。因此,这两个因素之间的优化将提供理想的组件尺寸。

性能、包装或土地格局、可追溯性和可用性是决定 HDI 组件选择的四个因素。

这组件的放置影响董事会的运作和效率。谈到 HDI,组件将比传统布局更接近。即使组件彼此靠近,也不会电磁干扰应该发生。这将降低走线的信号效率。还,寄生电容或电感不应出现在相邻的引脚或焊盘之间。因此,有可能信号完整性改进在将元件放置在 PCB 上之前,必须进行适当的研究。

过孔位置还取决于元件放置。因此,如果过孔位置不对称,可能会导致整个电路板上的应力不均匀。这样一来,董事会的实力就会受到影响。

查看我们的教程如何在 KiCad 中放置组件.

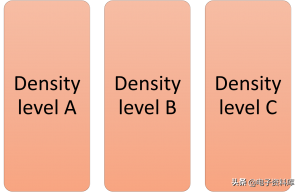

什么是 HDI PCB 封装?元件封装是图案电路板布局表示将在此期间焊接的组件的位置电路板组装. 没有专门为高密度互连板设计的特定类型的封装。设计人员试图使组件占用空间更小,以减少占用的空间。根据 IPC-7351,封装一般分为三类。

封装的IPC分类

- 密度等级A:这种封装分类适用于低密度产品应用。波峰焊最适合密度级别 A 的组件。与其他两个相比,这些封装占用更多的电路板面积。

- 密度等级 B:本部分适用于具有中等元件密度的电路板的元件封装。在回流焊接的情况下,密度级别 B 的封装提供了强大的焊接连接条件。这些足迹是标称尺寸。

- 密度等级 C:这些封装适用于 HDI 等高密度板。与 A 级和 B 级相比,这些足迹的大小将更小。

现在,我们已经意识到密度级别 C 的占用面积是最小的,最适合高密度互连板。但是在我们决定使用哪个之前,这些足迹应该满足工控机-7351标准。它们还应符合供应商的制造和组装能力。

HDI PCB 填充了小型 SMD 封装

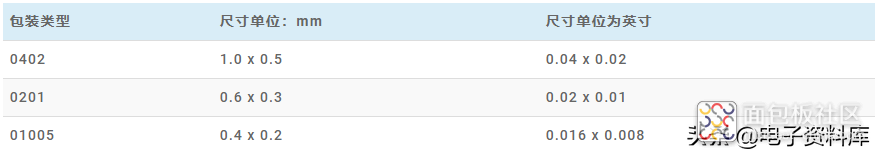

占用空间较小的 SMD 封装最适合 HDI 板。一些例子是0402、0201、001005等。这些封装的尺寸如下所示。

电阻器和电容器通常可用于这些微型SMT封装. 表面贴装电感器采用 0805 (2.0 x 1.3 mm) 和 0603 (1.5 x 0.8 mm) 封装。还有其他组件,如变压器、石英晶体谐振器、陶瓷谐振器、滤波器等,在这些极小的封装样式中不可用。但我们必须确保这些组件紧凑且与取放机械,与组件包样式无关。

说到 IC 封装,下面列出了较小的版本:

- TSOP:随附的薄型小轮廓包0.5mm引脚间距。

- SSOP:收缩小外形封装,引脚间距为0.635mm.

- QSOP:四分之一小轮廓包带0.635mm引脚间距。

- VSOP:非常小的轮廓包0.4、0.5 或 0.65 毫米引脚间距。

BGA

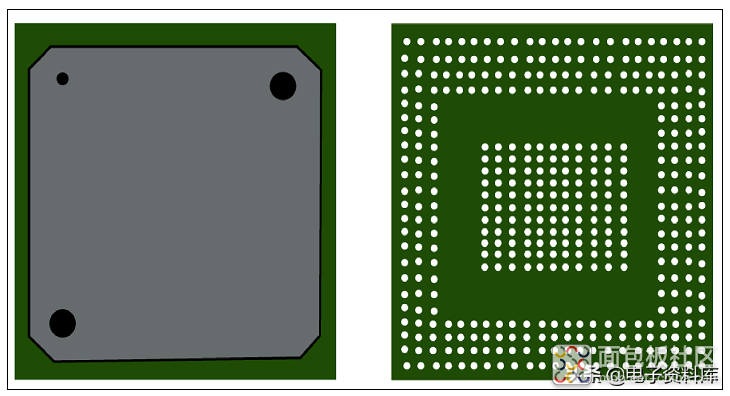

BGA 元件焊盘图案

BGA封装常用于HDI板。这些组件的精细间距和实现过孔焊盘技术有助于满足这些类型的电路板所需的紧凑性。由于引脚位于组件表面下方,因此这些组件的空间消耗甚至减少了。可提供间距小至 0.4mm、0.5mm 等的 BGA 组件。

请参阅我们的文章以了解如何突破0.4mm BGA和如何突破0.5mm BGA。

一个 TQFP32 封装

四方扁平封装还提供了一些非常适用于高密度应用的变体。

- LQFP:薄型四方扁平封装采用薄型,可提供不同的引脚间距。高度保持在1.4mm.

- TQFP:薄四方扁平封装是普通 QFP 的更薄版本,具有更小的外形尺寸。

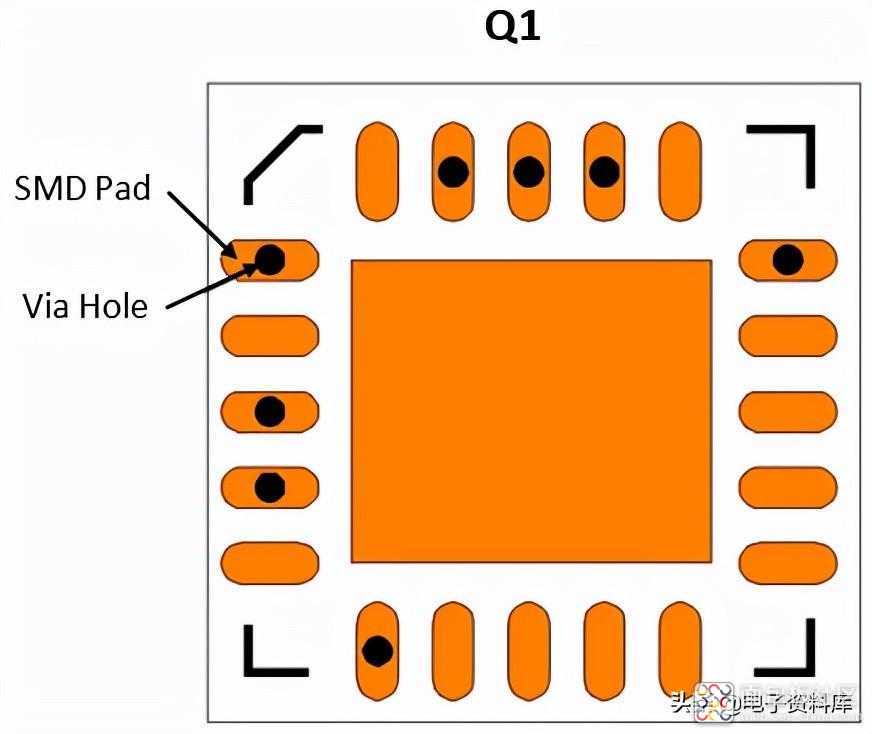

QFN

典型的 QFN 焊盘图案

四方扁平无引线封装由于其占用空间小、周边有输入-输出焊盘和热焊盘,因此适用于 HDI。因此,当布线拥挤且布局密集时,这些封装很容易散热。微型引线框架 QFN 封装是微型变体的一个示例,其平均高度介于0.35mm 至 1.45mm.

因此,从上面讨论的所有主题中,我们可以总结有关 HDI 中组件封装的以下几个方面:

- HDI 板每平方英寸的元件密度总是大于常规板。

- 使用高引脚数和低间距组件。

- 较小的占地面积使组件彼此更接近,从而缩短信号路径长度,从而提高信号质量。

- 组件封装应始终遵循 IPC-7351 标准以及DFM 要求制造商的。

- 使用via-in-pads 布线组件。

来源:电子资料库

/5

/5