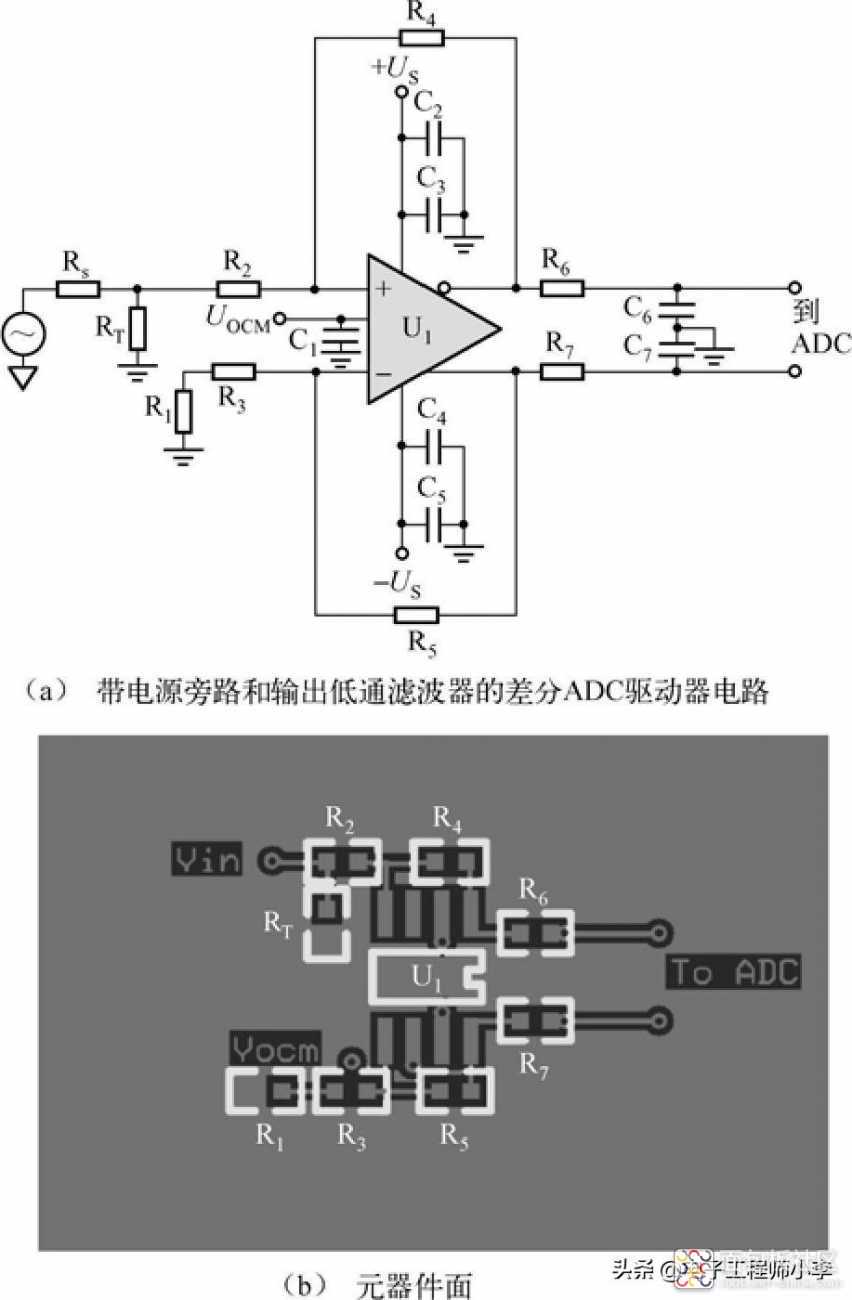

高速差分ADC驱动器的PCB设计

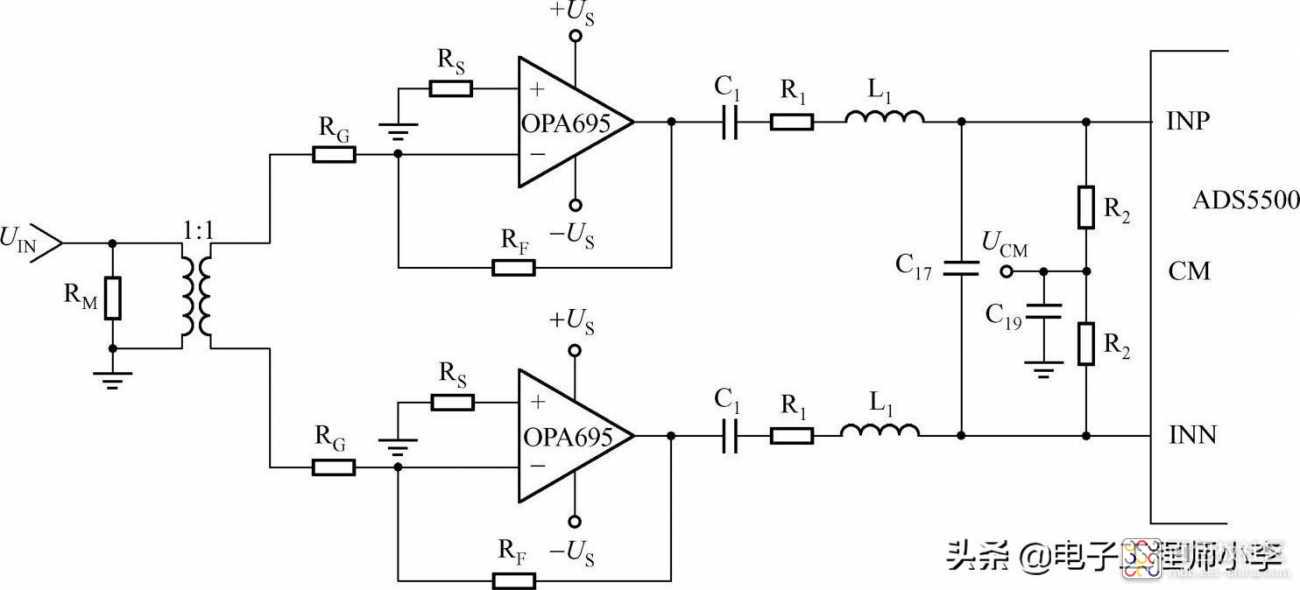

一个带电源旁路和输出低通滤波器的差分ADC驱动器电路和PCB图,如图11-15所示。为了减少不良寄生电抗,应尽量缩短所有布线的距离。在FR-4上的外层50Ω PCB电路板布线会贡献大约2.8pF/in和7nH/in的寄生电感;在内层50Ω布线则会使此类寄生电抗增加约30%。

图11-15 差分ADC驱动器电路和PCB图

图11-15

差分ADC驱动器裸露焊盘的PCB设计

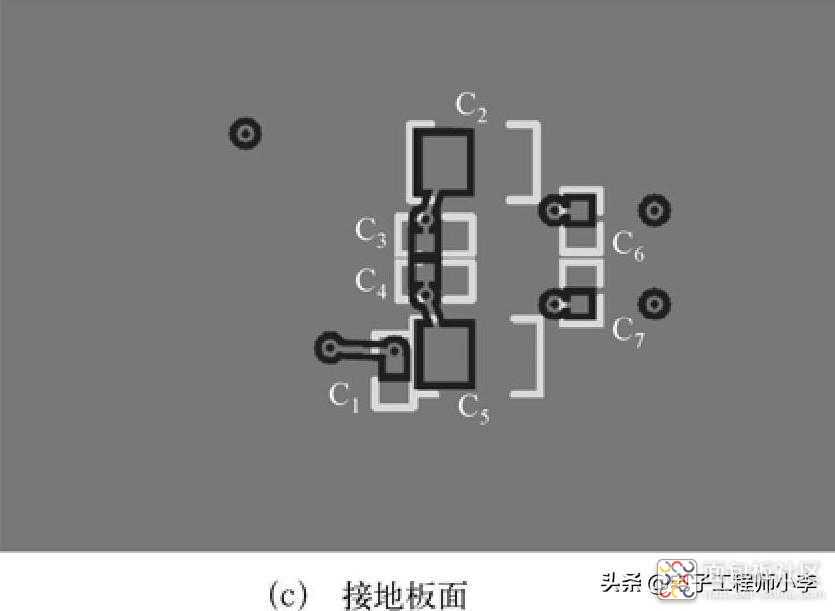

差分ADC驱动器ADA4950-x系列芯片都具有裸露的焊盘,裸露焊盘的PCB设计示意图,如图11-16所示,裸露焊盘采用过孔与接地平面连接。

图11-16

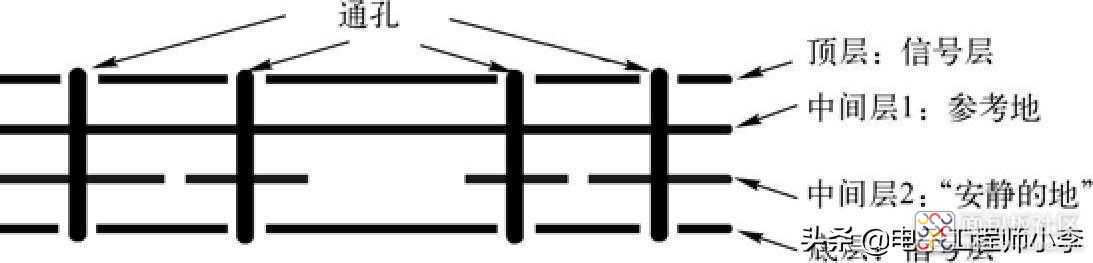

注意: 过孔用来实现不同层的互连,如图11-17所示,过孔存在电感和电容。对于一个1.6mm(0.063in)厚PCB上的0.4mm(0.0157in)的过孔,过孔电感≈ 1.2nH。在FR-4介质材料上,对于一个1.6mm(0.063in)的间隙,围绕孔周围0.8mm(0.031in)的焊盘,电容≈ 0.4pF。在下列公式中,ε r = PCB介质材料系数(介质材料FR-4的系数≈ 4.5)。

图11-17 过孔示意图

低失真高速差分ADC驱动电路的PCB设计

差分布局的一些考虑

由于越来越多的ADC采用了差分输入结构,所以差分驱动器已成为ADC驱动必要的器件。目前,有众多技术可以将宽频带双运算放大器应用于差分ADC驱动器。理论上,差分结构可以消除二次谐波失真。实际上,只有精心布局的PCB能够有效地抑制二次谐波失真。采用对称设计,可以通过差分反相配置来使放大器获得最好的转换速率。为了使差分结构对于二次谐波失真的消减能力达到最佳,必须对PCB的板层数、特征阻抗、元件位置、地线层、对称性、电源去耦合及其他许多方面进行优化,这些在设计PCB时都需要被考虑到。

采用对称设计,需要考虑元件对称性和信号路径对称性。元件对称性是指所有的板上元件都按照特定的模式排列。信号路径对称性是指更注重的是信号路径的对称性而不是元件布局上的对称。

差分ADC驱动电路

一个采用运算放大器OPA695构成的差分驱动器与ADS5500 ADC的接口电路如图11-18所示。

图11-18

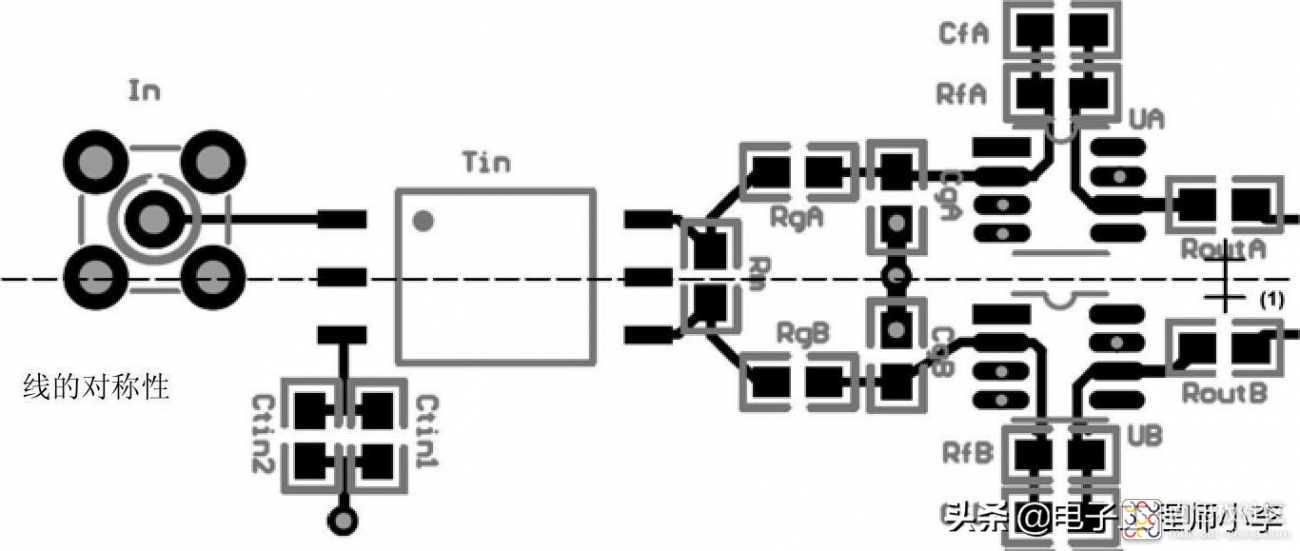

考虑元件对称性的PCB设计实例

对于图11-18的电路,考虑元件对称性的PCB设计实例如图11-19所示。图11-19中的元件按照元件对称策略排列。对称中线被定义为穿过变压器(Tin)中央的直线。输出电阻R OUTA 和R OUTB 基于对称中线等距分布。尽管这种布局看上去使人赏心悦目,但仔细分析,可以看到它仍然对放大器引脚输出的信号路径产生了一定的影响。例如,在SOIC-8封装的运算放大器中,输出引脚通常在引脚端6,因此,UA的引脚端6到中心的距离与UB的不同。这种差异必须通过加长某一信号路径的方式来补偿。如图11-19中右边的虚线所示,路径A与路径B存在不匹配的情况。

图11-19 考虑元件对称性的PCB设计实例

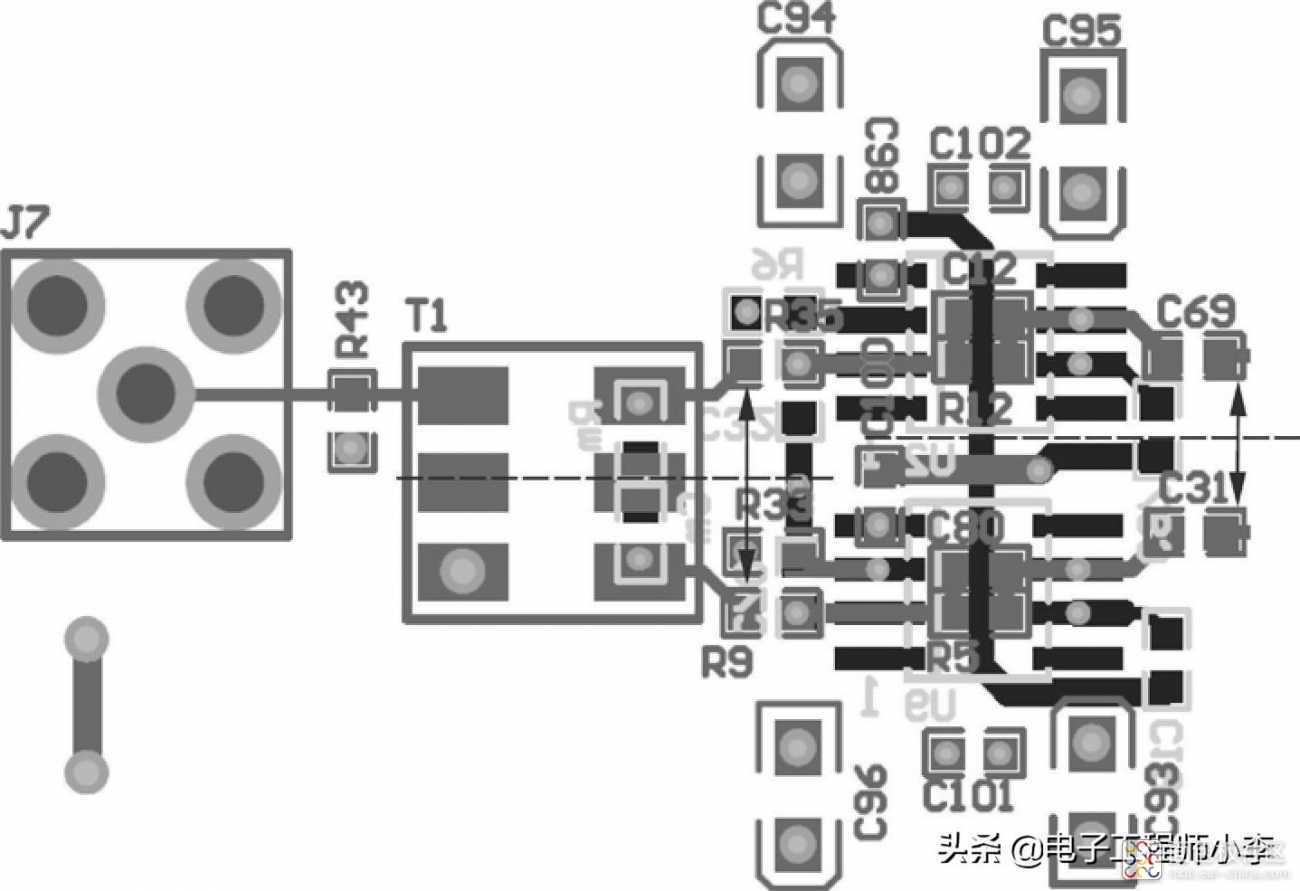

考虑信号路径对称的PCB设计实例

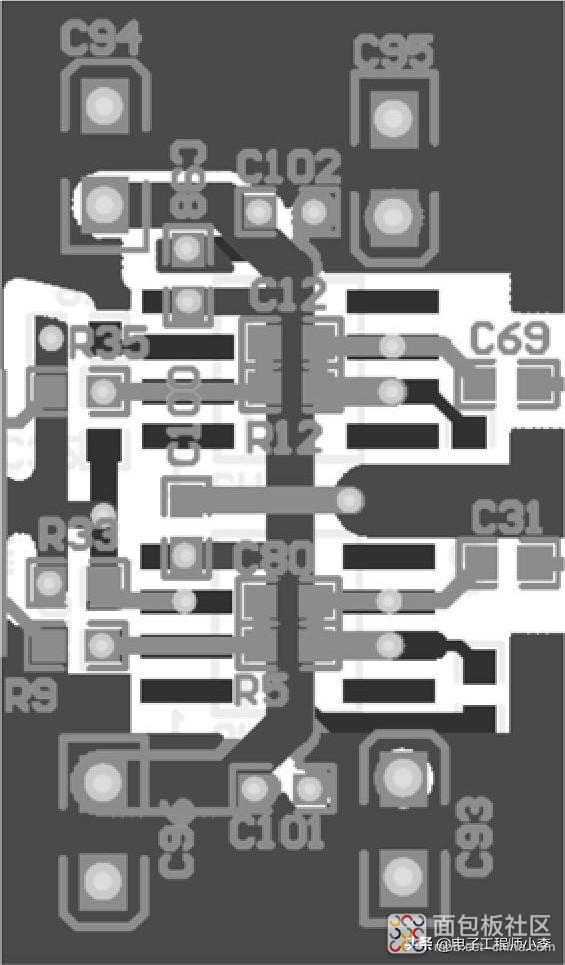

考虑信号路径对称的PCB设计实例如图11-20所示,注意图中无论是顶层路径还是底层路径,从焊盘到焊盘的路径长度都是相等的。

图11-20 考虑信号路径对称的PCB设计实例

图11-20中有两条不同的对称中线:一条是驱动器输入的对称线;另一条是驱动器输出的对称线。SOIC-8封装是与输入中线对称的,这个PCB布局消除了图11-19中所示的信号路径不匹配情况。

图11-20所示的PCB布局选择了0603尺寸的元件来取代1206尺寸的元件,与图11-19所示的PCB布局相比更加紧凑。由于使用0603尺寸的元件,使得反馈元件R FA ,C FA ,R FB 和C FB (分别对应于图11-20中的R 12 , C 12 , R 5 和C 80 )可以分布在PCB的一侧,运算放大器可以直接放在另一侧,从而消除了运算放大器的同相输入端(SOIC-8的引脚端3)与反馈元件焊盘有可能产生的过孔和寄生耦合。同时,元件的尺寸小也能够减少输出路径到反相输入端的长度,从而消除图11-19中虚线所示的不匹配情况。

运算放大器

的电源去耦

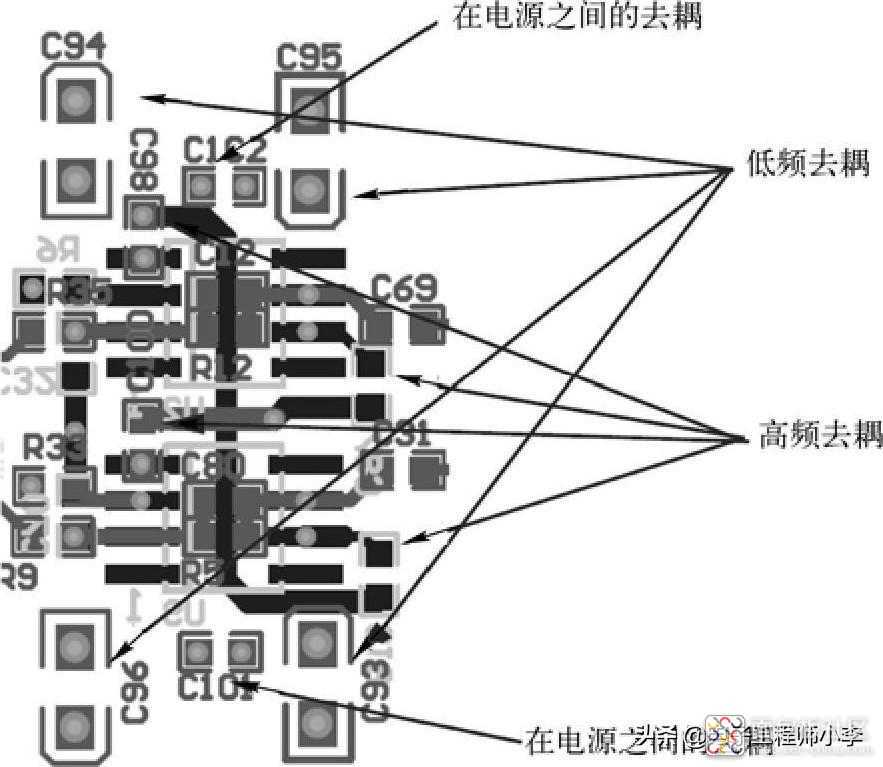

运算放大器对电源去耦的要求很高。一些文献中通常建议在每个电源引脚端加上两个电容:一个是高频电容(0.1μF),直接连接(或者距离运算放大器电源引脚端小于0.25′);另一个是低频电容(2.2~6.8μF),这个容量较大的去耦电容在低频段有效,它可以离运算放大器稍微远一点。注意,在PCB上的相同区域附近的几个元件,可以共用一个低频去耦电容。除了这些电容外,第三个更小的电容(10nF)也可以加到这些电源引脚端上,这个额外的电容有益于减少二次谐波失真。

运算放大器的电源去耦电容的位置如图11-21所示。图11-21中的C 93 ,C 94 ,C 95 和C 96 是较大的电容;C18,C97,C98和C100是高频电容;C101和C102则是电源间去耦合电容。去耦合电容C 97 ,C 98 ,C 18 和C 100 采用星形接地方式。这种接地连接方式可以消除某些由于放大器产生而传到共地端的失真。

图11-21 运算放大器的电源去耦电容的位置

接地层

无论怎么强调消除失真,或者说防止失真干扰到地线的重要性都不为过。然而,失真干扰几乎总是会到达地线(不是在这个点就是在那个点),然后再传播到电路板的其他部分上。

理想的情况是在电路板上只有一个接地层,然而这个目标并非总能实现。当电路中必须添加地线层时,最好采用“安静的地”设计形式。这种设计采用一个地线层作为基准(参考)接地层,基准接地层与“安静的地”仅用在一点(仅在一点)连接。

例如,图11-22中所示的一个4层电路板,其顶层和底层用来作为信号层,而中间的两层用来接地,其中一个为基准地线层,另一个为“安静的地”。

图11-22 接地层和“安静的地”

将运算放大器下面的地线层和电源层开槽(开路),可以防止寄生电容耦合将不需要的信号反馈到同相输入端。在图11-23中,两个运算放大器下面的地线层是开槽的。注意,不仅运算放大器下面的地线层被开槽了,开槽还延伸到所有与运算放大器直接相连的焊盘。另外,如果一个焊盘需要接地,则这条线路的宽度至少要大于50mils(0.050in),才能将寄生电阻和电感减到最小。

图11-23 地线层的开槽

电源线布线

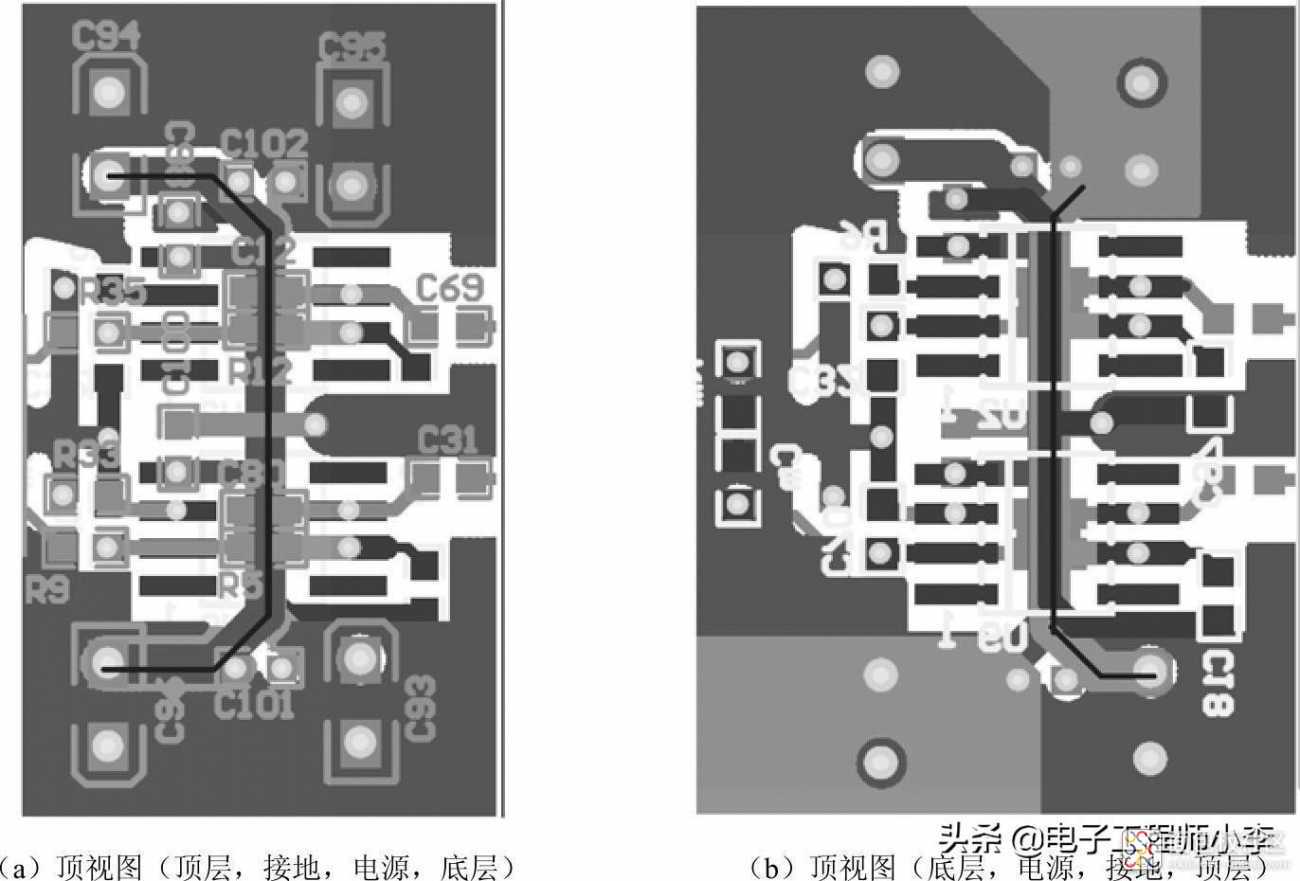

如图11-24所示,对于采用SOIC-8封装的运算放大器而言,其正负电源线路通过内层互跨,可以实现在不与任何信号路径交叉的情况下为两个运算放大器供电。这两条线路在图11-24(a)和图11-24(b)中分别用黑线标示了出来[图11-24(a)与图11-24(b)的图层顺序相反,均为顶视图]。这种设计将PCB的层数量减少到4层。

图11-24

/5

/5