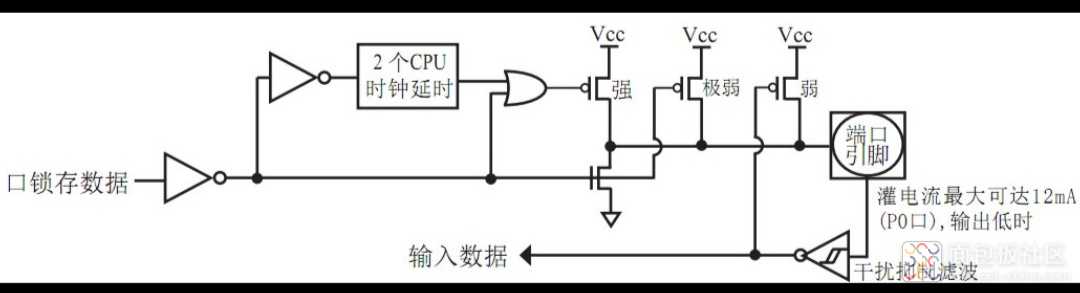

按照这张图片分析,上面电路时输出,下面电路是输入,是这样的准双向输入输出端口。

端口输出时,假设是高电平,经过两个非门和两个CPU信号延迟到达或门,这里为什么要用到两个CPU时钟信号延迟?经过或门输出还是高电平,此时一路输出信号分出两路分别驱动两个MOS管导通,输出是高电平。同理可输出为低电平,不知道我的理解是否正确?

如果配置为端口输入状态,那么是下面这个输入电路,下面这个应该比较简单,就一个施密特触发器翻转电平,有一定的消抖能力。假设外部输入为高电平,经施密特触发器为低电平,但是这个施密特触发器后级接的这个MOS管有什么作用,弱是什么意思?

/5

/5