一、主要特点

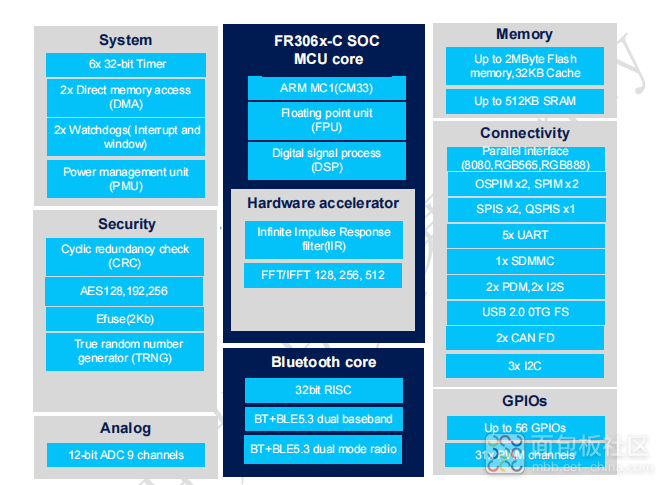

- 内置蓝牙模块:FR306x-C系列芯片内置了蓝牙BR/EDR/BLE的收发器和控制器,符合蓝牙V5.3标准,支持多种模式如BR 1Mbps GFSK、EDR 2Mbps π/4-DQPSK、3Mbps 8DPSK以及BLE1M/2Mbps GFSK、125K/500K等。这种设计使得FR306x-C系列芯片能够轻松实现蓝牙多主多从多连接,非常适合需要无线通信的应用场景。

- CAN FD总线控制器:FR306x-C系列芯片内置了最多2个独立的CAN FD控制器,向下兼容CAN2.0 A/B部分。这使得FR306x-C系列芯片在工业和汽车电子等领域具有广泛的应用前景,如汽车安全系统、无钥匙进入、无线电池管理等。

- 高性能内核:该系列芯片搭载了高性能的CM33 ARM内核,最高主频可达156MHz,以及一个主频为48MHz的蓝牙协处理器。这种组合为FR306x-C系列芯片提供了强大的处理能力,能够满足各种复杂应用的需求。

二、应用领域

- 汽车电子:FR306x-C系列芯片的高性能和低功耗特性使其成为汽车电子领域的理想选择。它可以应用于汽车安全系统、无钥匙进入、无线电池管理等方面,提高汽车的智能化和安全性。

- 工业领域:在工业领域,FR306x-C系列芯片同样表现出色。它可以应用于监控系统、智能楼宇、门禁等场景,实现远程监控和控制,提高工业生产的效率和安全性。

三、开发支持

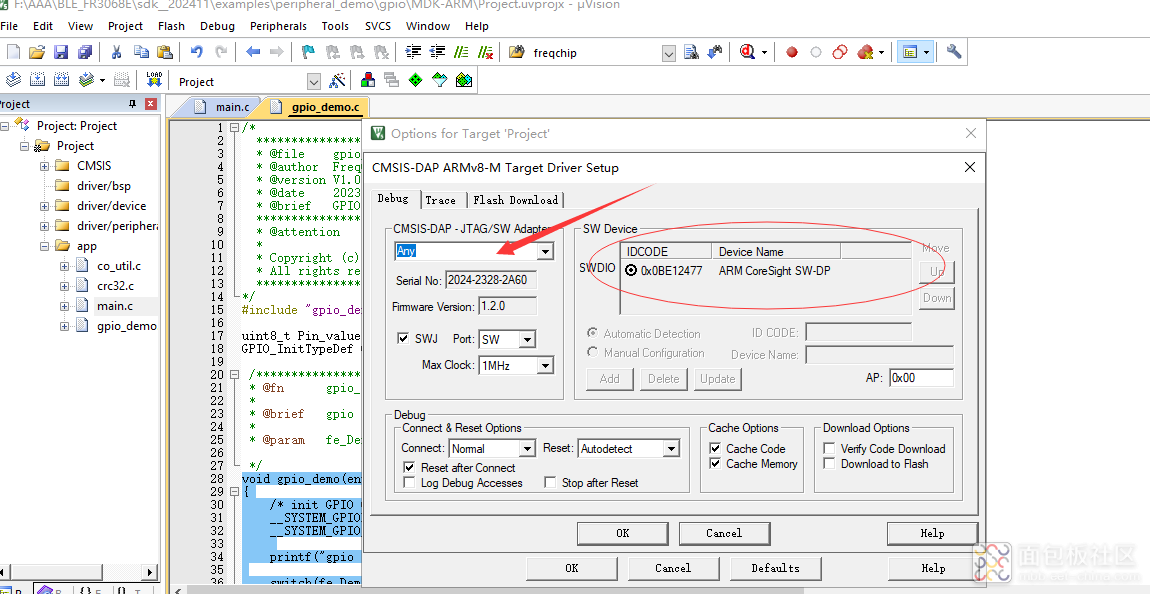

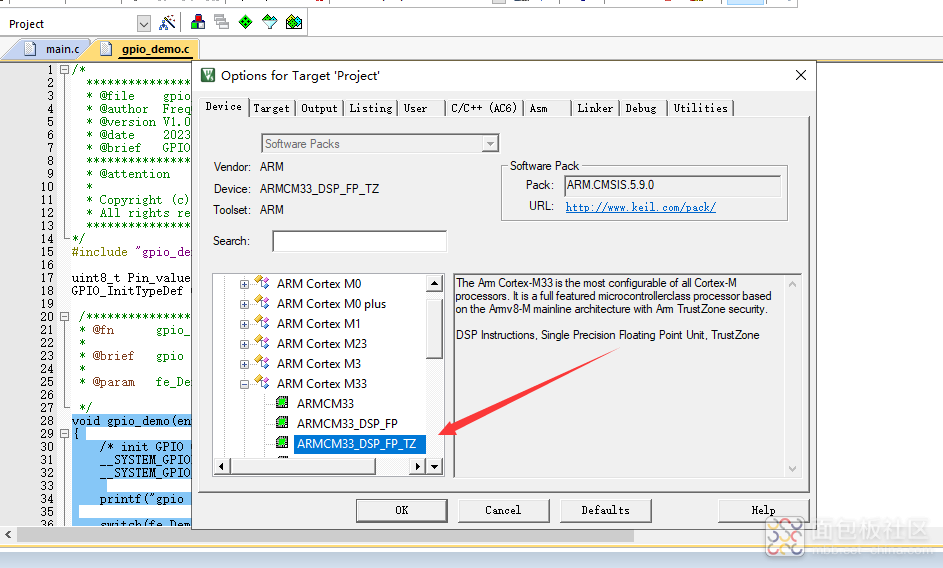

- 官方工具和示例程序:FR306x-C系列芯片的官方提供了全套的开发工具和示例程序,使得开发者能够更快速、更方便地进行项目开发。这些工具和示例程序涵盖了从硬件初始化到应用程序开发的各个环节,大大降低了开发难度。

- 技术支持:FR306x-C系列芯片的制造商还提供了专业的技术支持服务,包括在线咨询、技术支持文档等。这些服务能够帮助开发者解决在开发过程中遇到的问题,提高开发效率。

四、开发体验

从开发者的角度来看,FR306x-C系列芯片提供了良好的开发体验。首先,其内置的蓝牙模块和CAN FD总线控制器使得开发者能够更轻松地实现无线通信和总线通信功能。其次,官方提供的开发工具和示例程序大大降低了开发难度和成本。最后,制造商提供的技术支持服务也为开发者提供了有力的保障。FR3068E-C芯片架构属于双核架构,包括一颗独立的蓝牙核做蓝牙通讯以及另外一颗主核MCU,双核之间通过串口做HCI通讯,蓝牙核一般不对外开放,用户无需关注。

FR3068E-C SDK是基于Freertos的系统框架,配合丰富的中断响应来实现整个代码的运行;SDK文件结构包含了MCU外设驱动,应用层的例程代码,都是以源码的形式提供;蓝牙 host部分以库的形式提供,同时提供了specification手册、公共组件、第三方软件、工具文件;内置了多种功能模块,如FlashDB存储模块、crc32算法、fatfs文件系统等等。

GPIO mian

<pre>

int fputc(int ch, FILE *stream)

{

while(__UART_IS_TxFIFO_FULL(UART3));

__UART_WRITE_FIFO(UART3, ch);

return ch;

}

/*********************************************************************

* @fn system_clock_config

*

* @brief System Misc Init.

*/

void system_clock_config(void)

{

System_ClkConfig_t ClkConfig;

/* CORE HSCLK Config */

ClkConfig.CORE_HSCLK_CFG.CORE_HSCLK_Source = CORE_HSCLK_SEL_HES;

/* PLL clock = HSE_VALUE*N + (HSE_VALUE/65535)*M */

/* SPLL CLK Config */

ClkConfig.SPLL_CFG.PowerEn = PLL_POWER_ENABLE;

ClkConfig.SPLL_CFG.PLL_N = 8;

ClkConfig.SPLL_CFG.PLL_M = 0;

/* PLL clock = HSE_VALUE*N + (HSE_VALUE/65535)*M */

/* AUPLL CLK Config */

ClkConfig.AUPLL_CFG.PowerEn = PLL_POWER_DISABLE;

ClkConfig.AUPLL_CFG.PLL_N = 8;

ClkConfig.AUPLL_CFG.PLL_K = 0;

ClkConfig.AUPLL_CFG.PLL_D = 0;

System_CORE_HSCLK_config(&ClkConfig.CORE_HSCLK_CFG);

if (System_SPLL_config(&ClkConfig.SPLL_CFG,200) == -1)

while(1);

if (System_AUPLL_config(&ClkConfig.AUPLL_CFG,200) == -1)

while(1);

ClkConfig.MCU_Clock_Source = MCU_CLK_SEL_CORE_HSCLK;

ClkConfig.SOC_DIV = 1; /* This parameter is valid when MCU_Clock_Source == MCU_CLK_SEL_SPLL_CLK */

ClkConfig.MCU_DIV = 1;

ClkConfig.APB0_DIV = 1;

ClkConfig.APB1_DIV = 1;

ClkConfig.APB2_DIV = 1;

System_MCU_clock_Config(&ClkConfig);

}

UART_HandleTypeDef Uart3_handle;

int main(void)

{

GPIO_InitTypeDef GPIO_Handle;

pmu_init();

system_clock_config();

/* Uart3 IO init */

GPIO_Handle.Pin = GPIO_PIN_4|GPIO_PIN_5;

GPIO_Handle.Mode = GPIO_MODE_AF_PP;

GPIO_Handle.Pull = GPIO_PULLUP;

GPIO_Handle.Alternate = GPIO_FUNCTION_1;

gpio_init(GPIOB, &GPIO_Handle);

__SYSTEM_UART_CLK_SELECT_COREH();

Uart3_handle.UARTx = UART3;

Uart3_handle.Init.BaudRate = 115200;

Uart3_handle.Init.DataLength = UART_DATA_LENGTH_8BIT;

Uart3_handle.Init.StopBits = UART_STOPBITS_1;

Uart3_handle.Init.Parity = UART_PARITY_NONE;

Uart3_handle.Init.FIFO_Mode = UART_FIFO_ENABLE;

uart_init(&Uart3_handle);

printf("SystemCoreClock:%d\r\n", system_get_CoreClock());

printf("SystemDSPClock:%d\r\n", system_get_DSPClock());

printf("System_CORE_HSCLK:%d\r\n", system_get_CORE_HSCLK());

printf("System_SPLLCLK:%d\r\n", system_get_SPLLCLK());

printf("System_AUPLLCLK:%d\r\n", system_get_AUPLLCLK());

gpio_demo(GOIO_OUTPUT);

while(1);

}

</pre>

复制代码void gpio_demo(enum_GPIO_Demo_t fe_Demo)

{

{

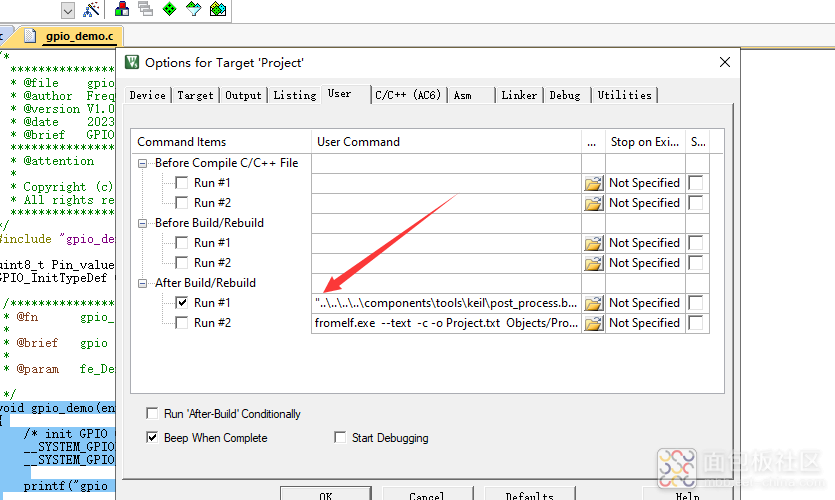

"..\..\..\..\components\tools\keil\post_process.bat" "@L" "#L" "$J"

点灯OK

/4

/4