21 世纪是信息的时代,各种电子技术都迅雷不及掩耳的速度更新发展,电脑、手机、DV 等已成为当代生活不可缺少的一部分,这些电子产品的功能日渐增多,性能越来越好,价格却有减无增,探究其原因,集成电路制造技术的发展和电子设计技术的提高是两大主流因素,集成电路制造技术以微细加工为主,电子设计技术以EDA 技术为核心。

EDA 技术已成为当今电子技术发展的前沿之一,这是在各技术较先进的国家的共同努力下取得的成果,CPLD、FPGA 可编程逻辑器件的应用,无疑为电子设计带来了极大的灵活性和适用性。

一. EDA 技术的概念与特征

1.1 概念

EDA 技术即是电子设计自动化技术,它由PLD 技术发展而来,可编程逻辑器件PLD 的应用与集成规模的扩大为数字系统的设计带来了极大的方便和灵活性,变革了传统的数字系统设计理念、过程、方法。通过对PLD 技术不断地改进提高,EDA 技术应运而生。

EDA 技术就是基于大规模可编程器件的,以计算机为工具,根据硬件描述语言HDL 完成表达,实现对逻辑的编译化简、分割、布局、优化等目标的一门新技术,借助EDA 技术,操作者可以通过利用软件来实现对硬件功能的一个描述,之后利用FPGA/CPLD 才可得到最终设计结果。

1.2 特征——全新的设计方法:自顶向下

传统的电子设计方法一般多是“自底向上”的,通俗来说就是在确定标准的通用的集成电路芯片之后,再行模块设计,最终完成系统设计。这种设计长期以来存在着难以克服的缺陷,效率不高,容易出故障,所需元器件太多,消耗大……

EDA 技术是对传统电子设计方法的一种突破与变革,它的设计是“自顶向下”的,也即以系统设计为切入点,在设计之时就做好功能方框图的划分并完成各部分结构的规划,在方框图划分阶段完成仿真、纠错工作,同时借助HDL 完成对高层次系统的逻辑描述,经验证后,借助综合的优化工具完成电子设计,借助EDA 技术,操作者可以通过利用软件来实现对硬件功能的一个描述,之后利用FPGA/CPLD 才可得到最终设计结果。 这样,我们可以发现,不论是仿真还是调试都是在初期在一个高层次上就完成了的,如此,既有助于及时发现结构设计上可能出现的错误,减少设计工作中的失误,同时有效地提高了电子设计工作效率和成功率。

1.3 独特的描述语言:硬件描述语言

EDA 技术以硬件描述语言HDL 为系统逻辑描述的主要表达方式,那么什么是硬件描述语言?

它是相对于一般的计算机语言如C、Pascsl 来说的,多应用于设计硬件电子系统,也属计算机语言,它描述电子系统的逻辑功能、电路功能和连接方式。ABEL-HDL 和VHDL 是现今应用比较广泛的两种硬件描述语言,后者较前者应用更多。

ABEL 可以支持各种方式的输入,所谓的输入方式就是指电路系统设计的表达方式,包括真值表、状态图。它的描述具有很强的独立性,与此同时,从宽口径到系统它都能完成描述,因而可以适应不同规模的编程设计,利用标准格式设计还 可以转换设计环境,对比VHDL 来说,它的适用面要宽许多,使用操作灵活简单,要求也要宽松,易于速成。

1.4 典型的设计

ASIC 现在电子产品更新极快,复杂度也在不断提高,有时候一个看起来比较简单电子系统它的组成也许是数万的中小规模集成电路,这样就使电子系统经常遭遇耗能高、可靠性低等问题的挑战。ASIC 芯片是对此问题进行改善的一个有效途径。 它包涵了FPGA 和CPLD 器件,FPGA/CPLD 是实现EDA 的基础,也是EDA 思想的最终表述手段,属于高密度的可编程逻辑器件,一般像样品的研制或者是批量不大的产品开发它们都能适用,并且极大的缩短设计周期,削减开销,避免风险,使产品能够尽快上市。

FPGA 和CPLD 的结构有所不同,前者是标准的门阵列,而后者是与或阵列,但是二者的集成度及易用性都颇为相似,因而可以并驾齐驱。当然二者也有各自的特点,其差异表现在以下几个方面:

(1)颗粒粗细不同。与CPLD 相比,FPGA 的颗粒相对细一些,它的一个颗粒只是逻辑宏单元,而CPLD 的则是逻辑宏块。二. EDA技术在电子设计中的应用

(2)适用结构不同。FPGA 更适合应用于触发器相对丰富的结构之中,CPLD 比较适合应用于触发器有限但是积项特别丰富的结构之中。

(3)编程方式不同。FPGA 在逻辑门下就可以实现编程,多采用改变内部布线的方式,具备很强的灵活性。GPLD 只有在逻辑快下才可实现变成,多采用修改已经固定了的内连电路的逻辑功能的方式,速度更快。

(4)功能消耗不同。FPGA 消耗小,CPLD 消耗比较而言大一些。

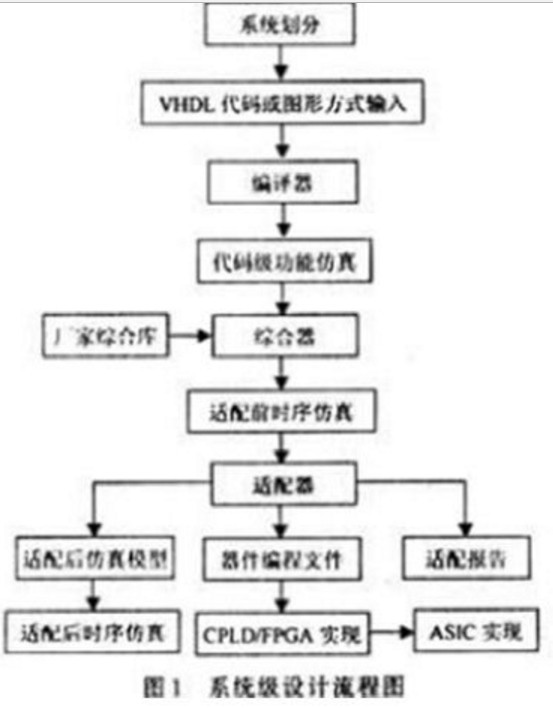

EDA 技术属于一种层次比较高的电子设计方式,也可以称作系统级设计方法,它以概念来驱动,电子设计工作者并不需要利用门级原理图,只是针对确定了的设计目标就可以实现对电路的描述,这样一来,就少了电路细节的约束和限制,使设计可以更多的放开从而更具创造性,待设计人员有了概念构思之后,再讲高层次描述输入到计算机中去,EDA 系统在规则驱动下就会自动完成整个电子的设计。如此,新的概念就可以在段时间中就成为产品,基于EDA 技术的电子设计流程如图1 所示:

可以看到电子EDA 技术设计的工作流程包括:

系统划分、VHDL 代码或图形的输入、代码级功能仿真、送配前时序仿真、编程下载、ASIC 实现。

电子设计的第一步是借助文本或者是图形编辑工具将设计呈现出来,即实现设计描述。

第二步是借助编译器实施错排编译,也即HDL 程序输入,至于选择那种输入形式并不一定,一般设计的原理图比较直观,所以不难掌握,也不难被接受,并且编辑器中可供利用的单元器件非常多,这时候就给设计者提供了根据自己需要选择表达的方式的机会,倘使是编译文件是VHDL 文件,那么在进行综合之前还要进行的一项重要工作就是仿真,就是把设计原程序送入VHDL仿真器之中,这个仿真过程可以有助于及时发现结构设计上可能出现的错误。

第三步就是综合,沟通软件和硬件设计,待综合后,就可以生成网表,针对网表,可以实施功能仿真,从而保证设计描述严格遵循并符合设计意图,仿真功能实际上只是从逻辑功能上对电子设计进行检测,并不涉及器件的一些硬件方面的特性,例如典型的有延迟特性,一些不甚严格的设计,这一层仿真通常可以省去。

最后一步是编程下载,通过仿真确定设计正确无误后,利用FPGA/CPLD 来完成逻辑映射操作,适配,最后利用JTAG 编程器或者其它下载设计项目到目标器件PFGA 之中,完成系统级设计。

三. 基于EDA 技术的电子设计应注意的事项

第一,考虑到电子电路延时的时间具备不确定性,和部分自动编译可能会为冗余的电路所简化两个因素,将EDA 技术应用于电子设计中时,不宜采用偶数个数的反向器,并以并联的方式将它们连接以构成“延时电路”;

第二,输入引脚不能置于悬空状态,一者要有有源信号来驱动,再者一些不用的引脚必须时刻保持接地;

第三,要切实保证各大器件的电源和地线引脚是始终连接着的,且它们之间有必要进行滤波及去耦;

第四,为了使设计扩展及修改更容易更方便进行,在使用器件的过程中,不管是逻辑单元还是引脚都要有一个多余的量;

第五,环境问题也应警惕,尽可能避免器件过热。 总之,EDA 技术是对传统电子设计技术的一种突破与创新,如果失去了EDA 技术的支持,是不可能顺利完成出大规模集成电路设计制造的,反过来思考,现代集成电路技术发展需求对EDA 技术提出了更高的要求,可以预见,在不久的将来,EDA 技术定会成为电子设计中的主导力量。

来源:网络

/5

/5