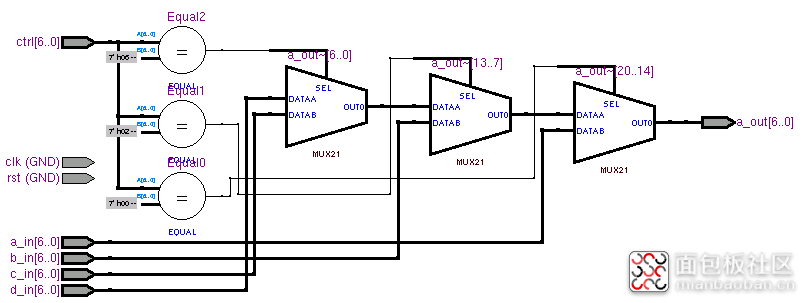

4 case IF-ELSIF or concurrent IFs mux with default value of ‘X’ in 3 writing forms, all have logic according to order of precedence.

a_out <= (others => 'X'); if ctrl = "0000000" then a_out <= a_in; elsif ctrl = "0000010" then a_out <= b_in; elsif ctrl = "0000110" then a_out <= c_in; elsif ctrl = "0001110" then a_out <= d_in; end if; | if ctrl = "0000000" then a_out <= a_in; elsif ctrl = "0000010" then a_out <= b_in; elsif ctrl = "0000110" then a_out <= c_in; elsif ctrl = "0001110" then a_out <= d_in; else a_out <= (others => 'X'); end if; | a_out <= (others => 'X'); if ctrl = "0000000" then a_out <= a_in; end if; if ctrl = "0000010" then a_out <= b_in; end if; if ctrl = "0000110" then a_out <= c_in; end if; if ctrl = "0001110" then a_out <= d_in; end if; * This form gives same RTL except for the order of precedence. In this case, CTRL=0xE will be the strongest assignment. |

ALUTs = 9 | ||

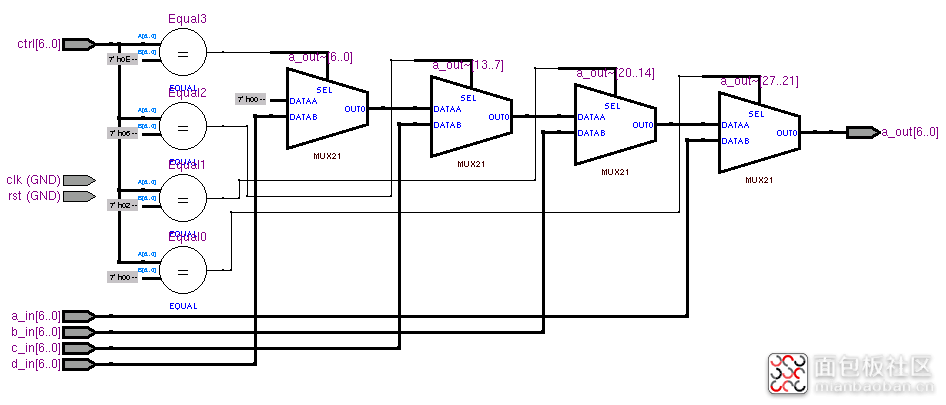

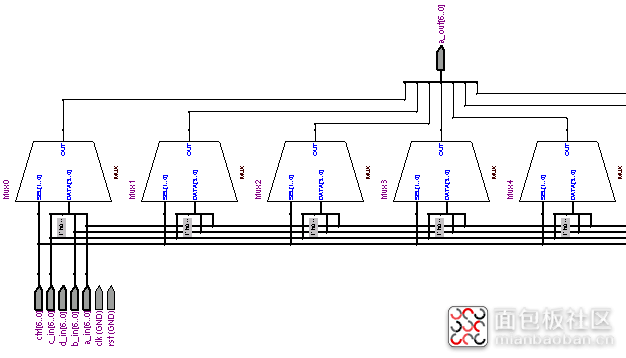

4 case mux with default value of ‘0’ added a logic stage for the (others=>’0’) case

if ctrl = "0000000" then a_out <= a_in; elsif ctrl = "0000010" then a_out <= b_in; elsif ctrl = "0000110" then a_out <= c_in; elsif ctrl = "0001110" then a_out <= d_in; else a_out <= (others => '0'); end if; |

ALUTs = 20 |

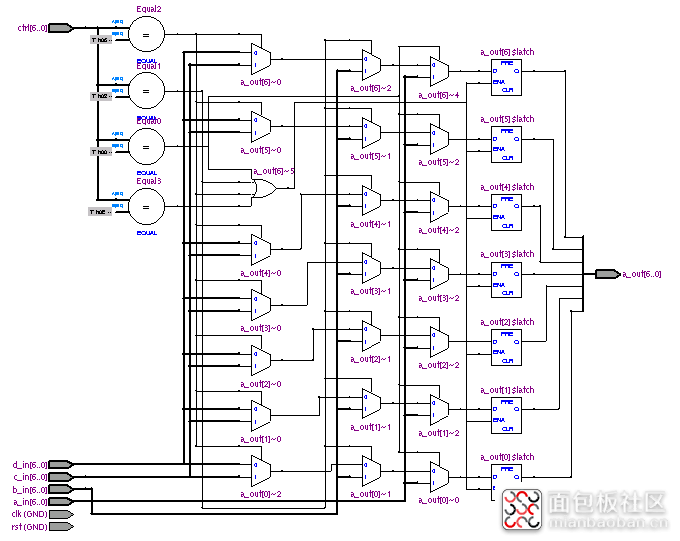

4 case mux with no default value created latches (this is a combinatorial process only)

if ctrl = "0000000" then a_out <= a_in; elsif ctrl = "0000010" then a_out <= b_in; elsif ctrl = "0000110" then a_out <= c_in; elsif ctrl = "0001110" then a_out <= d_in; end if; |

|

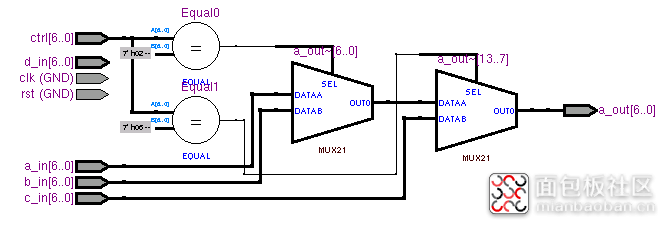

4 case CASE mux with default value of ‘X’ has no precedence order.

case ctrl is when "0000000" => a_out <= a_in; when "0000010" => a_out <= b_in; when "0000110" => a_out <= c_in; when "0001110" => a_out <= d_in; when others => a_out <= (others => 'X'); end case; |

ALUTs = 9 |

4 case CASE mux with no default value created latches.

case ctrl is when "0000000" => a_out <= a_in; when "0000010" => a_out <= b_in; when "0000110" => a_out <= c_in; when "0001110" => a_out <= d_in; when others => null; end case; |

ALUTs = 17 |

4 case CASE mux with default value of ‘0’ added logic.

case ctrl is when "0000000" => a_out <= a_in; when "0000010" => a_out <= b_in; when "0000110" => a_out <= c_in; when "0001110" => a_out <= d_in; when others => a_out <= (others => '0'); end case; |

ALUTs = 18 |

3 case IF mux with default value of ‘X’ gets 8 ALUTs

a_out <= (others => 'X'); if ctrl = "0000000" then a_out <= a_in; end if; if ctrl = "0000010" then a_out <= b_in; end if; if ctrl = "0000110" then a_out <= c_in; end if; |

|

3 case CASE mux with default value of ‘X’ gets 7 ALUTs

case ctrl is when "0000000" => a_out <= a_in; when "0000010" => a_out <= b_in; when "0000110" => a_out <= c_in; when others => a_out <= (others => 'X'); end case; |

*7 muxes *7 muxesALUTs = 7 |

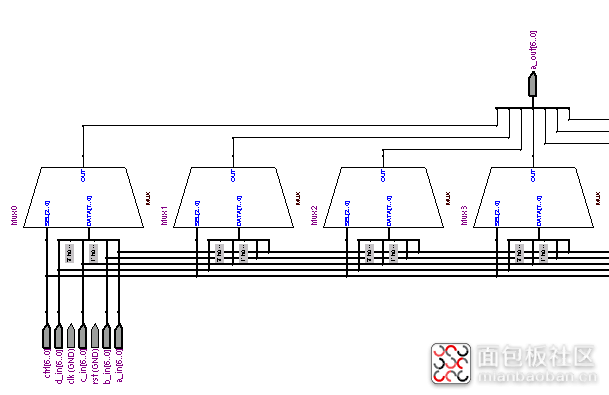

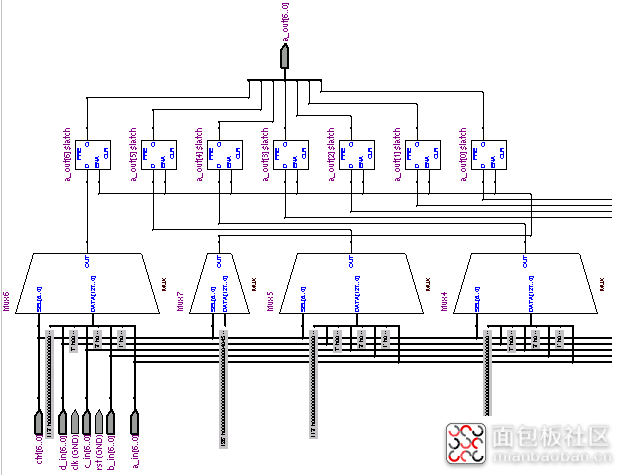

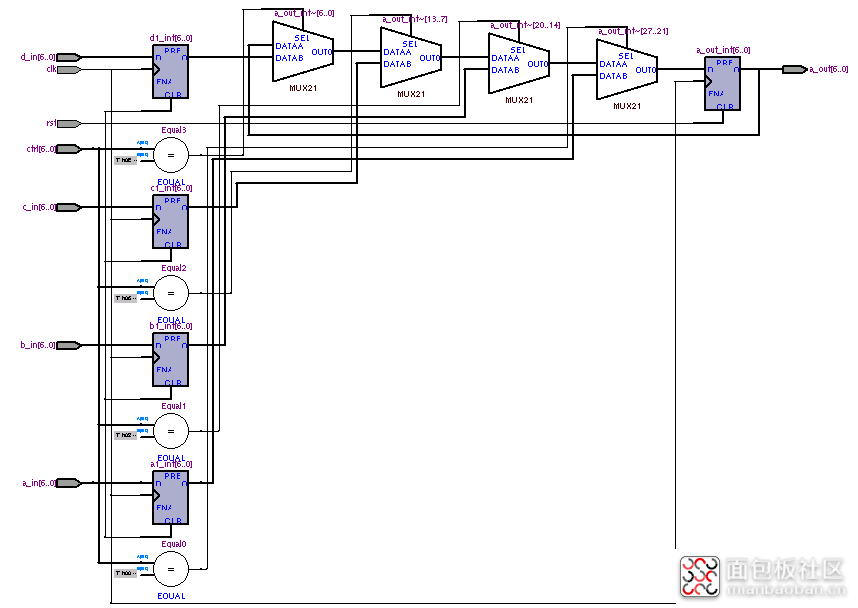

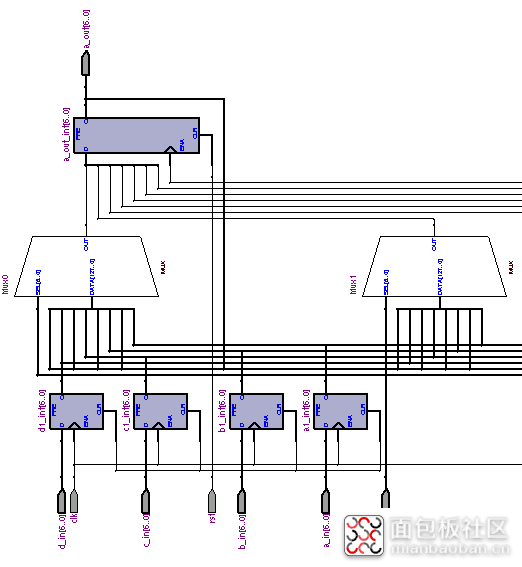

Sequential IF-ELSIF mux

process (clk,rst) begin if rst = '1' then a_out_int <= (others => '0'); a1_int<= (others => '0'); b1_int<= (others => '0'); c1_int<= (others => '0'); d1_int<= (others => '0'); elsif (clk'event and clk = '1') then a1_int<= a_in; b1_int<= b_in; c1_int<= c_in; d1_int<= d_in; if ctrl = "0000000" then a_out_int <= a1_int; elsif ctrl = "0000010" then a_out_int <= b1_int; elsif ctrl = "0000110" then a_out_int <= c1_int; elsif ctrl = "0001110" then a_out_int <= d1_int; -- same with else section -- else -- a_out <= (others => 'X'); end if; end if; end process; a_out <= a_out_int; |

ALUTs = 10 , REGS = 35 Fmax = 1222 Restricted Fmax = 703 |

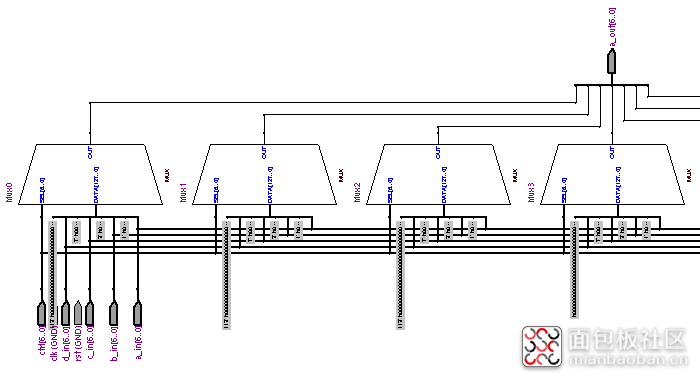

Sequential CASE mux

process (clk,rst) begin if rst = '1' then a_out_int <= (others => '0'); a1_int<= (others => '0'); b1_int<= (others => '0'); c1_int<= (others => '0'); d1_int<= (others => '0'); elsif (clk'event and clk = '1') then a1_int<= a_in; b1_int<= b_in; c1_int<= c_in; d1_int<= d_in; case ctrl is when "0000000" => a_out_int <= a1_int; when "0000010" => a_out_int <= b1_int; when "0000110" => a_out_int <= c1_int; when "0001110" => a_out_int <= d1_int; when others => null; -- same with a_out <= (others => 'X'); end case; end if; end process; a_out <= a_out_int; |

*7 muxes *7 muxesALUTs = 10 , REGS = 35 Fmax = 1105 Restricted Fmax = 703 |

/4

/4