zynq作为一个跨时代的SOC,其FPGA+CPU的组合,解决了在复杂多变的系统需求。那么只要是有CPU的系统肯定就

会涉及到其中断机制。那么在zynq上面,PL部分怎么去中断PS呢,这期,我们通过一个按键中断来给大家演示一下!!

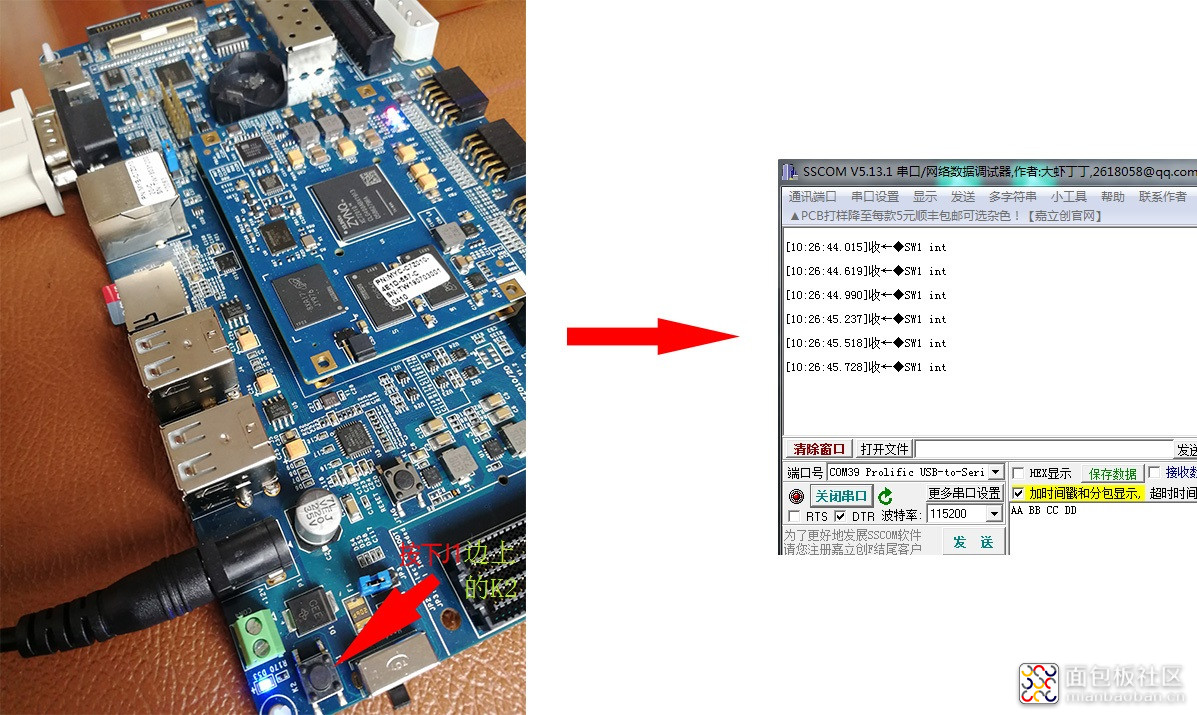

首先,我们来看下实验结果,如图,按下底板上的J1边上的K2,这时串口就会打印SW1 int字样如图,按一次打印一次:

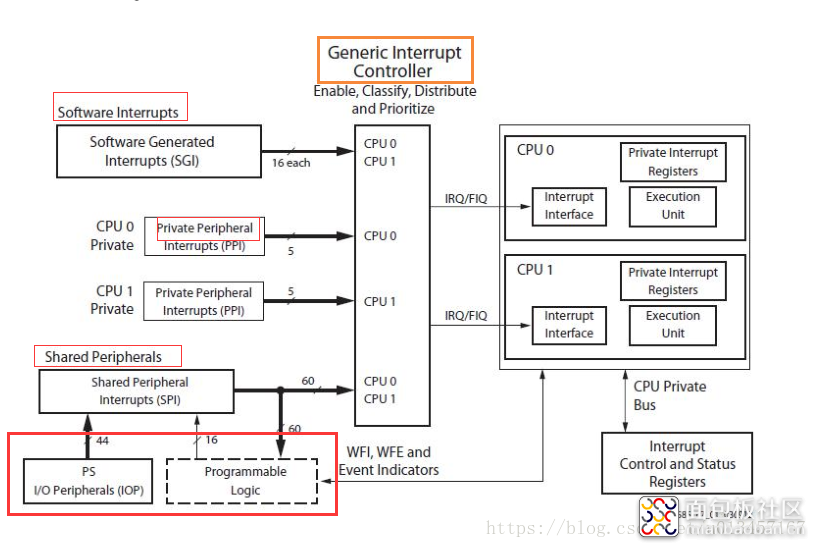

接下来,先说下zynq的PL中断机制,如图,下图是中断控制框图:

这里看到虚框内的PL部分可以通过SPI 这部分,产生中断,最终可以通过ICD灵活分配到两个处理器上。

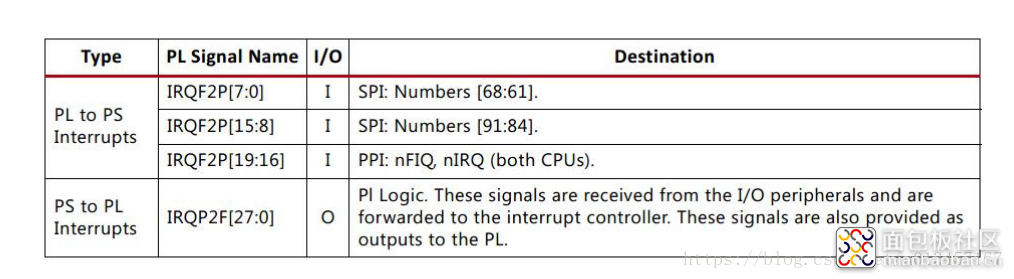

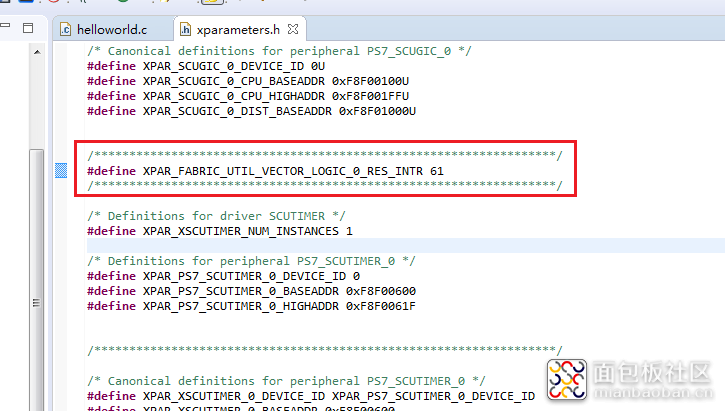

每一个中断源或者一组中断源都对应一个中断ID,处理器运行程序通过ID号来区分是哪个具体中断源产

生的中断。Zynq中共有20个PL到PS的中断。IRQF[15:0]是16个共享外设中断(SPI),可配选择上升沿触

发或高电平触发,中断号为61-68和84-91。

zynq中断可以这么分类,如下:

1.软件中断(SGI,Software generatedinterrupts,中断号0-15)(16–26 reserved) :被路由到一个或者两个CPU上,通过写ICDSGIR寄存器产生SGI.

2.私有外设中断(PPI,private peripheralinterrupts ,中断号27-31):每个CPU都有一组PPI,包括全局定时器、私有看门狗定时器、私有定时器和来自PL的FIQ/IRQ.

3.共享外设中断(SPI,shared peripheralinterrupts,中断号32-95):由PS和PL上的各种I/O控制器和存储器控制器产生,这些中断信号被路由到相应的CPU.

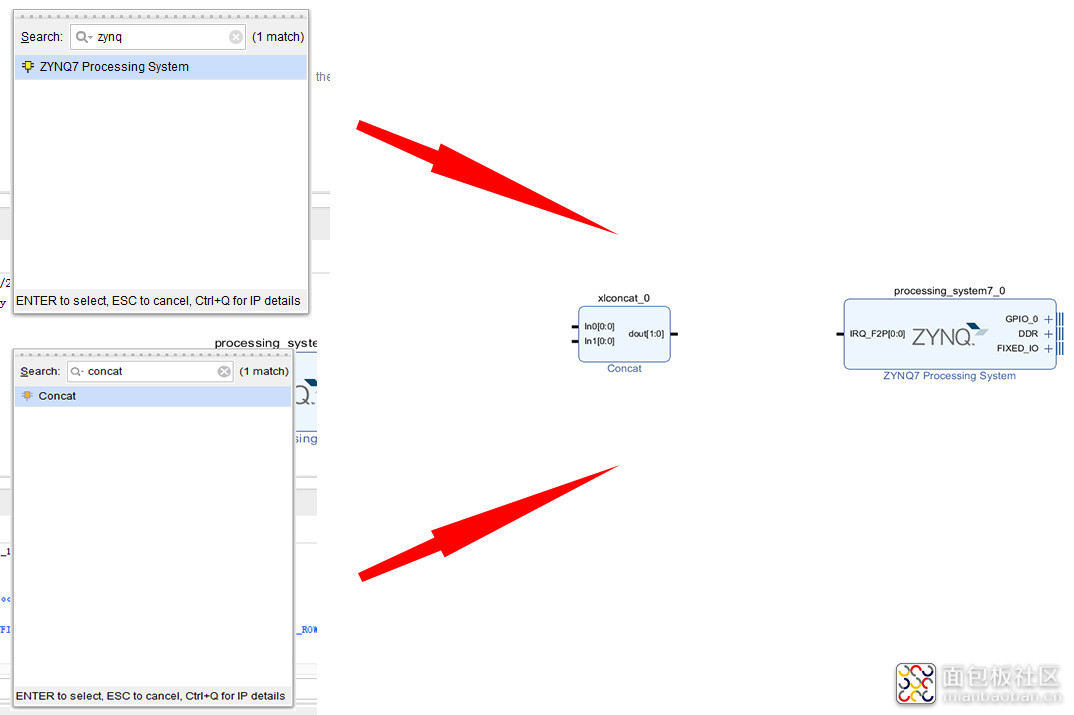

对一些基本概念了解过后,现在我们就开始搭建过程,之前新建工程的步骤这边就不在赘述了,从添加IP开始,先添加zynq

内核,再添加concat IP,添加完成后,两个IP就会出现在IP block里面如下图:

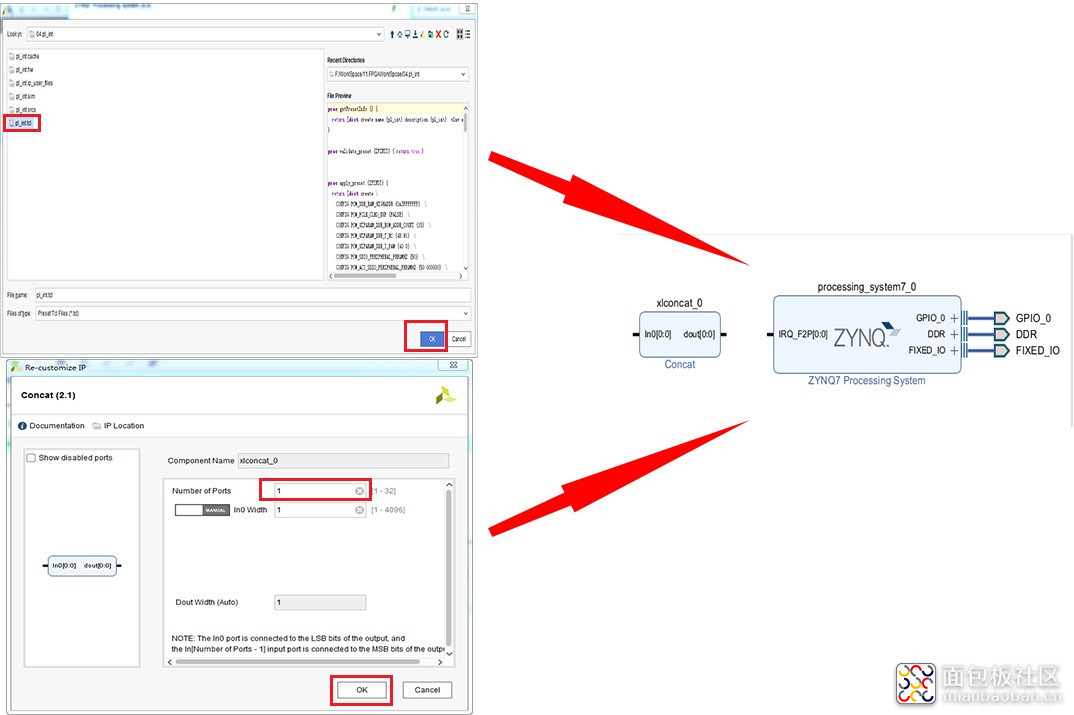

添加好IP好,我们要对IP进行一些配置,先配置zynq内核,双击zynq block,然后倒入demo程序提供的tcl文件。双击concat block把端口设置成1,如图:

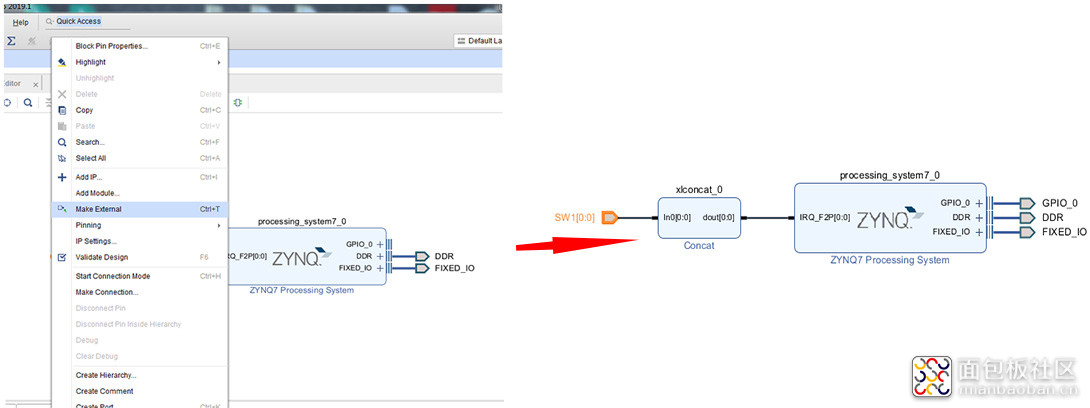

ip配置完成以后,把两个IP连接起来,并且还要设置一个port,我们设置为SW1,右击concat block上的In0,选择Make external,如图:

OK至此,我们可以生成综合文件以及生成FPGA顶层文件了,具体步骤不赘述了,在生成bit文件之前,还要对SW1的硬件关键进行约束,那么

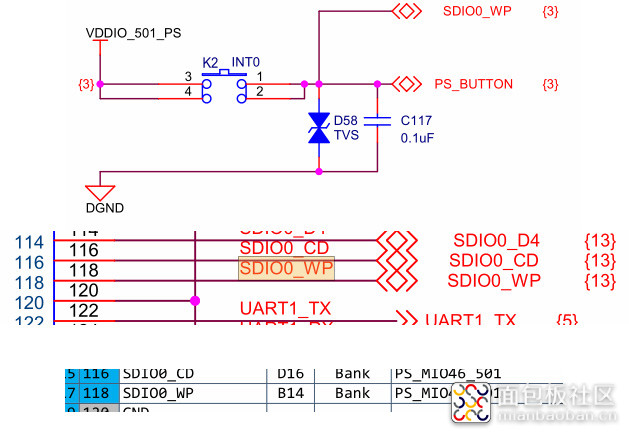

我们要先看看原理图上SW1连接的是哪个管脚,我们通过原理图可以看到B14就是连接K2的管脚,如图,

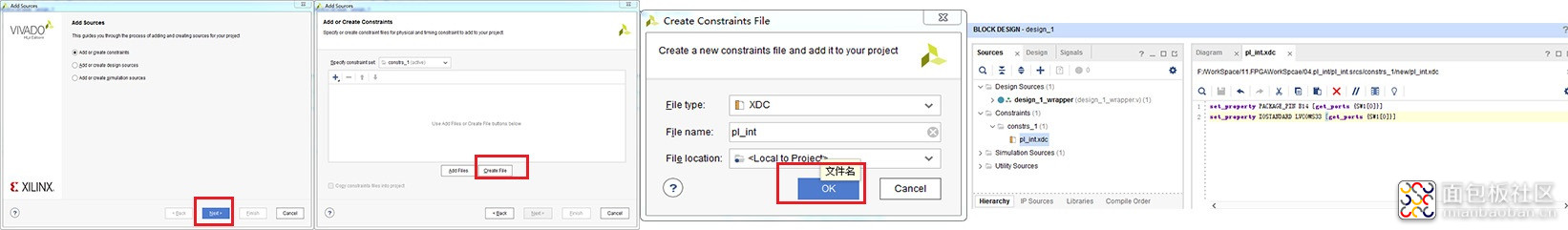

添加管脚约束,如图,

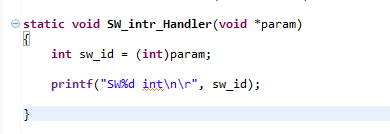

接下来启动SDK,我们看下中断函数,如图,这个函数就是CPU进中断后要干什么,这里是打印一串字符,如文章开头所示

除此以外,我们还要在xparameters.h文件中,添加中断号为61,这个文件在fsbl_bsp/include文件夹里,

嘿嘿,完成,最终实验结果如文章开头所示。

***************************************完美分割线***************************************

【MYD-C7Z010/20开发板 试用体验】惊鸿一瞥,便爱上!

【MYD-C7Z010/20开发板 试用体验】核心板以及底板资源介绍

【MYD-C7Z010/20开发板 试用体验】上电问声好,hello world工程搭建实现

MYD-C7Z010/20购买链接

/2

/2