《MYiR Zynq FPGA 使用手册》中介绍了11个实验的详细操作步骤,如果您仔细阅读过,就不难发现该使用手册层次清晰,由简单到复杂,由面面俱到到重点点拨。总体来描述一个Vivado工程从创建工程到生成BIN文件,步骤有:

①新建一个Vivado工程 → ②新建Block Design → ③添加IP核并配置 → ④生成综合文件 → ⑤生成FPGA顶层文件 → ⑥生成bit文件 → ⑦导出硬件配置文件 → ⑧启动SDK,新建fsbl → ⑨新建一个hello_world工程 → ⑩生成BOOT.bin文件

由于笔记本的HDMI不支持输入,加之没有相适应的LCD屏,因此只验证了六个工程实验,感觉收获颇丰。

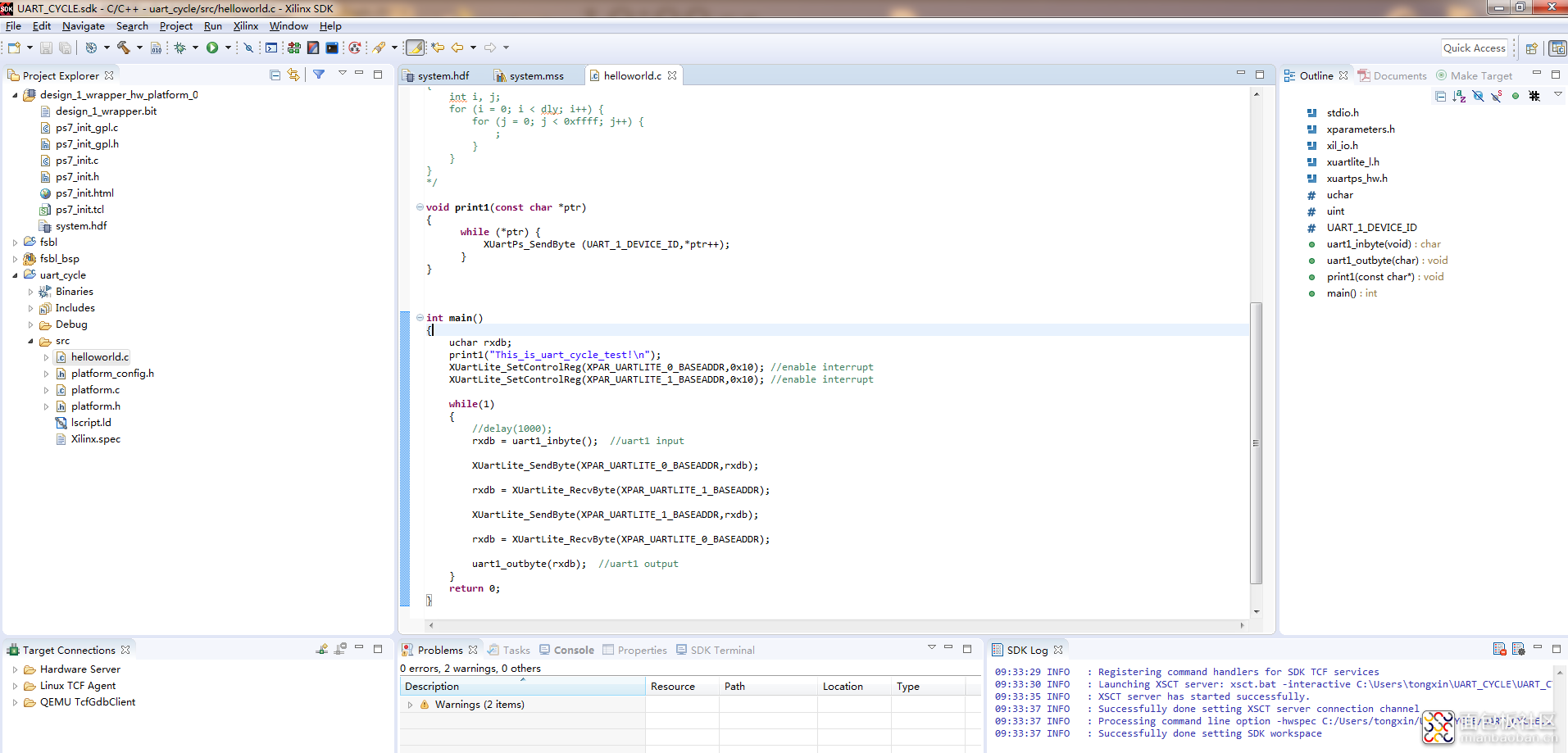

在《MYiR Zynq FPGA 使用手册》中,当然也是存在诸多问题点的,比方说小标题,第五章的1.10写成了1.8,第十章、第十一章出现两个1.8。内容上也存在些许问题,第五章的pl_int中concat核输入管脚SW1连线是否必须改成Op1_0_1,没做说明;第五章的1.5添加xdc管脚约束没有详细说明需要添加三个管脚,导致1.6生成bit文件时编辑pl_int.xdc文件让开发人员一头雾水,怎么多出了SW2,SW3呢。总共做了6个实验的验证,除了第三章的uart_cycle测试结果与手册上描述的不一致外,其它实验结果都与手册描述不谋而合。关于第三章的uart_cycle的实验,米尔提供的uart_cycle工程程序如下:

/* ------------------------------------------------------------ *//* Include File Definitions */ /* ------------------------------------------------------------ */ #include <stdio.h> #include "xparameters.h" //The hardware configuration describing constants #include "xil_io.h" //Contains the Xil_Out32 and Xil_In32 functions #include "xuartlite_l.h" // #include "xuartps_hw.h" #define uchar unsigned char #define uint unsigned short /* ------------------------------------------------------------ */ /* main function */ /* ------------------------------------------------------------ */ #define UART_1_DEVICE_ID 0xE0001000 char uart1_inbyte(void) { return XUartPs_RecvByte(UART_1_DEVICE_ID); } void uart1_outbyte(char c) { XUartPs_SendByte(UART_1_DEVICE_ID, c); } /* static void delay(int dly) { int i, j; for (i = 0; i < dly; i++) { for (j = 0; j < 0xffff; j++) { ; } } } */ void print1(const char *ptr) { while (*ptr) { XUartPs_SendByte (UART_1_DEVICE_ID,*ptr++); } } int main() { uchar rxdb; print1("hellowolrd!\n"); XUartLite_SetControlReg(XPAR_UARTLITE_0_BASEADDR,0x10); //enable interrupt XUartLite_SetControlReg(XPAR_UARTLITE_1_BASEADDR,0x10); //enable interrupt while(1) { //delay(1000); rxdb = uart1_inbyte(); XUartLite_SendByte(XPAR_UARTLITE_0_BASEADDR,rxdb); rxdb = XUartLite_RecvByte(XPAR_UARTLITE_1_BASEADDR); XUartLite_SendByte(XPAR_UARTLITE_1_BASEADDR,rxdb); rxdb = XUartLite_RecvByte(XPAR_UARTLITE_0_BASEADDR); uart1_outbyte(rxdb); } return 0; }

复制代码第一章通过串口打印输出字符信息

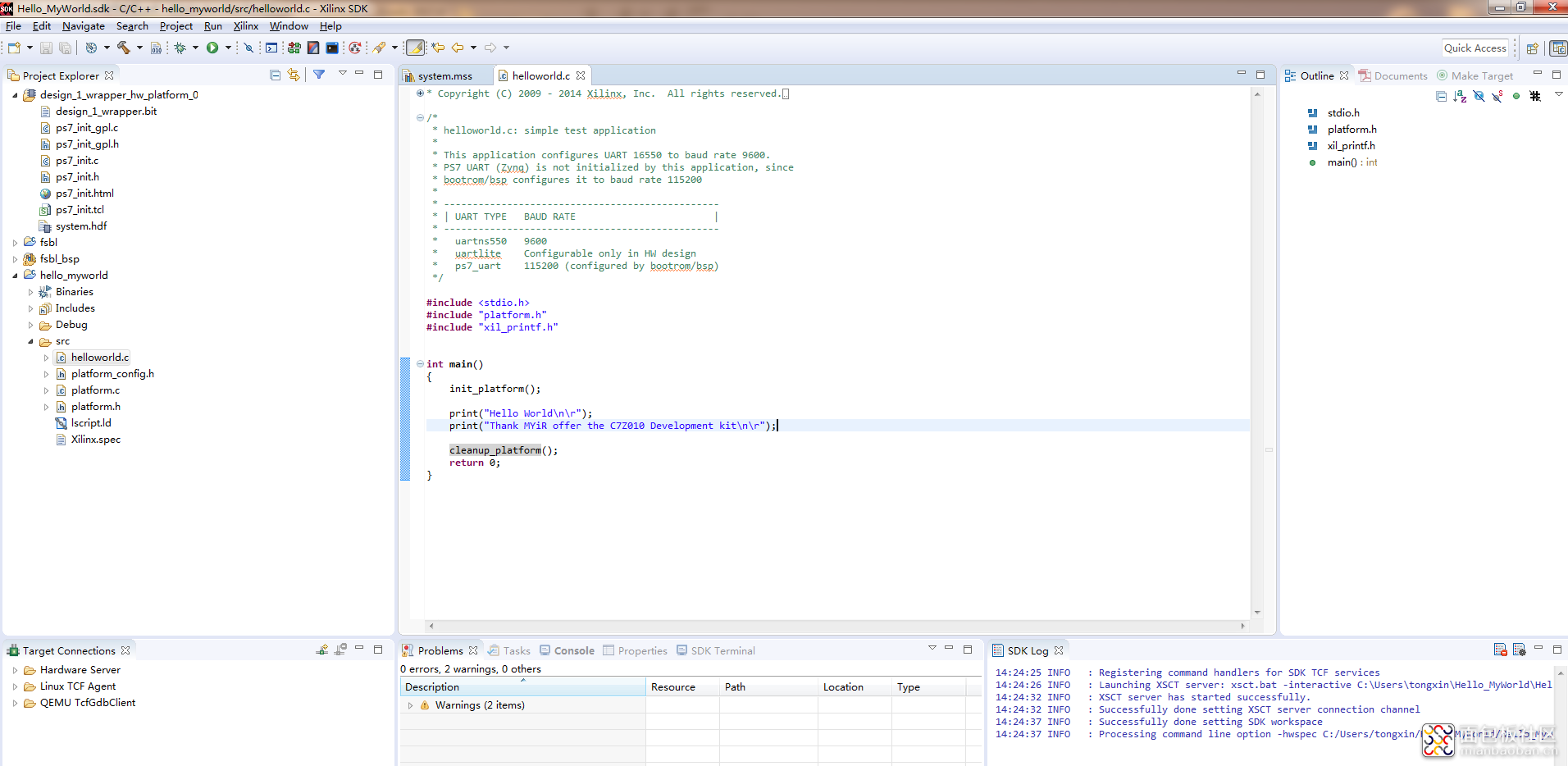

第1章启动SDK截图如下:

生成的BOOT.bin文件:

第1章BOOT.zip

(39.97 KB, 下载次数: 1)

第1章BOOT.zip

(39.97 KB, 下载次数: 1)

2019-12-1 19:38 上传

点击文件名下载附件

视频演示实验结果:https://v.youku.com/v_show/id_XNDQ1NDY5NTkxNg==.html?spm=a2h3j.8428770.3416059.1

第二章介绍通过EMIO引出GPIO,并控制三色灯D34,涉及两个工程,即FSBL与控制三色灯的应用工程

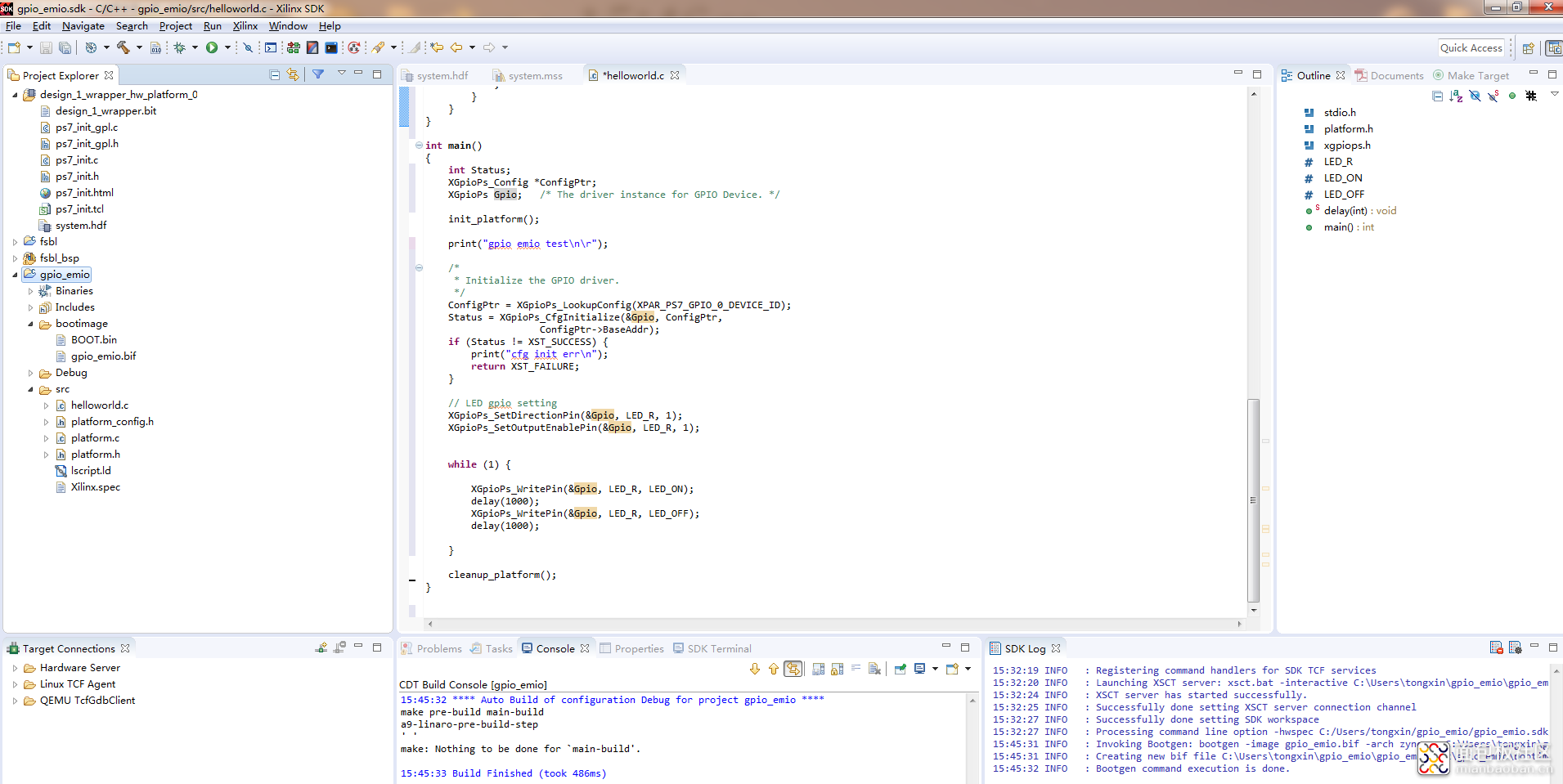

第2章启动SDK截图如下:

生成的BOOT.bin文件:

第2章BOOT.zip

(43.73 KB, 下载次数: 2)

第2章BOOT.zip

(43.73 KB, 下载次数: 2)

2019-12-1 19:56 上传

点击文件名下载附件

视频演示实验结果:https://v.youku.com/v_show/id_XNDQ1NDY5OTI0MA==.html?spm=a2h3j.8428770.3416059.1

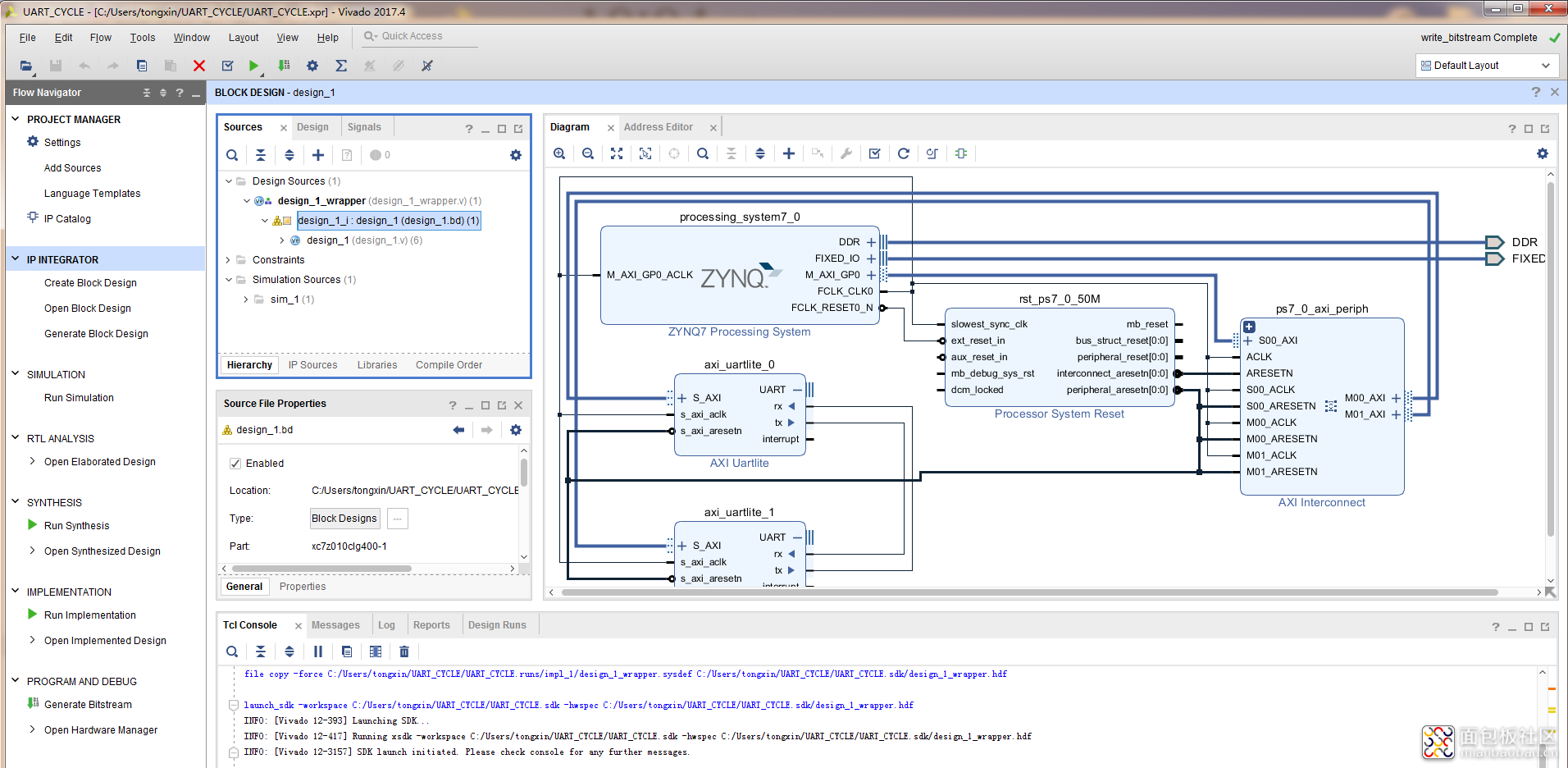

第三章通过配置ps以及调用在pl端的axi_uartlite ip核,实现ps与pl之间通过AXI GP Master进行通信

第3章自动连线后截图如下:

第3章启动SDK截图如下:

生成的BOOT.bin文件

第3章BOOT.zip

(61.54 KB, 下载次数: 1)

第3章BOOT.zip

(61.54 KB, 下载次数: 1)

2019-12-1 20:06 上传

点击文件名下载附件

视频演示实验结果:https://v.youku.com/v_show/id_XNDQ1NDcwMDE1Ng==.html?spm=a2h3j.8428770.3416059.1

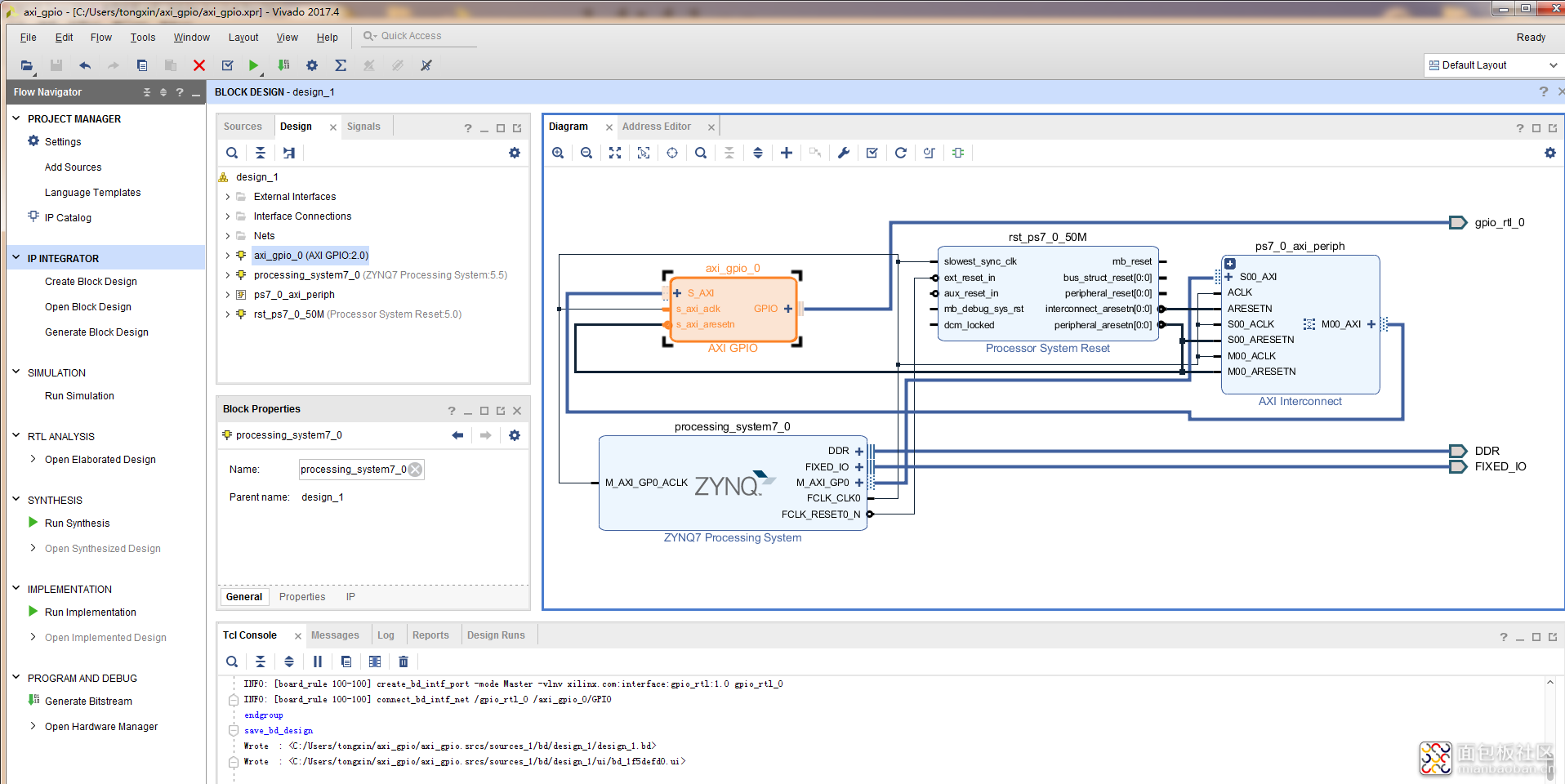

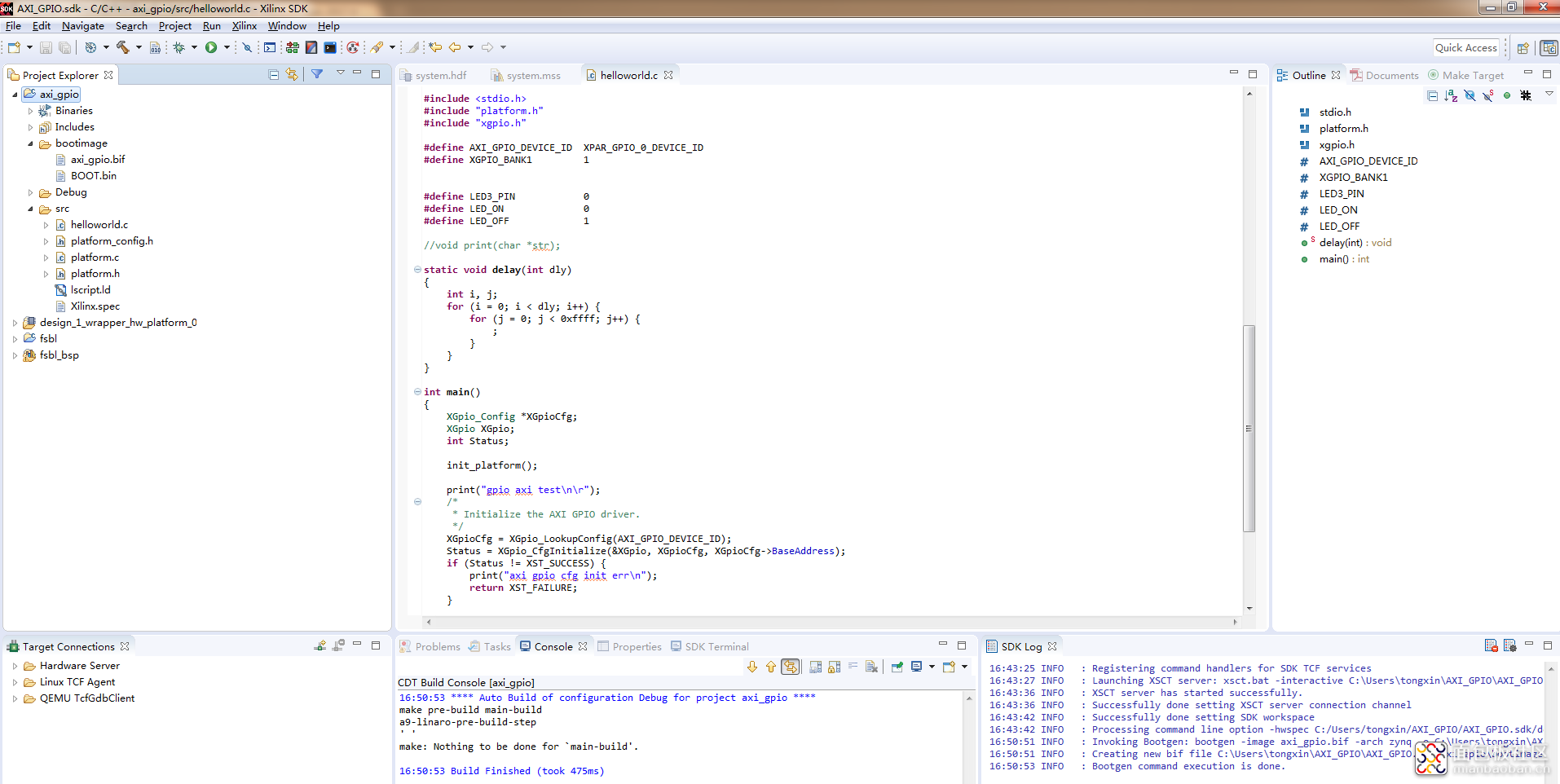

第四章使用xilinx的gpio核,在PL端实现一个gpio控制器,控制二极管D3

第4章自动连线后截图如下:

第4章启动SDK截图如下:

生成的BOOT.bin文件:

第4章BOOT.zip

(58.69 KB, 下载次数: 0)

第4章BOOT.zip

(58.69 KB, 下载次数: 0)

2019-12-1 20:14 上传

点击文件名下载附件

视频演示实验结果:https://v.youku.com/v_show/id_XNDQ1NDcwMTAxNg==.html?spm=a2h3j.8428770.3416059.1

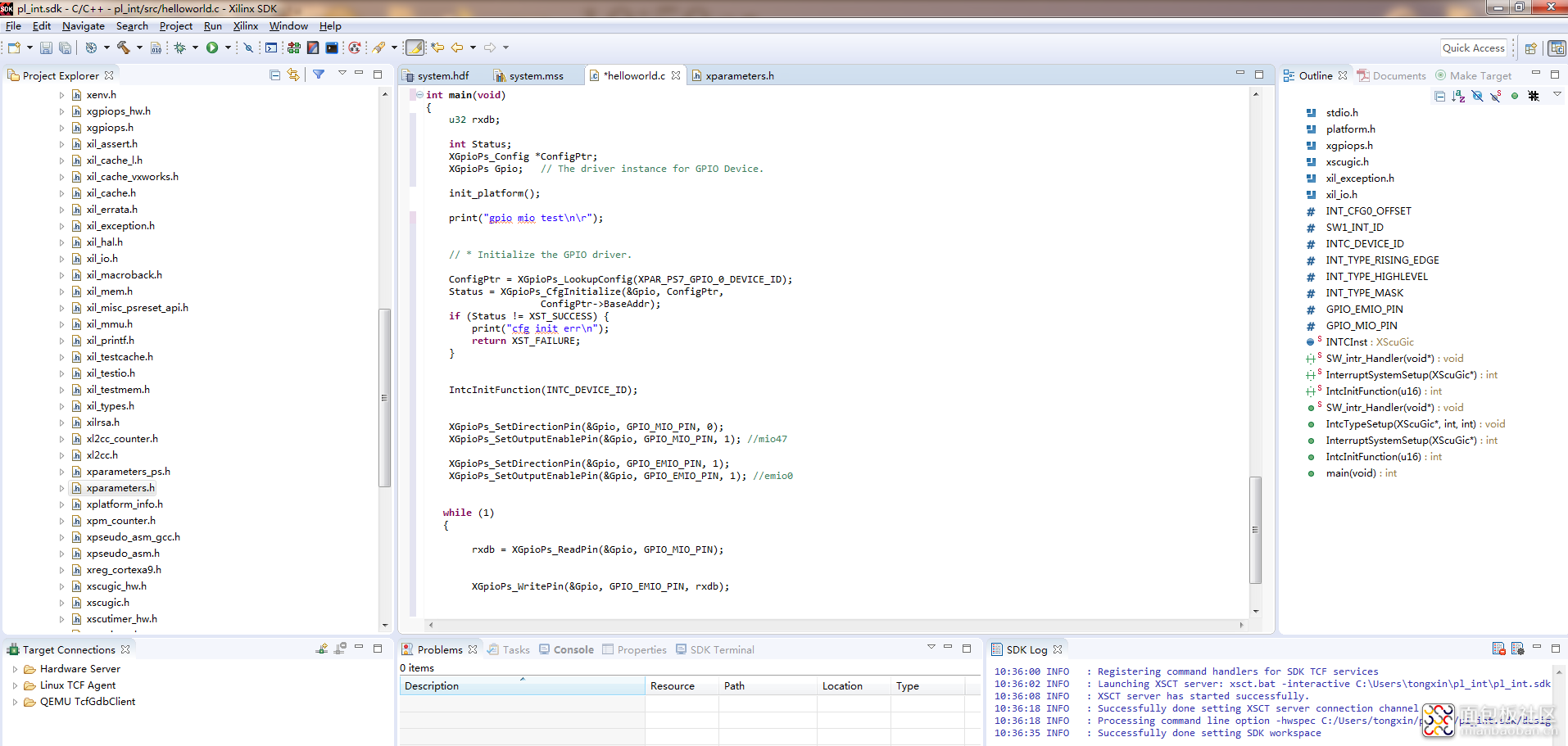

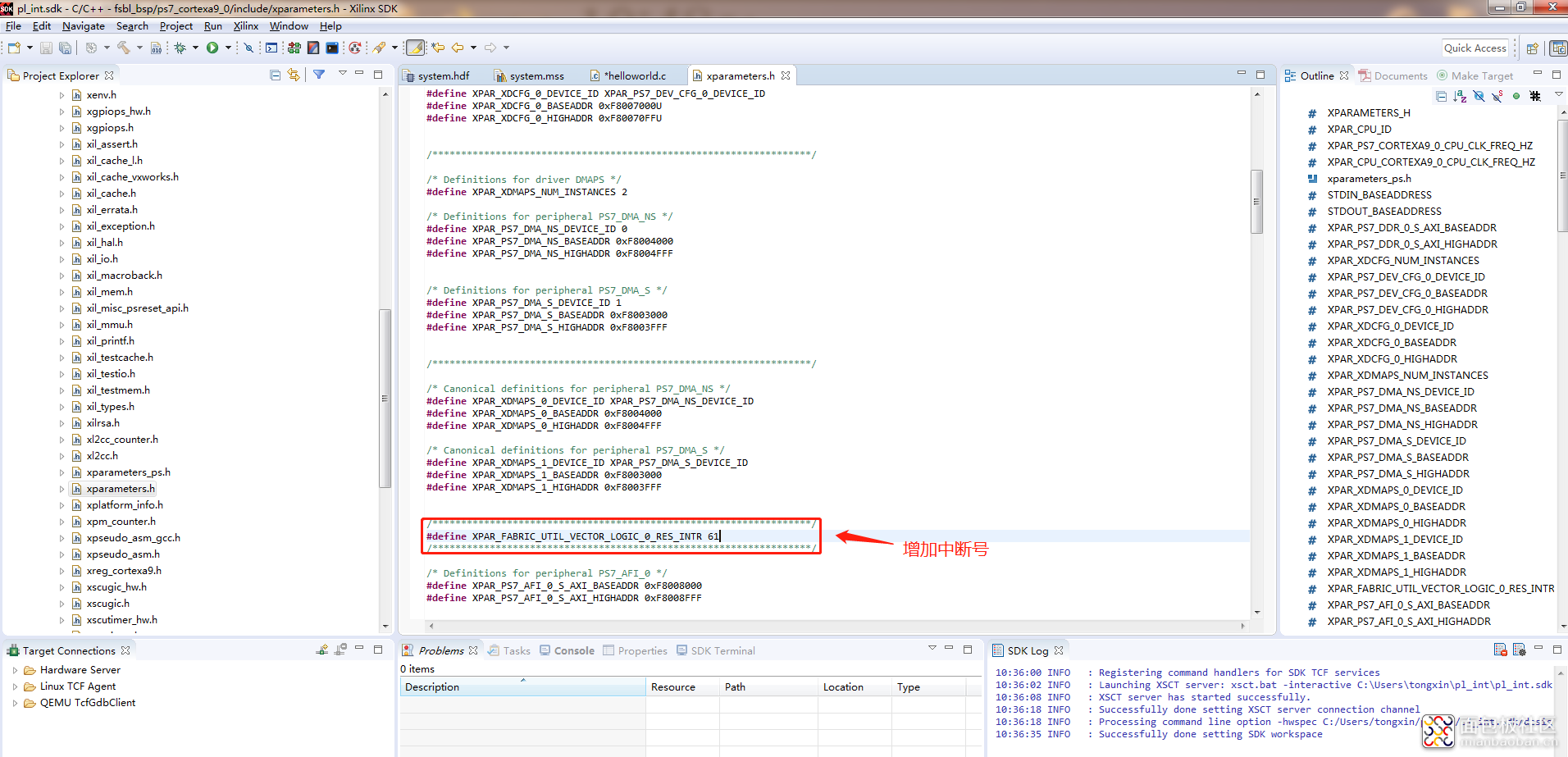

第五章使用开关K2来触发PL中断

第5章启动SDK截图如下:

第5章SDK中添加中断号截图如下:

生成的BOOT.bin文件:

第05章BOOT.zip

(71.87 KB, 下载次数: 0)

第05章BOOT.zip

(71.87 KB, 下载次数: 0)

2019-12-1 20:24 上传

点击文件名下载附件

视频演示实验结果:https://v.youku.com/v_show/id_XNDQ1NDcwMjE4MA==.html?spm=a2h3j.8428770.3416059.1

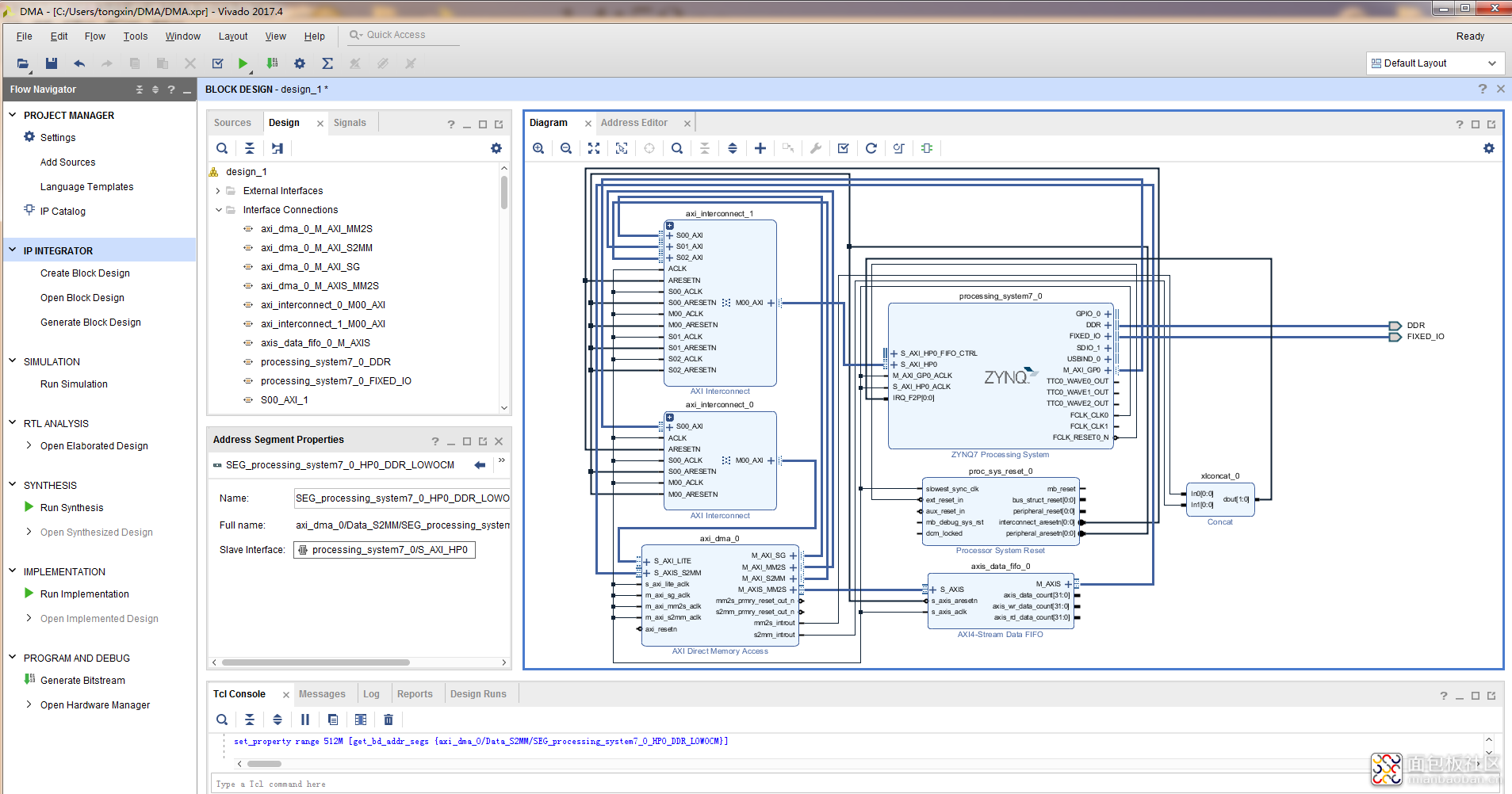

第八章通过DMA能让PL和PS进行高速数据传输

第8章自动连线并分配地址空间截图如下:

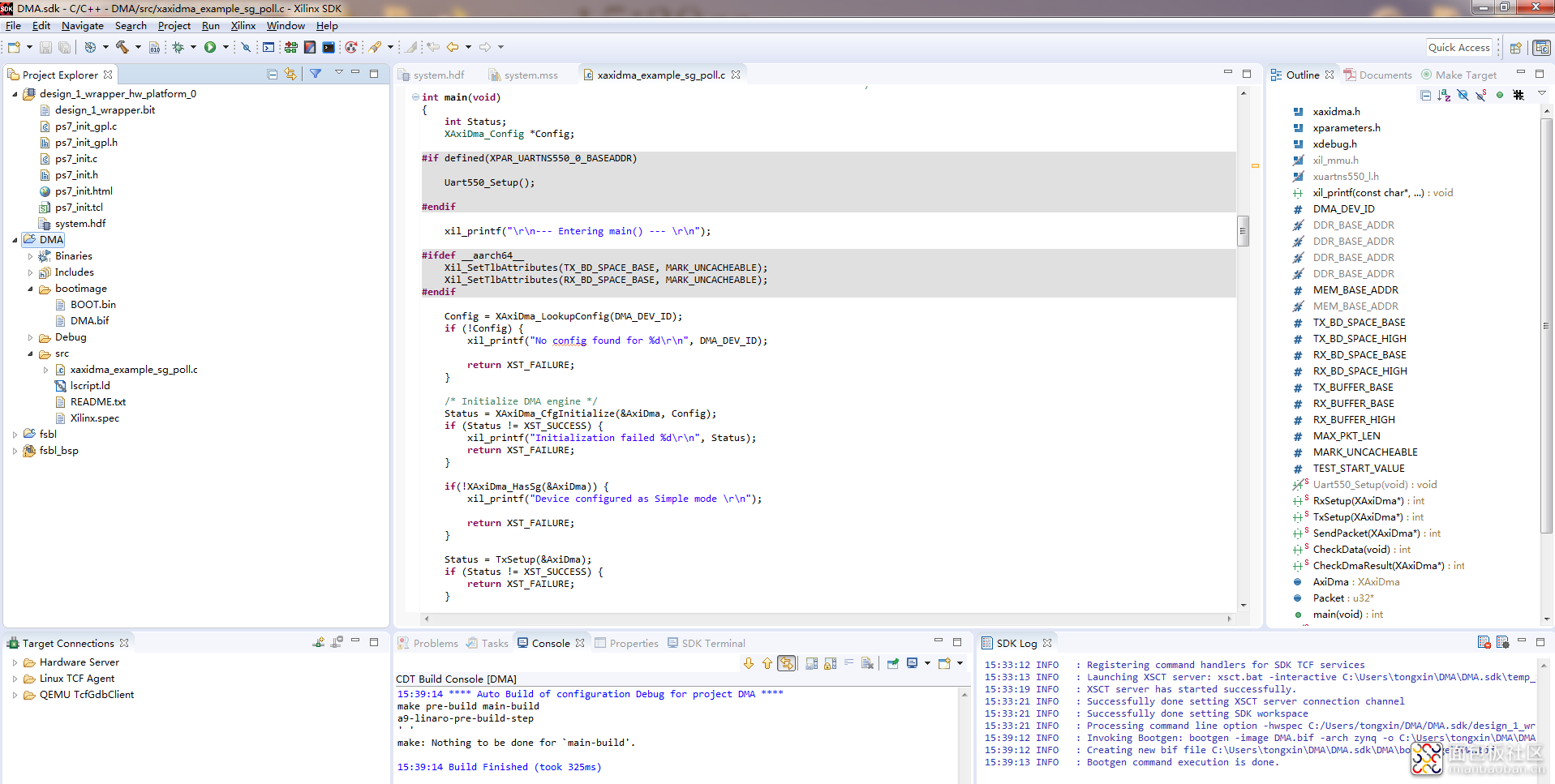

第8章启动SDK截图如下:

生成的BOOT.bin文件:

第8章BOOT.zip

(259.46 KB, 下载次数: 1)

第8章BOOT.zip

(259.46 KB, 下载次数: 1)

2019-12-1 20:33 上传

点击文件名下载附件

视频演示实验结果:https://v.youku.com/v_show/id_XNDQ1NDcwMzEwNA==.html?spm=a2h3j.8428770.3416059.1

以上就是近期验证的几个实验,通过这几个实验的实践,感觉加深了对MYD-C7Z010开发板的了解,虽然都是采用TF进入SD卡启动模式去验证FPGA设计的正确性,但从中可以学到不少关于FPGA设计的关键环节。此次分享就到这啦,后续条件允许的话,再对LCD、HDMI显示做进一步研究。欢迎各位网友来访参观,对以上实验分享如有异议,请回帖告知,谢谢!

全部回复 4

评测文章

热帖

大家都在看的技术资料

举报

内容系网友发布,其中涉及到安全隐患的内容系网友个人行为,不代表面包板社区观点

关闭

站长推荐 /1

/1

/1

/1

-

返回顶部

返回顶部

-

工具栏