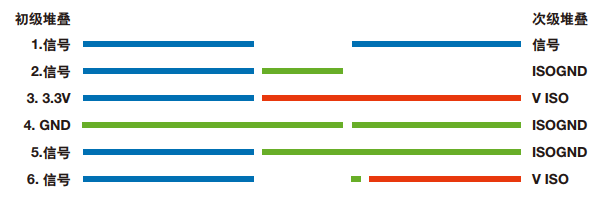

图1.PCB层堆叠示例

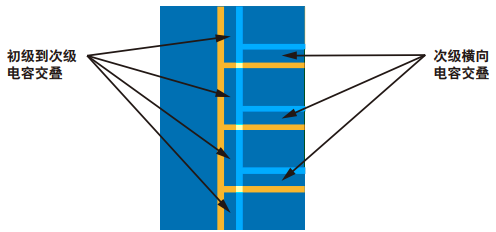

埋层(原边3、4层,副边2至5层)可承载电力和接地电流。跨越隔离栅的交叠(例如原边上的第4层GND和副边上的第3层 V Iso)可形成理想的拼接电容。通过多层PCB堆叠可形成多个交叠,从而提高整体电容。为使电容最大,还必须减小参考层之间PCB电介质材料的厚度。另一个布局技巧就是交叠相邻的isoPower通道的各层。图2显示了一个具有四条相邻通道的示例。

图2.具有交叠拼接电容的四个相邻通道

本示例中,每个输出域与其他域隔离,但是我们仍能利用一些交叠电容。图3显示了这种堆叠,可看到每个isoPower器件可增加电容以及相邻隔离区连接的情况。

图3.具有交叠拼接电容的四个相邻通道

必须确保内部和外部间隙要求符合最终应用。还可使用铁氧体磁珠在任意电缆连接上提供过滤,从而减少可能产生辐射的天线效应。总结

如何在密集PCB布局中,最大限度降低多个isoPower器件的辐射?请参考以下几个要点↓

- 最大程度降低每个通道的电源要求

- 在多个PCB层上构建拼接

- 采用尽可能多的PCB层切实可行

- 在各参考层间使用最薄的电介质

- 在相邻域之间进行连接

- 确保内部和外部爬电距离仍然符合要求

- 电缆连接上提供过滤

来源:ADI

/5

/5