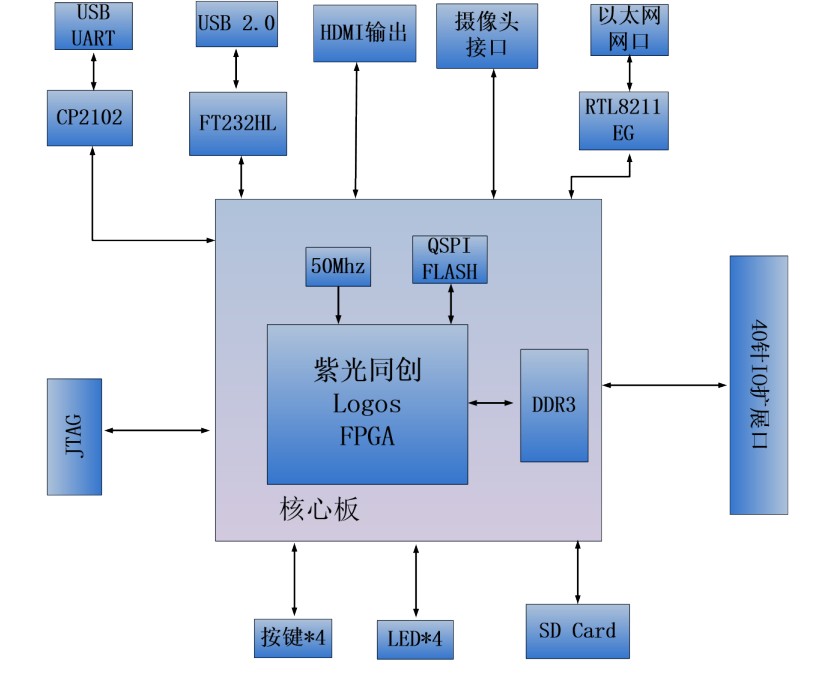

今天评估的是PGL22G,PGL22G6CMBG324。开发板核心板+扩展板的模式来设计的。核心板主要由 FPGA + DDR3 +QSPI FLASH 构成,速度等级为-6,温度等级为商业级 C。此型号为MBG324 封装, 324 个引脚,具有高速,高带宽,高容量等特点,适合高速数据通信,视频图像处理,高速数据采集等方面,可以满足工业与物联网等市场领域的应用需求。DDR3 芯片为 Micron 公司的 MT41J128M16HA-125 容量为 256MB; DDR3 芯片和 FPGA 芯片总线宽度为 16bit, 数据时钟频率高达800Mhz;这样的配置,可以满足高带宽的数据处理的需求。板上的128Mb QSPI FLASH芯片的型号为 W25Q128,用于存储 FPGA 系统的启动文件。

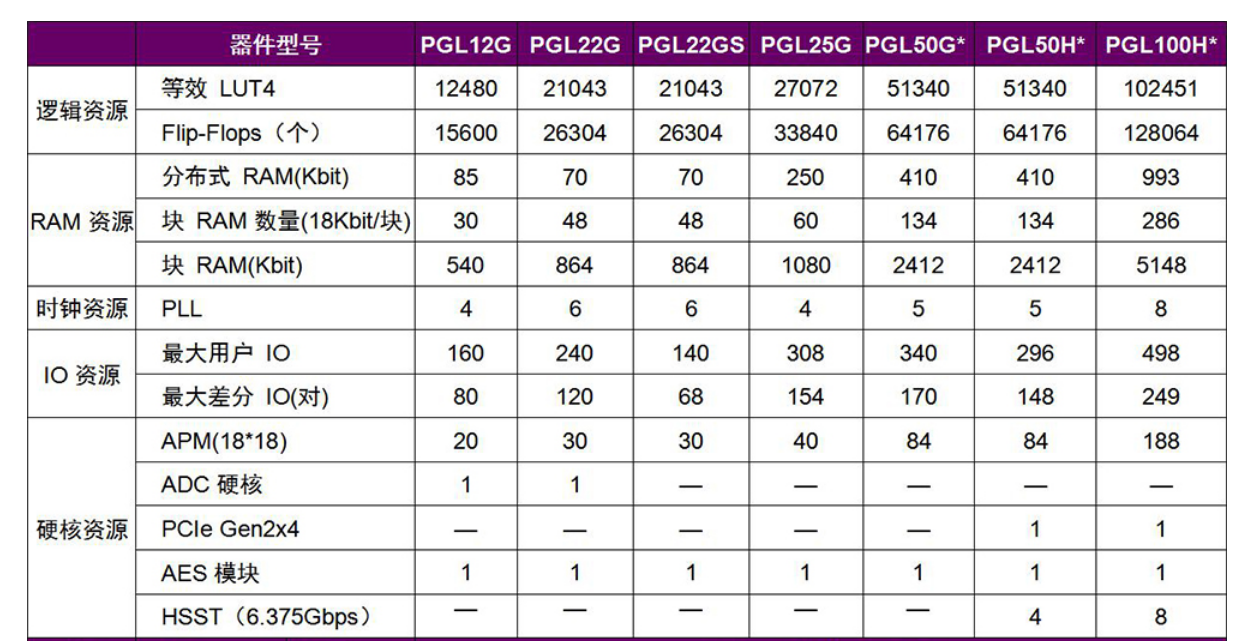

PGL22G系列资源

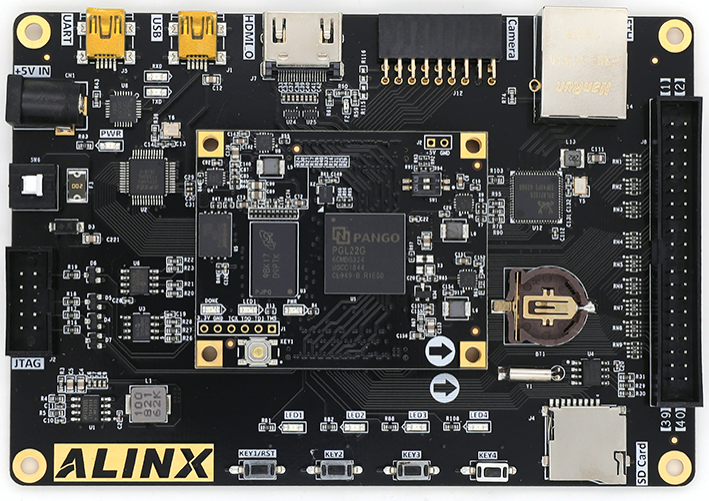

开发板正面

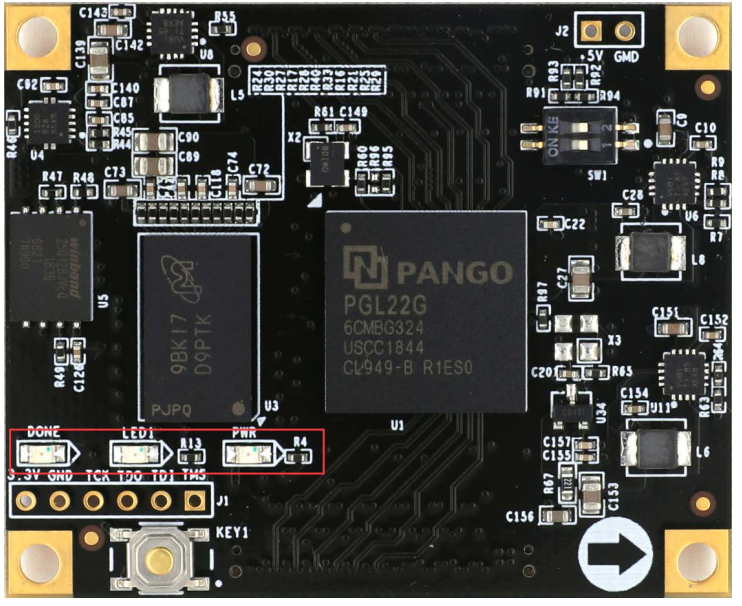

核心板

开发板架构图

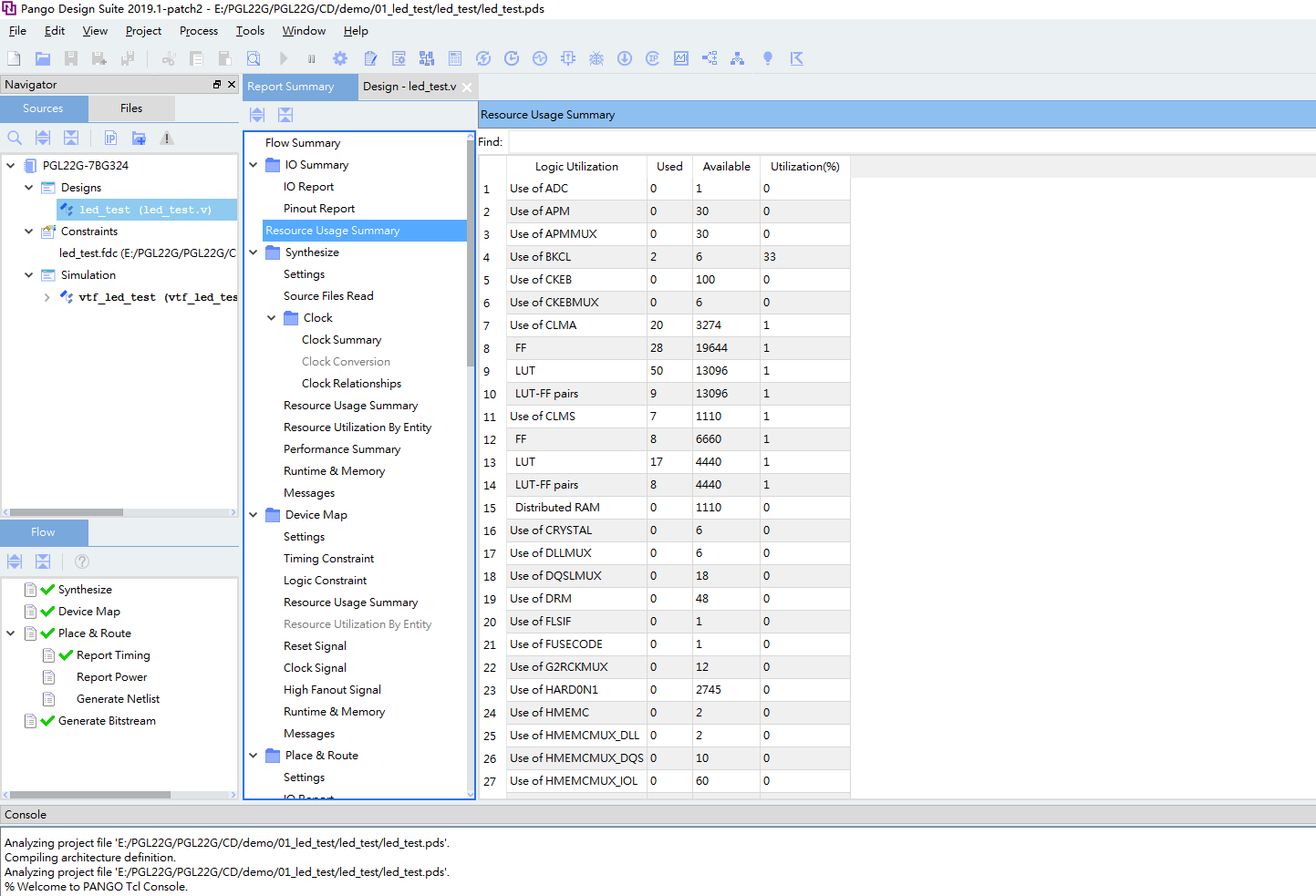

Pango Design Suite 为 EDA 套件是紫光同创开发的,与ISE差不多。

FPGA 的设计中通常使用计数器来计时,对于 50Mhz 的系统时钟,一个时钟周期是 20ns,那

么表示一秒需要 50000000 个时钟周期,如果一个时钟周期计数器累加一次,那么计数器从 0 到

49999999 正好是 50000000 个周期,就是 1 秒的时钟

timescale 1ns/1nsmodule led_test ( sys_clk, // system clock 50Mhz on board rst_n, // reset ,low active led // LED,use for control the LED signal on board ); input sys_clk; input rst_n; output [3:0] led; //define the time counter reg [31:0] timer; reg [3:0] led; always @(posedge sys_clk or negedge rst_n) begin if (~rst_n) timer <= 32'd0; // when the reset signal valid,time counter clearing else if (timer == 32'd199_999_999) //4 seconds count(50M*4-1=199999999) timer <= 32'd0; //count done,clearing the time counter else timer <= timer + 1'b1; //timer counter = timer counter + 1 end always @(posedge sys_clk or negedge rst_n) begin if (~rst_n) led <= 4'b0000; //when the reset signal active else if (timer == 32'd49_999_999) //time counter count to 1st sec,LED1 lighten led <= 4'b0001; else if (timer == 32'd99_999_999) //time counter count to 2nd sec,LED2 lighten begin led <= 4'b0010; end else if (timer == 32'd149_999_999) //time counter count to 3nd sec,LED3 lighten led <= 4'b0100; else if (timer == 32'd199_999_999) //time counter count to 4nd sec,LED4 lighten led <= 4'b1000; end endmodule

复制代码