[color=rgb(51, 51, 51) !important]PLL 时钟管理单元,输出2路相位相差90°的时钟,一路提供给系统内所有逻辑使用,一路输出到SDRAM芯片的clk管脚上。(相位为-90°)

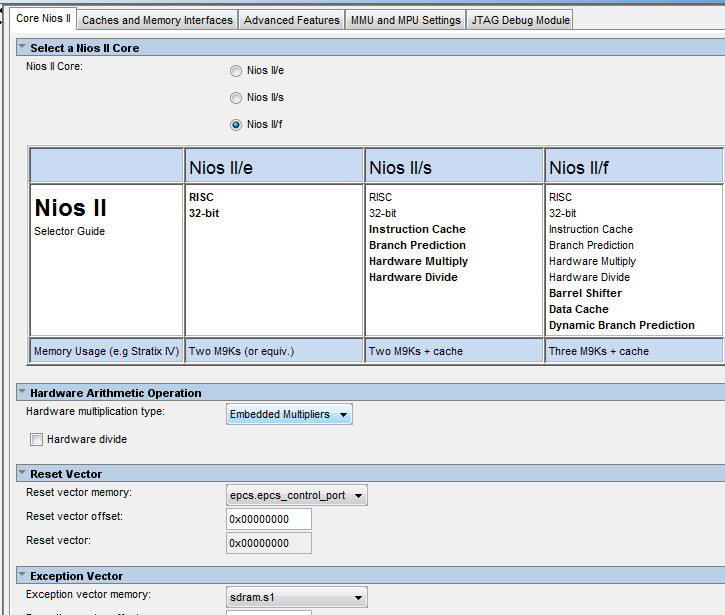

[color=rgb(51, 51, 51) !important]NIOS II 处理器 ,选择f(快速)版本,其他默认。

[color=rgb(51, 51, 51) !important]SDRAM控制器,16位数据位宽,12位行地址,9位列地址,用作NIOS II的数据和指令存储器

[color=rgb(51, 51, 51) !important]EPCS控制器,用以掉电存储FPGA和NIOS II的软硬件固件信息

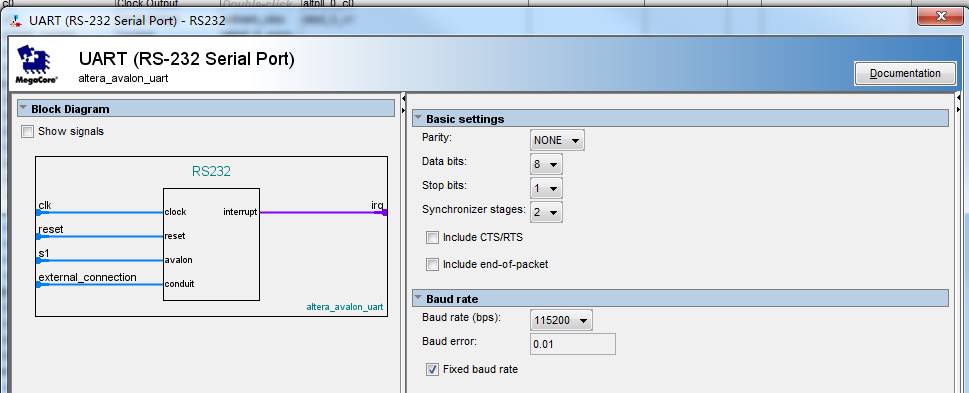

[color=rgb(51, 51, 51) !important]UART(RS232)控制器,用作系统标准输入输出设备,默认115200波特率

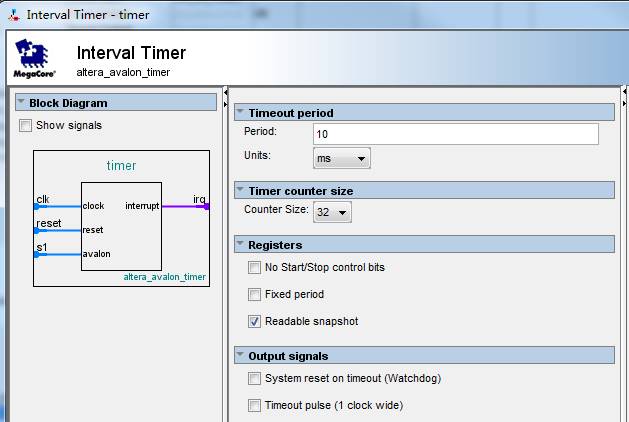

[color=rgb(51, 51, 51) !important]Timer定时器,设置默认10毫秒定时器,并可通过软件修改寄存器以修改定时时间。

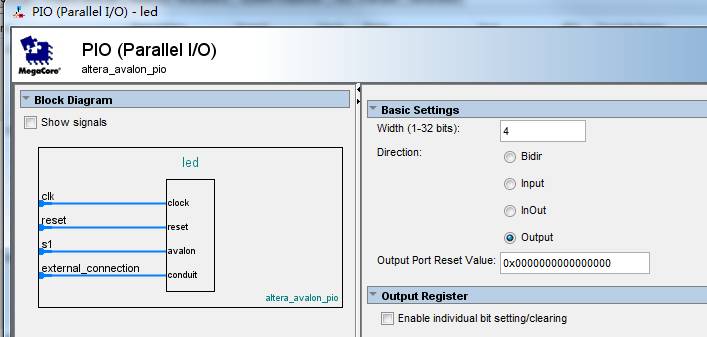

[color=rgb(51, 51, 51) !important]PIO,仅输出型PIO,4位,对应开发板上4个LED灯

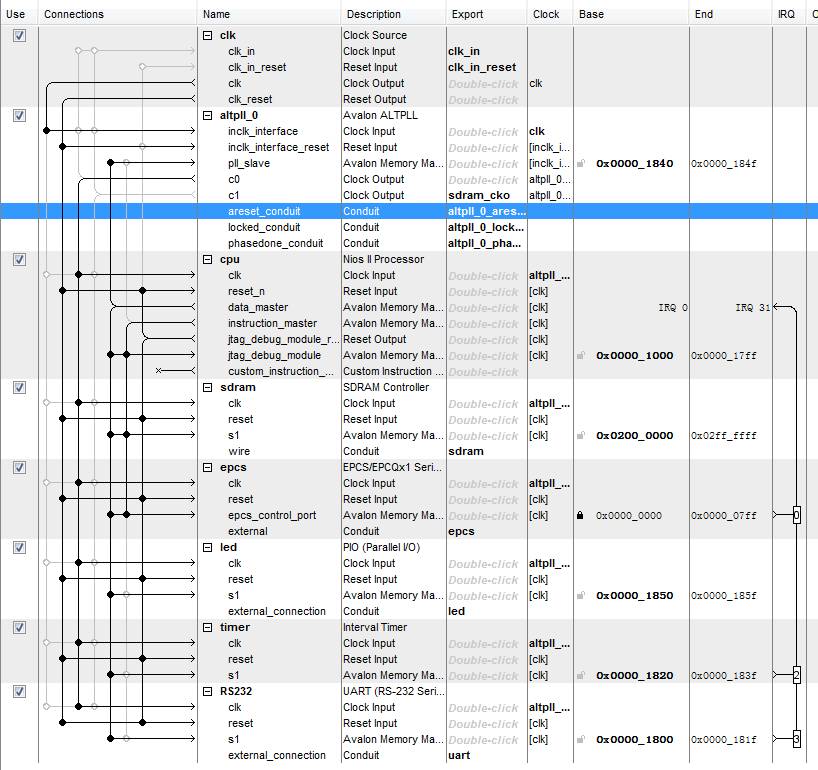

[color=rgb(51, 51, 51) !important]下图为搭建好的最小NIOS II应用系统

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]其中需要注意的是,驱动LED的PIO为4位,并直接命名为了led,uart串口被命名为了RS232,这是为了与RT-Thread官方提供的NIOS II的BSP文件中相关代码相对应。

[color=rgb(51, 51, 51) !important]NIOS II CPU相关设置

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]定时器参数设置

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]UART控制器相关设置

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]LED PIO相关设置

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]在Quartus II工程中例化CPU系统

[color=rgb(51, 51, 51) !important]设计顶层文件

[color=rgb(51, 51, 51) !important]将Qsys中搭建的系统命名为mysystem,然后generate得到HDL文件,在Quartus II软件中添加mysystem.qsys文件,新建Verilog文件,完善顶层例化信息,完善后的代码如下所示:

[color=rgb(51, 51, 51) !important]module ac620_ghrd( input wire reset_n, input wire clk, output wire [11:0] sdram_addr, output wire [1:0] sdram_ba, output wire sdram_cas_n, output wire sdram_cke, output wire sdram_clk, output wire sdram_cs_n, inout wire [15:0] sdram_dq, output wire [1:0] sdram_dqm, output wire sdram_ras_n, output wire sdram_we_n, output wire [3:0] led, input wire uart_rxd, output wire uart_txd, output wire epcs_dclk, output wire epcs_sce, output wire epcs_sdo, input wire epcs_data0 ); mysystem u0 ( .clk_in_reset_reset_n (reset_n), .clk_in_clk (clk), .sdram_addr (sdram_addr), .sdram_ba (sdram_ba), .sdram_cas_n (sdram_cas_n), .sdram_cke (sdram_cke), .sdram_cs_n (sdram_cs_n), .sdram_dq (sdram_dq), .sdram_dqm (sdram_dqm), .sdram_ras_n (sdram_ras_n), .sdram_we_n (sdram_we_n), .led_export (led), .uart_rxd (uart_rxd), .uart_txd (uart_txd), .sdram_cko_clk (sdram_clk), .epcs_dclk (epcs_dclk), .epcs_sce (epcs_sce), .epcs_sdo (epcs_sdo), .epcs_data0 (epcs_data0), .altpll_0_phasedone_conduit_export (), .altpll_0_locked_conduit_export (), .altpll_0_areset_conduit_export () ); endmodule

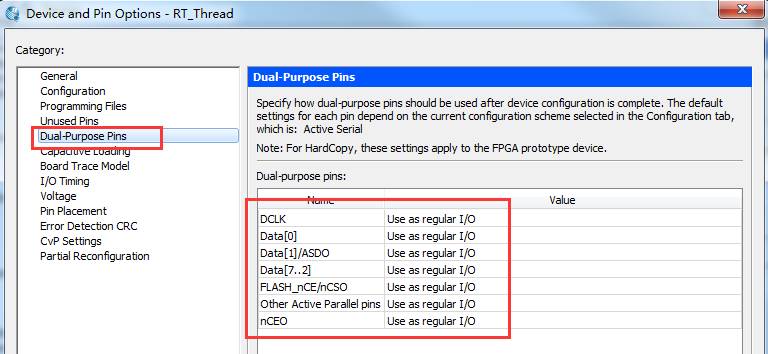

[color=rgb(51, 51, 51) !important]设置EPCS管脚功能

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]根据AC620 FPGA开发板引脚分配表或者开发板背面的丝印对用到的引脚功能一一分配正确的管脚。注意设置所有的IO电平为3.3LVTTL,以防止无法正确驱动SDRAM存储器。另外由于使用到了EPCS,因此需要在Quartus中设置其功能为regular IO,如下图所示:

[color=rgb(51, 51, 51) !important]添加SDC约束文件

[color=rgb(51, 51, 51) !important]在做基于NIOS II的SOPC开发时,务必要添加SDC约束文件,对系统的时钟进行约束,以保证Quartus II软件能够按照运行的频率要求对系统进行布局布线,否则,在没有加约束的情况下,整个系统可能最高运行频率比50MHz还要低,就会出现系统无法正常运行,软件无法下载等各种故障。本实例中约束文件比较简单,大家只需要将下述内容新建一个sdc文件保存起来并添加到Quartus II工程中即可:

[color=rgb(51, 51, 51) !important]set_time_format -unit ns -decimal_places 3 create_clock -name {clk} -period 20.000 -waveform { 0.000 10.000 } [get_ports {clk}] derive_pll_clocks

[color=rgb(51, 51, 51) !important]添加完成后编译整个工程,得到sof文件。

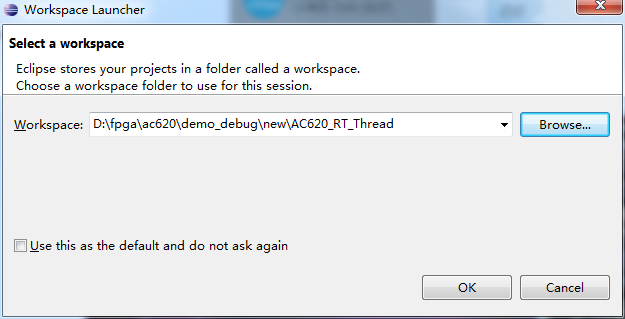

[color=rgb(51, 51, 51) !important]创建NIOS II应用工程模版

[color=rgb(51, 51, 51) !important]打开Quartus II集成的NIOS II软件开发工具(基于Eclipse),然后切换工作空间到Quartus II工程目录下。

[color=rgb(51, 51, 51) !important]

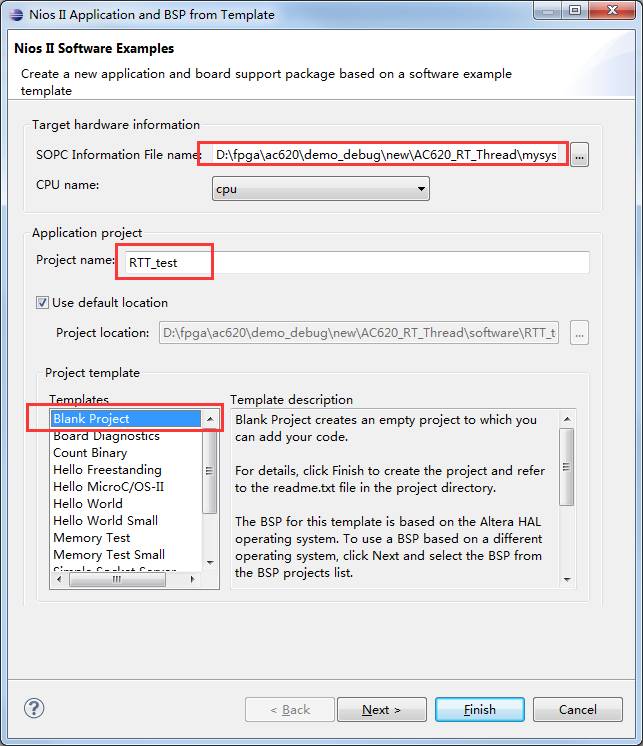

[color=rgb(51, 51, 51) !important]然后新建一个空白模版工程和bsp工程,如下所示。注意,sopcinfo文件路径一定不能错。

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]移植RT-Thread操作系统

[color=rgb(51, 51, 51) !important]下载RT-Thread操作系统源码

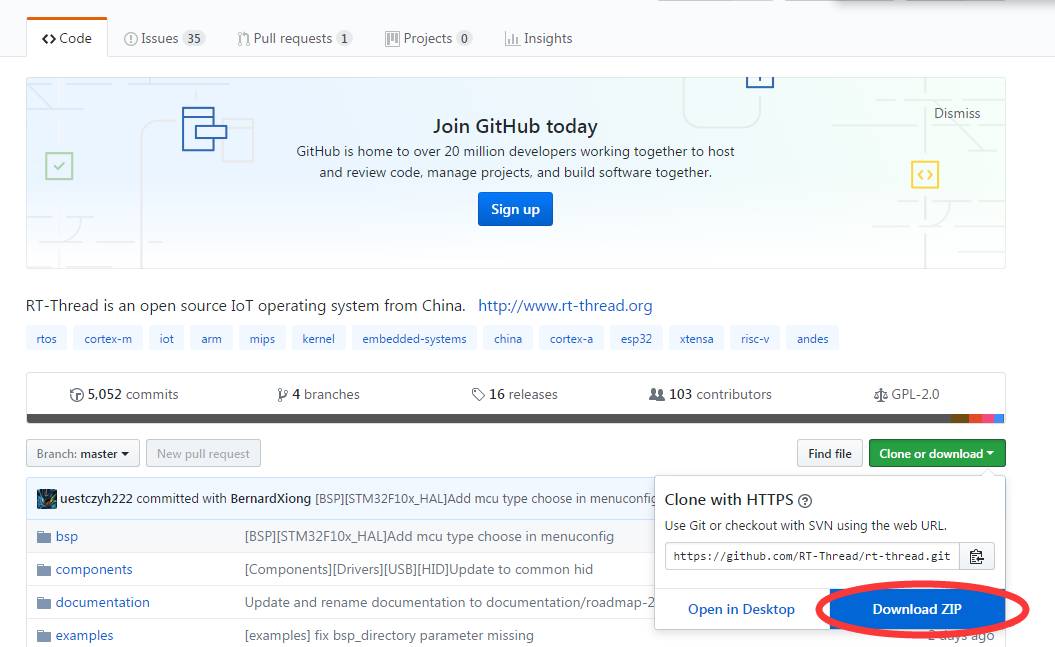

[color=rgb(51, 51, 51) !important]从git上下载RT-Thread操作系统的源文件,源码地址:https://github.com/RT-Thread/rt-thread选择master分支,点击Clone or download按钮,选择Download zip来下载源文件,当然也可以从我们提供的本实例的压缩包中得到该文件。

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]下载完成之后的文件名为:rt-thread-master.zip

[color=rgb(51, 51, 51) !important]移植RT-Thread操作系统源码

[color=rgb(51, 51, 51) !important]在RTT_Test工程下新建一个文件夹,命名为”rt-thread”,添加src文件夹,include文件夹到rt-thread文件夹下,然后添加libcpu下nios部分内容到rt-thread文件夹下。注意,libcpu下提供了对各种体系架构的cpu的支持,我们这里只需要nios部分即可,其他部分不需要添加到工程中。上述就完成了RT-Thread操作系统源码的添加。但是此时还并不完整,我们还需要添加对NIOS II CPU的bsp文件,该文件在bsp路径下的nios ii路径下,我们拷贝该路径下的所有.c和.h文件到工程中,注意,application.c是整个系统的应用部分,也就是main函数所在文件,因此将该文件从rt-thread文件夹中移出到软件工程的根目录(拖动即可),添加完成后的工程如下所示(具体可以参考我们提供的实例工程文件)。

[color=rgb(51, 51, 51) !important]

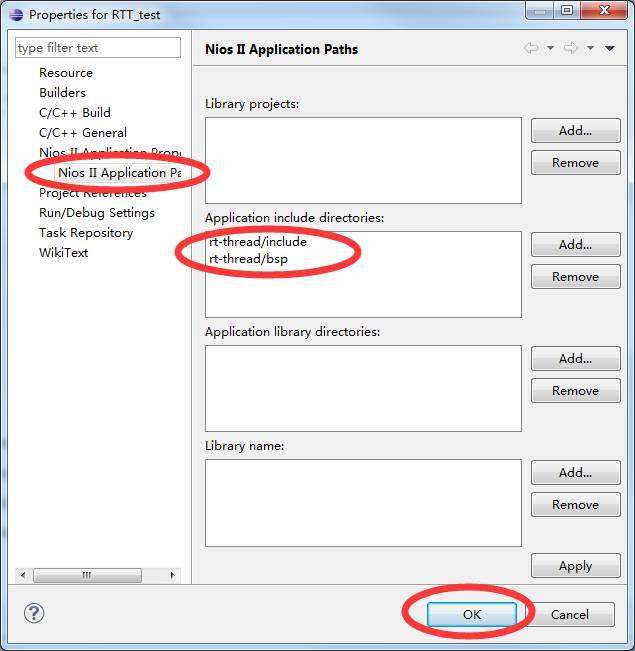

[color=rgb(51, 51, 51) !important]设置头文件搜索路径

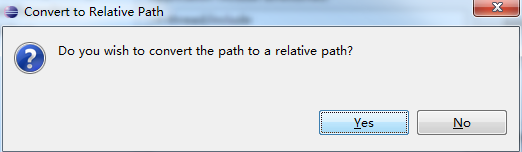

[color=rgb(51, 51, 51) !important]添加完所有的文件之后,我们还必须要在软件的设置中添加头文件搜索路径,选中RTT_test工程,鼠标右击选择Properties选项,在弹出的对话框中选中Nios II Application Paths选项,添加include和bsp文件夹道头文件路径中,然后确认关闭。如果弹出下述相对路径转换提示,选择Yes即可。

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]

至此,所有的运行RT-Thread操作系统的要求都已经满足了。

[color=rgb(51, 51, 51) !important]关闭FINSH支持功能

[color=rgb(51, 51, 51) !important]接下来,我们打开工程的rt-thread -> bsp -> rtconfig.h文件,定位到第80行左右,将#define RT_USING_FINSH这句话前面加上单行注释符“//”,以屏蔽该定义,即不使用FINSH功能。

[color=rgb(51, 51, 51) !important]运行RT-Thread操作系统

[color=rgb(51, 51, 51) !important]编译运行程序

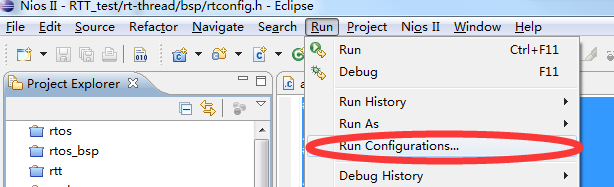

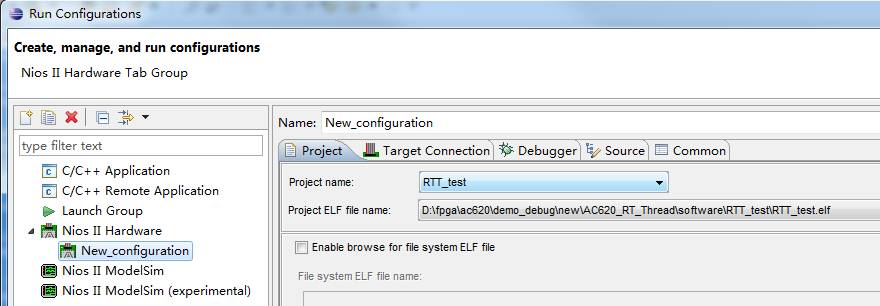

[color=rgb(51, 51, 51) !important]然后对整个工程进行全编译(快捷键为Ctrl + B),编译无误,就会得到可下载到NIOS II CPU中运行的elf文件,然后在菜单栏中依次点击RUN -> Run Configurations选项,打开下载运行页面。

[color=rgb(51, 51, 51) !important]

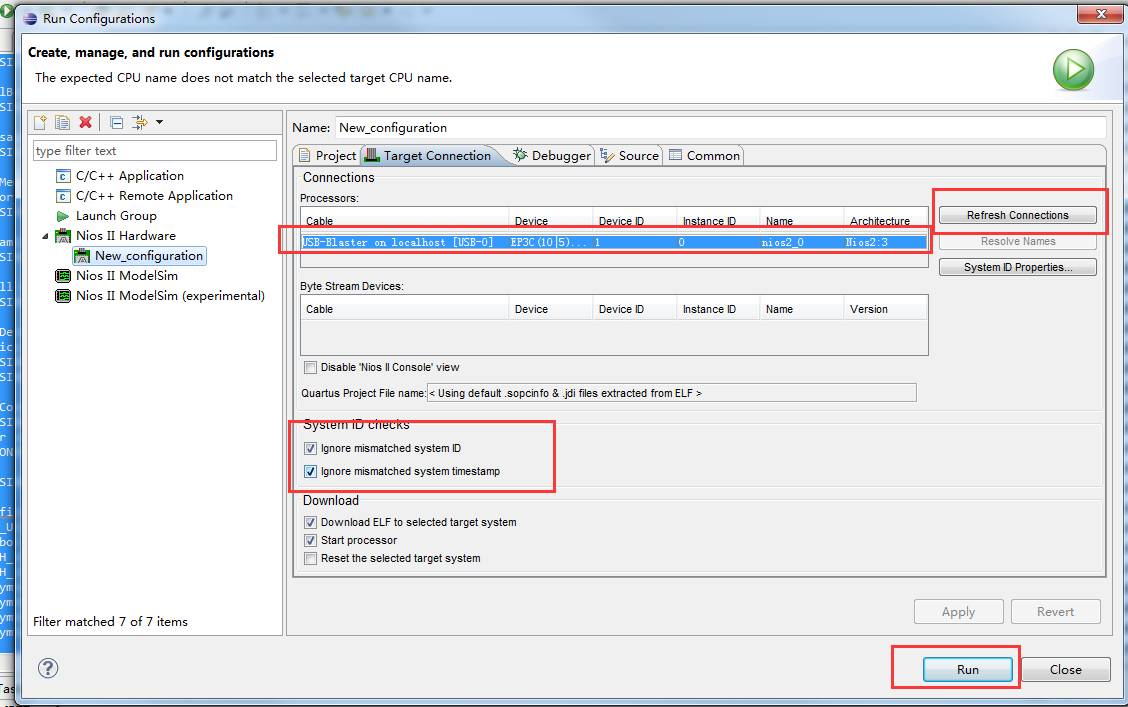

[color=rgb(51, 51, 51) !important]新建一个硬件运行配置并选择RTT_test工程,然后切换到Target Connection选项卡,刷新连接以确认硬件USB Blaster已经找到CPU。注意,在此操作之前需要先将Quartus II软件编译生成的sof文件下载到开发板中,并使用Micro USB数据线连接开发板和电脑,并打开串口调试工具,以找到开发板对应串口,设置波特率115200,ASCII接收。

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]

勾选忽略system id和时间戳选项,然后点击Run。即可开始软件程序的下载。

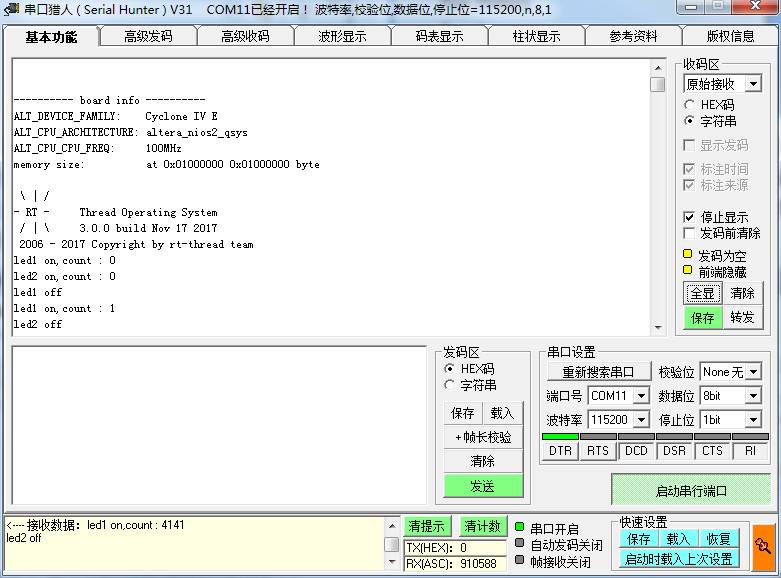

[color=rgb(51, 51, 51) !important]实验结果

[color=rgb(51, 51, 51) !important]下载完成后,即可在串口调试助手上看到系统运行时打印的信息,同时,开发板上4个LED灯循环闪烁。

[color=rgb(51, 51, 51) !important]

[color=rgb(51, 51, 51) !important]

/5

/5