一、相关环境准备

1.软件Install

2.硬件Device

二、硬件环境搭建

1.开发板连接

2.下载代码到开发板

三、软件环境搭建

1.启动Eclipse软件

2. 创建新的工程

3. 用OpenOCD调试

四、OpenOcd烧录固化

五、Efinity烧录固化

五、总结

一、相关环境准备

1.软件Install

1.Efinity® Software

链接:https://pan.baidu.com/s/1bKzy7hD9lv8FlxXZpyp2zw提取码:s745

2.RISC-V SDK

链接:https://pan.baidu.com/s/1jwoUjRv1i5-RGmppYfacew提取码:cpp6

2.硬件Device

此流程是基于T120F324的官方实验板进行的操作,后续会更新实际RiscV内核移植起来有关的注意事项。

1.Trion®T120F324开发板

2. 12V电源DC座子

3.Micro-USB连接线

4.(可选) USB转串口模块

5.(可选) FTDI设备:C232HM-DDHSL-0下载电缆

二、硬件环境搭建

1.开发板连接

开发板接12V电源,USB线连接电脑和开发板;

调试debug也可以用usb线,也可以用C232HM电缆:

如果使用C232电缆,板子上接线参考项目工程中 引脚的定义。

我这里用的是T120的开发板,附上相关的原理图:

链接:https://pan.baidu.com/s/1nbE4Vz03wOdIeLR3TZPPCg提取码:w7tj

2.下载代码到开发板

上文的软件准备环境中,我们已经下载了Opal,Jade,Ruby三种不同规格的版本;

此例程是针对T120开发板设计的,所以不必有太多的改动。

1. 此时选择Ruby版本,拷贝到没有中文,标点以及特殊字符的路径内。

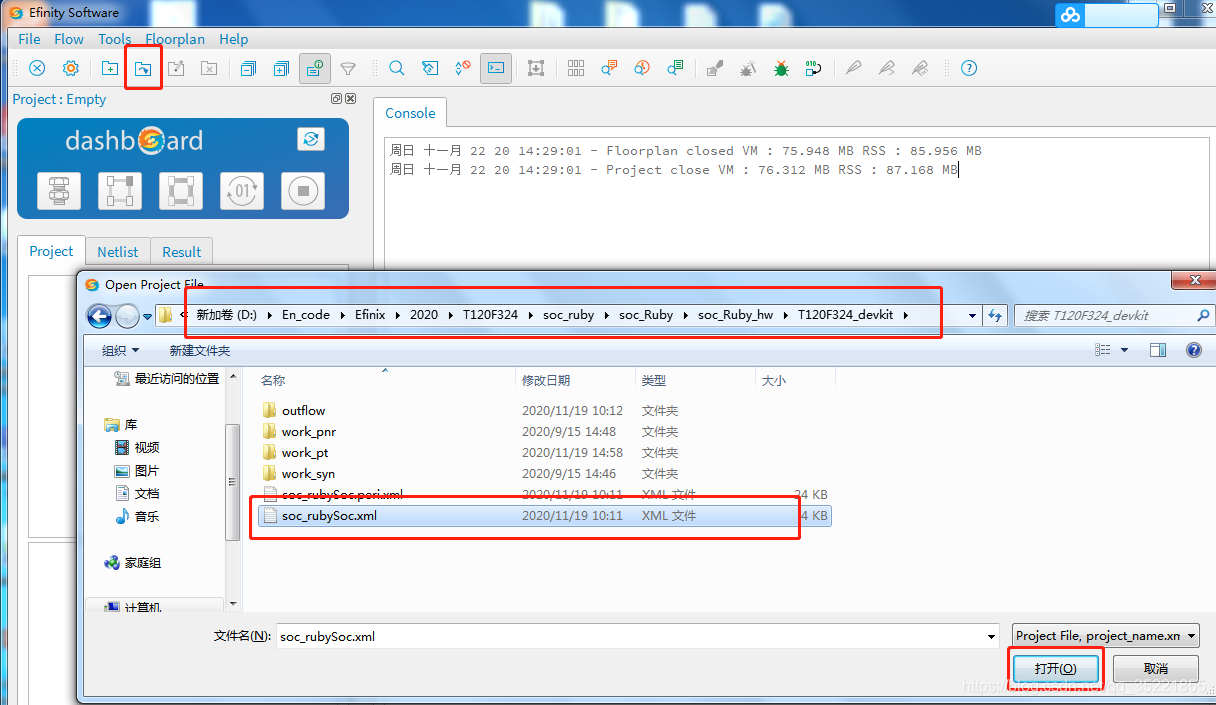

2. Efinity软件 打开soc_rubySoc工程。

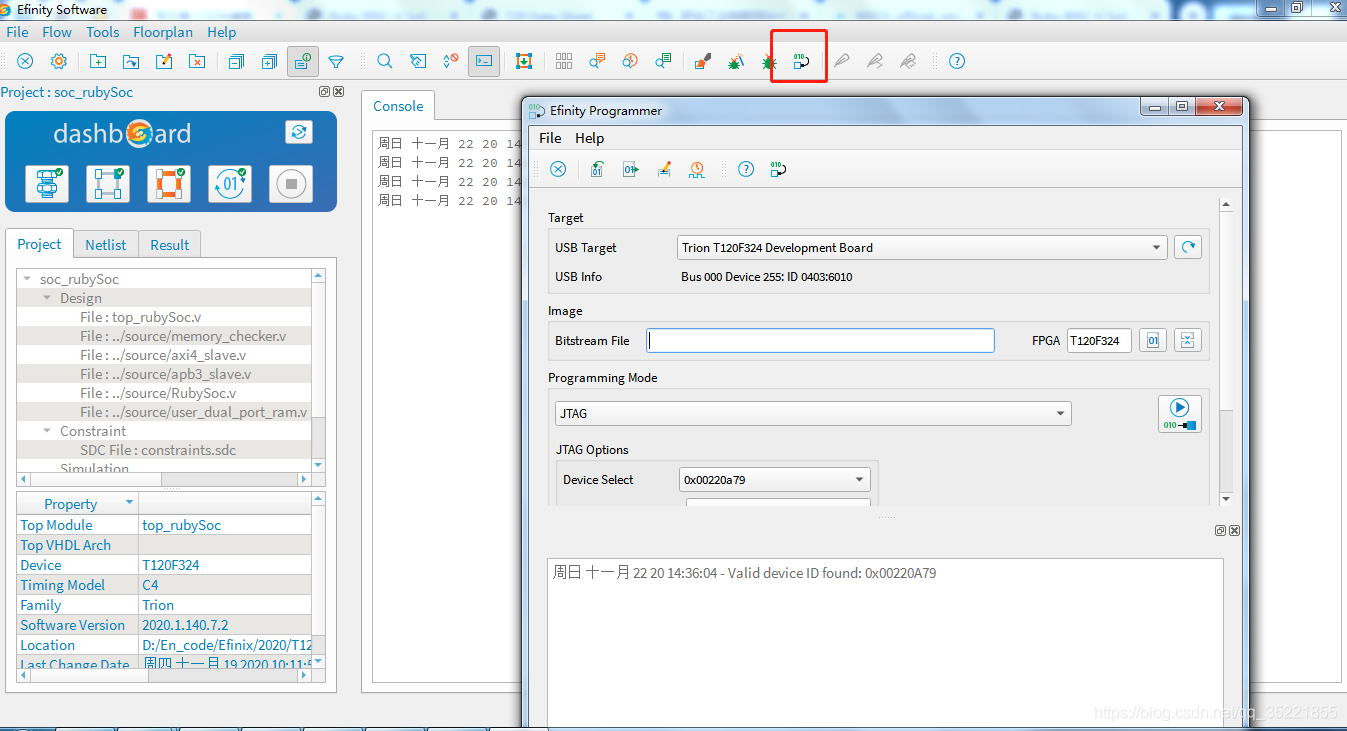

3. 点击Efinity菜单栏open programmer按钮下载工程到T120开发板内。

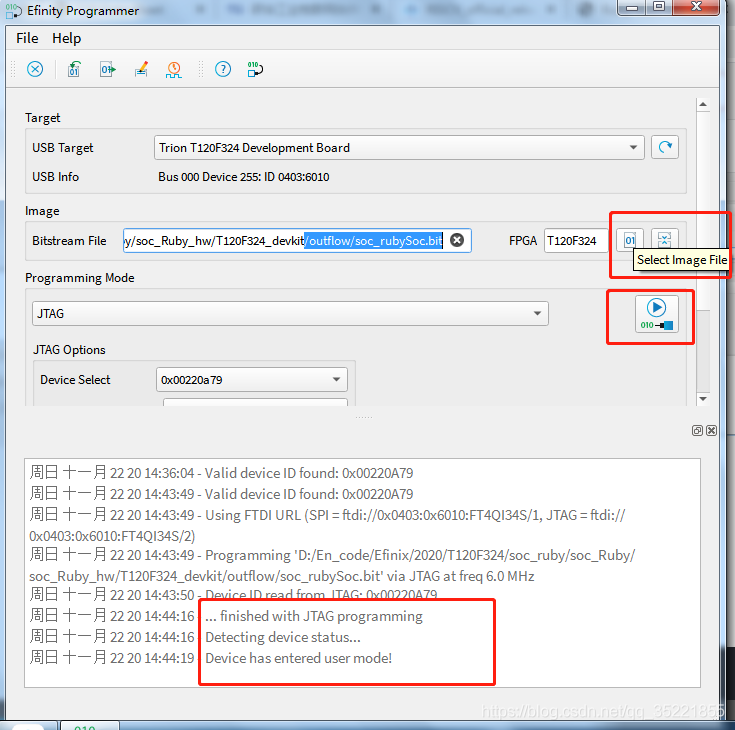

4. 点击选择路径按钮,选择soc_rubySoc.bit文件;Programming Mode选择JTAG,节省时间;点击Start Program,出现finished即为下载成功。

5.注意事项

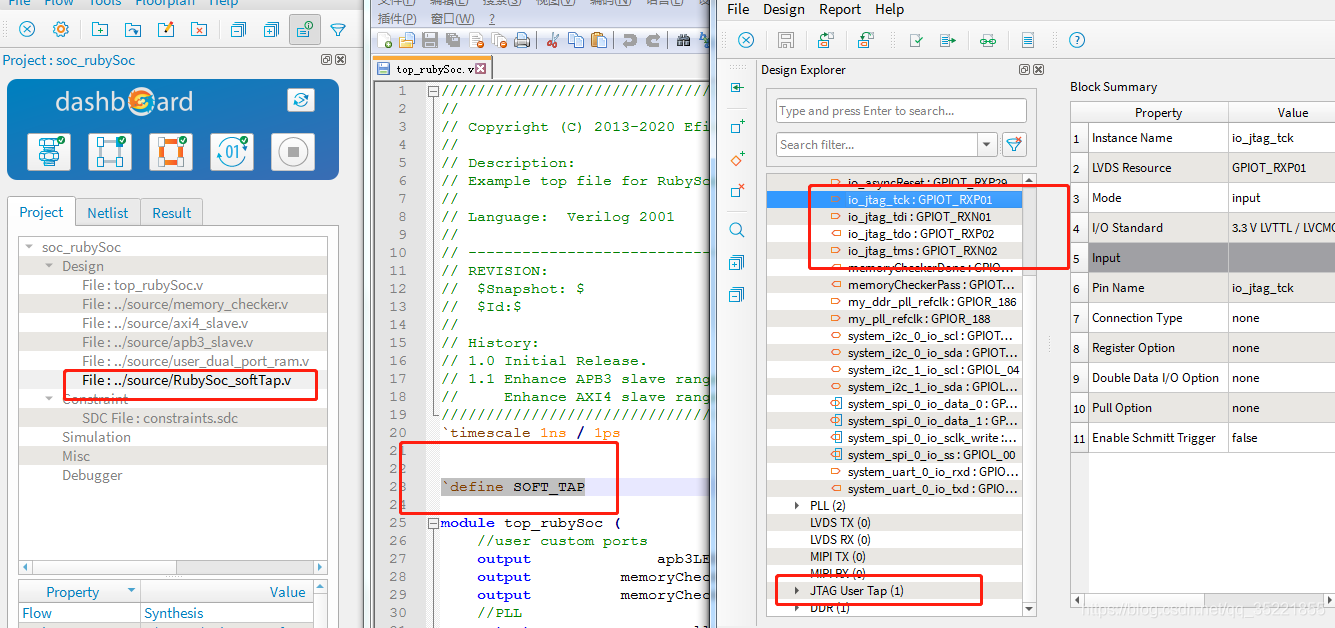

1.如果要使用232电缆线调试,那意味着添加了软连接调试口,整个工程需要做如下修改:

a.工程目录下将RubySoc.v换成RubySoc_softTap.v文件。

b.在top_rubySoc.v文件中添加 `define SOFT_TAP代码。

c.在interfaceplane 内部添加softio口,并添加对应JTAG资源。

2.如果使用C232HM电缆调试debugger并连接到电脑的时候,在第四步的下载界面的usb tagart会检测到两个,所以需要拔掉C232HM电缆,以免多端口识别下载失败,调试的时候插上即可;

三、软件环境搭建

在使用 eclipse 之前需要安装JAVA环境

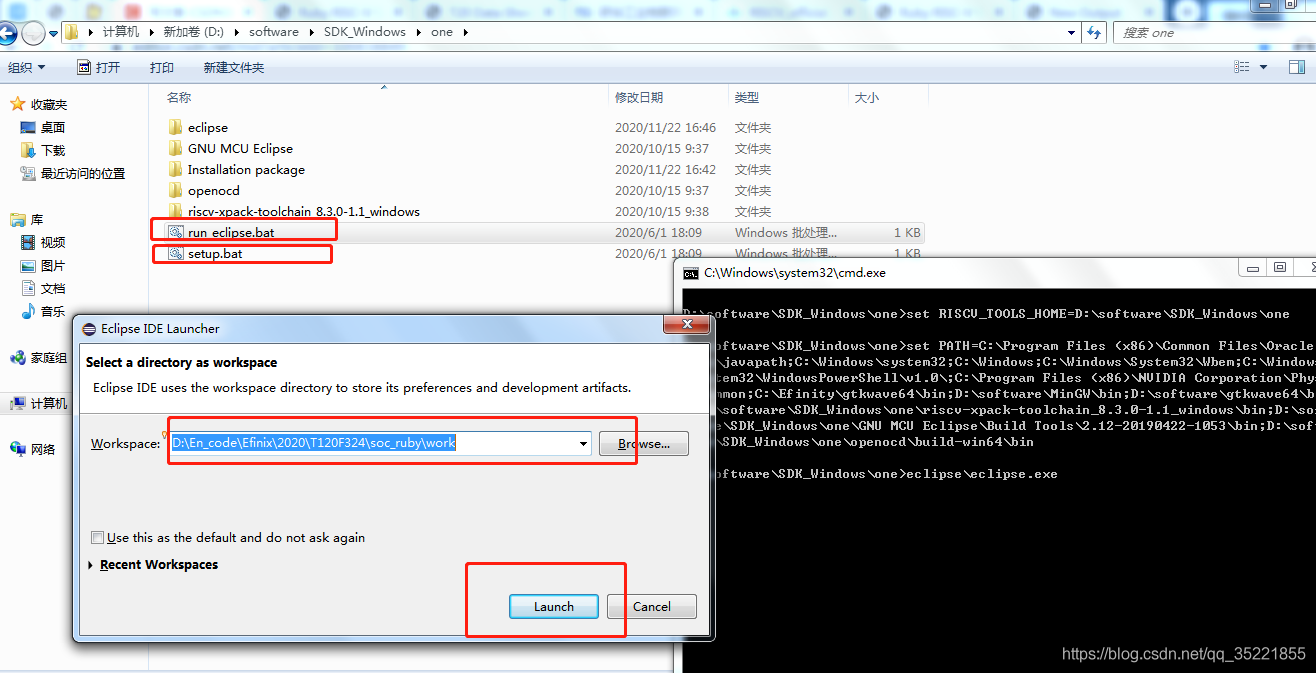

1.启动Eclipse软件

a.打开Eclipse软件

解压上文的RISC-V SDK中任意一个版本到没有中文,标点以及特殊字符的路径内。,双击 setup.bat 设置系统环境变量后,双击 run_eclipse.bat;设置Workspace(不能有中文标定特殊字符等),点击Launch建立。

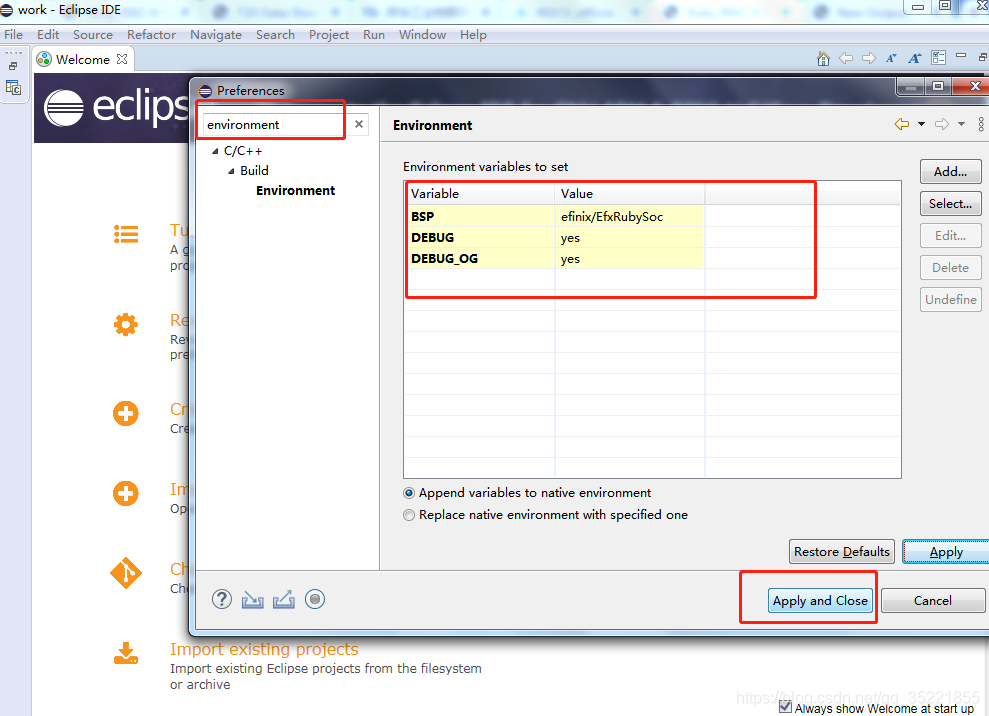

b. 设置work工作区环境变量。

选择菜单栏“Window > Preferences 打开 Environment 窗口.

输入以下环境变量定义。

变量名 值 描述

BSP efinix/EfxRubySoc Board-specific package for the SoC

DEBUG yes Enables or disables debug mode.no: Debuggingis turned off . yes: Debugging is enabled

DEBUG_OG yes Enables or disables optimization duringdebugging.Use an uppercase letter O not a zero.

备注:如果使用的是其他的RiscV内核,BSP的值可以替换成efinix/EfxOpalSoc,efinix/EfxJadeSoc等我们实际的路径。

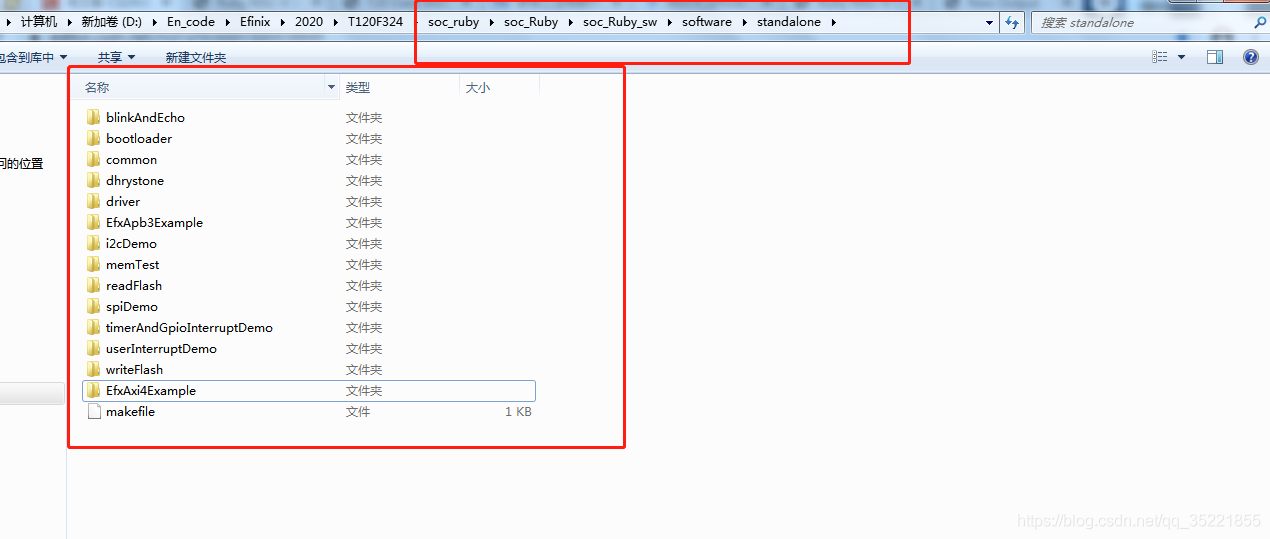

2. 创建新的工程

在soc_Ruby\soc_Ruby_sw\software\standalone文件夹目录下我们能看到有以下例程方便我们学习和调试,我们选择 EfxAxi4Example进行调试:

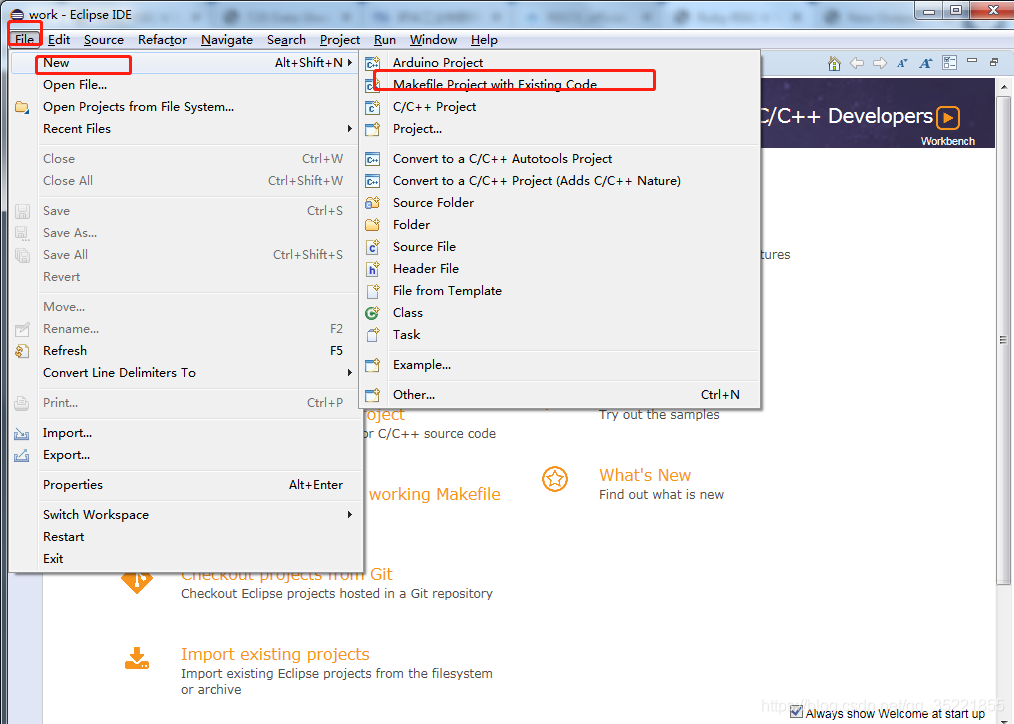

a.

选择Eclipse的File菜单,选择New里面的Makefile Project with Existing Code。

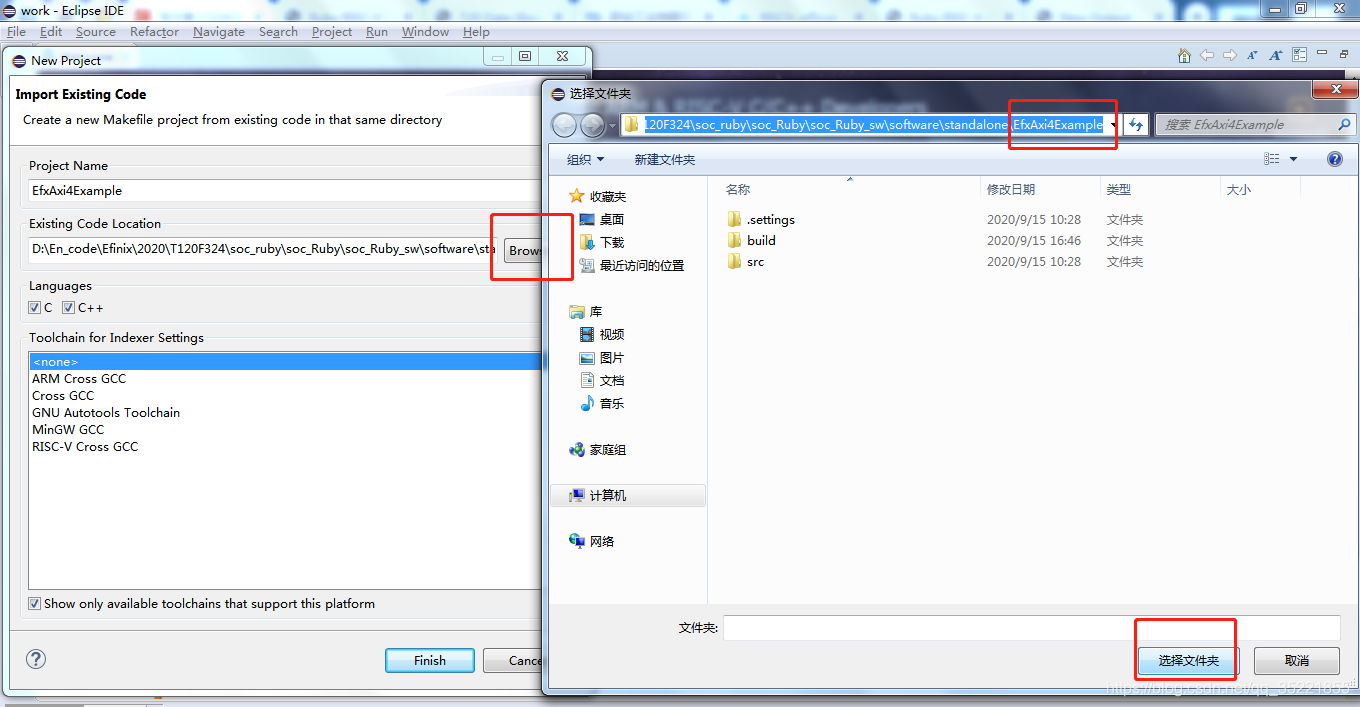

b.

在Existing Code Location 单击Browse,选择…\software\standalone\EfxAxi4Example文件夹;

在 Toolchain for Indexer Settings 目录内,选择**<none>** 后finish。

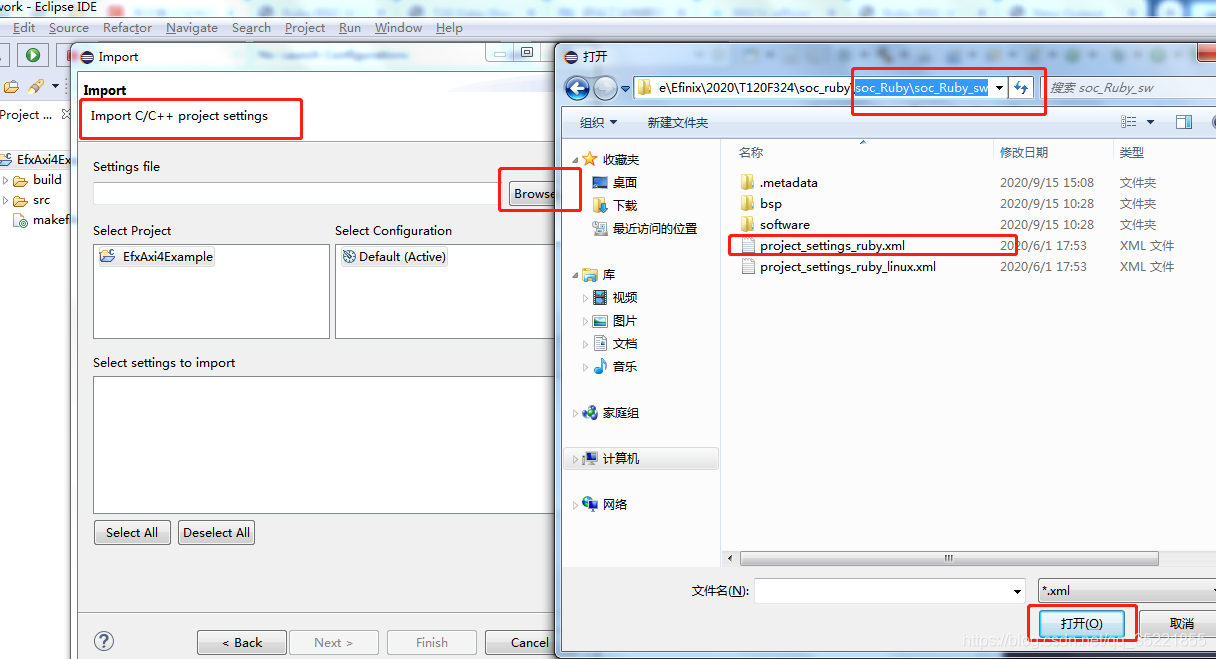

c. 设置项目约束文件

在File菜单栏下点击Import,选择C/C++ 下面的 C/C++ > C/C++ Project Settings。选择project_settings_ruby.xml文件。

d.

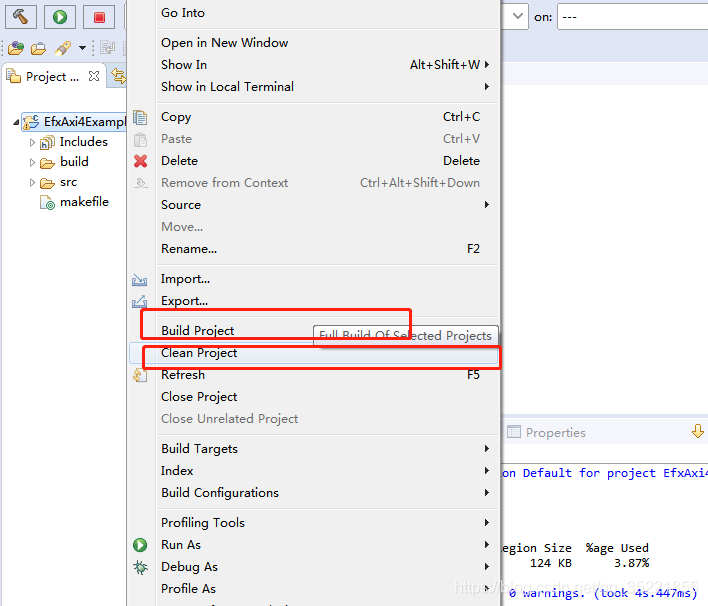

右击EfxAxi4Example项目,先后clean,build项目。build的过程会将所有的引索添加到当前的工程中。

3. 用OpenOCD调试

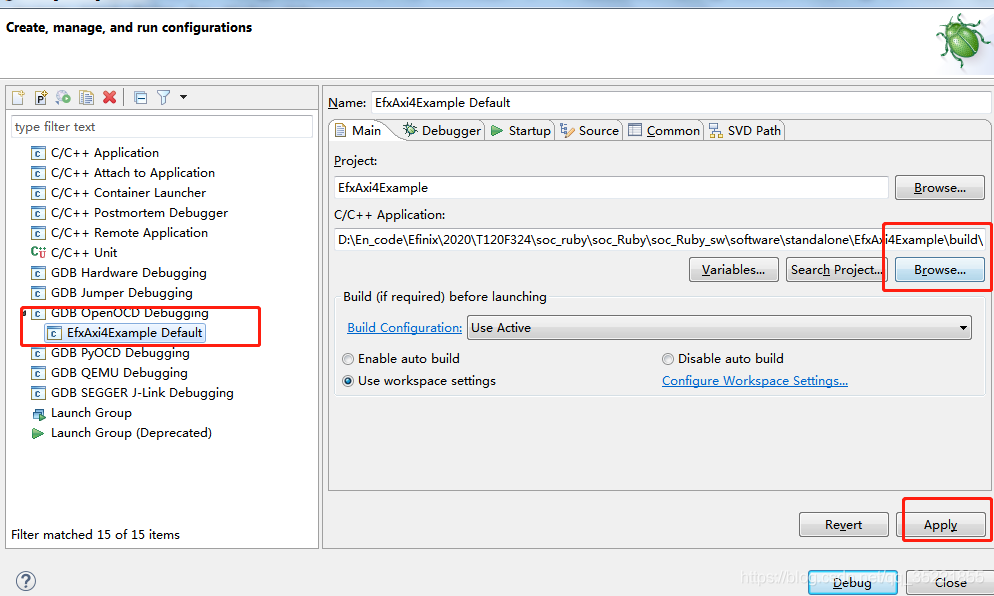

a. 创建debug配置

右击EfxAxi4Example项目,选择 Debug As里面的 Debug Configurations;双击 GDB OpenOCD Debugging 命名一个新工程EfxAxi4ExampleDefault ;

在 C/C++ Application 选项框里选择…soc_Ruby_sw\software\standalone\EfxAxi4Example\build\EfxAxiExample.elf文件,apply保存;

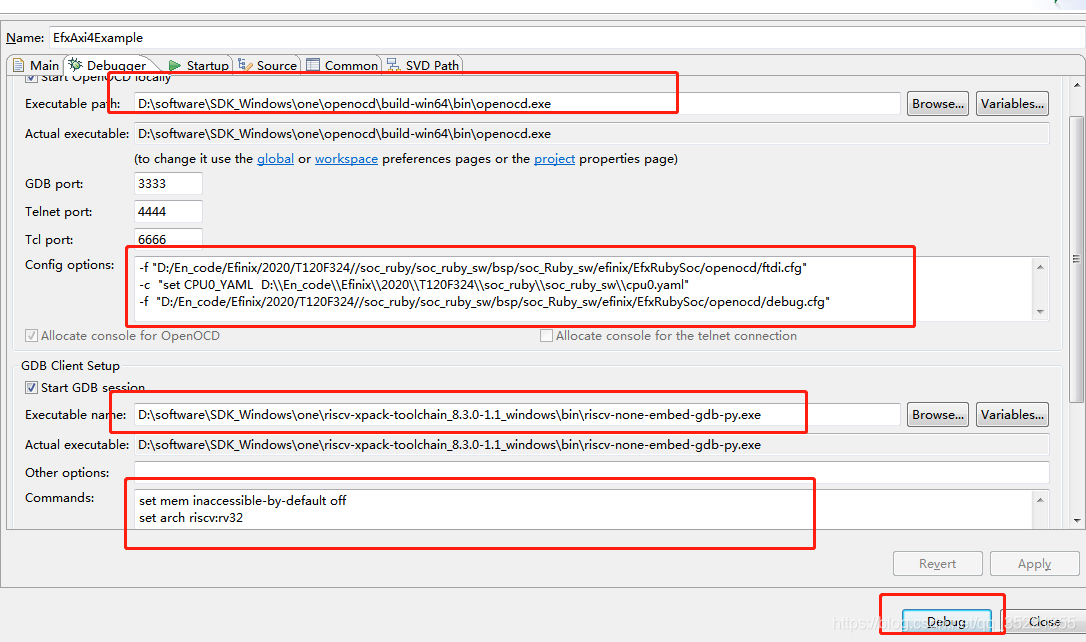

b.设置debug环境

1. 在 OpenOCDSetup 选项框里选择SDK包里面的openocd软件的路径,我一般会选择绝对路径,只是为了方便copy:

D:\software\SDK_Windows\one\openocd\build-win64\bin\openocd.exe

2. 在GDB ClientSetup 选项框里选择 SDK包里面的GDB软件的路径:

D:\software\SDK_Windows\one\riscv-xpack-toolchain_8.3.0-1.1_windows\bin\riscv-none-embed-gdb.exe

3. 在 Configoptions 选项框里输入FTDI设备和 RISC-VCPU的设置,不同的路径根据实际情况更改:

-f“D:/En_code/Efinix/2020/T120F324/soc_ruby/soc_ruby_sw/bsp/soc_Ruby_sw/efinix/EfxRubySoc/openocd/ftdi.cfg”

-c “set CPU0_YAMLD:\\En_code\\Efinix\\2020\\T120F324\\soc_ruby\\soc_ruby_sw\\cpu0.yaml”

-f “D:/En_code/Efinix/2020/T120F324//soc_ruby/soc_ruby_sw/bsp/soc_Ruby_sw/efinix/EfxRubySoc/openocd/debug.cfg”

4. 在 Commands 选项框里输入调试命令:

set mem inaccessible-by-default off

set arch riscv:rv32

set remotetimeout 250

c. Debugging

单击Resume 按钮或按F8继续代码操作,现象是开发板所有LED灯连续一致地闪烁。

单击单步执行(F6)对一条源指令执行单步执行;单击单步执行(F5)进入下一个调用的函数;

单击Step Return(F7)执行当前函数的单步操作;单击“寄存器”选项卡以检查处理器的寄存器;

单击内存选项卡以检查内存内容;单击“挂起”按钮停止代码操作;

完成调试后,单击“终止”断开OpenOCD调试器的连接。

四、OpenOcd烧录固化

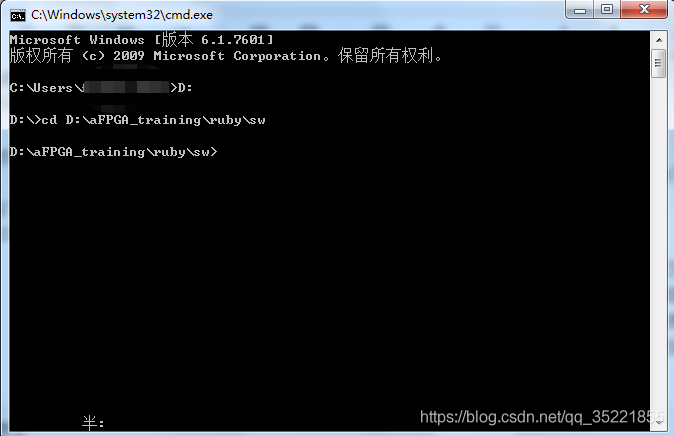

1. 打开一个cmd窗口1,切换到要烧写的bin文件目录下;

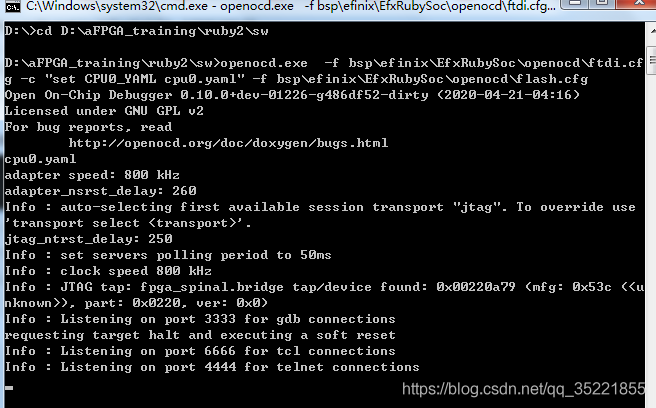

2.键入以下代码

openocd.exe -f bsp\efinix\EfxRubySoc\openocd\ftdi.cfg

-c "set CPU0_YAML cpu0.yaml"

-f bsp\efinix\EfxRubySoc\openocd\flash.cfg

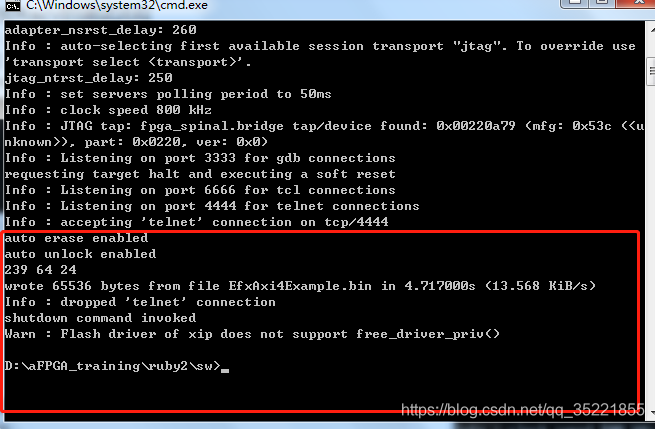

实际路径根据自己的项目修改, 会打印如下信息

备注:openocd是编译器 ,需要把opened. exe放到windows system32目录下,否则会报错找不到openocd路径。

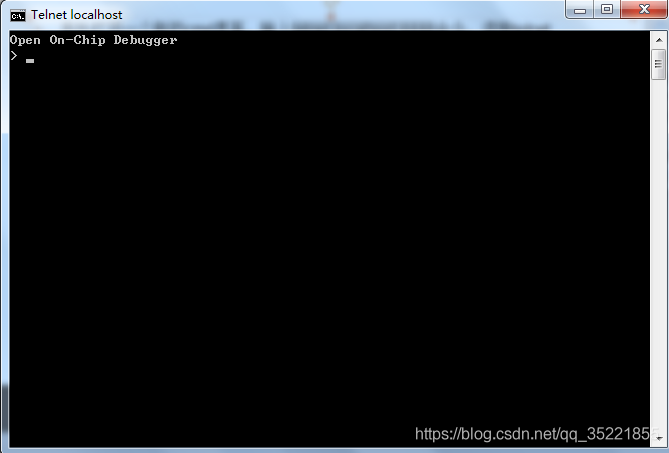

3. 再打开一个新的CMD窗口2,打开4444本地主机端口 ,键入以下命令;

telnet localhost 4444

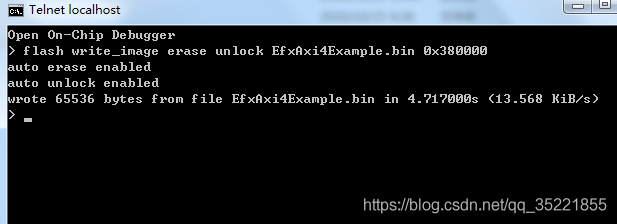

会出现如下对话框:

备注:如果本地telnet没有打开,会报错,自行百度打开。

4. 烧写用户自定义bin文件,键入以下命令

flash write_image erase unlock<filename>.bin 0x380000

例如

flash write_image erase unlockEfxAxi4Example.bin 0x380000

打印如下信息即烧录成功:

5. 此时即可关闭CMD窗口2 ;切回CMD窗口1,按下 Ctrl+C 关闭提示openocd;板子板子再次上电即可检验是否固话成功。

五、Efinity烧录固化

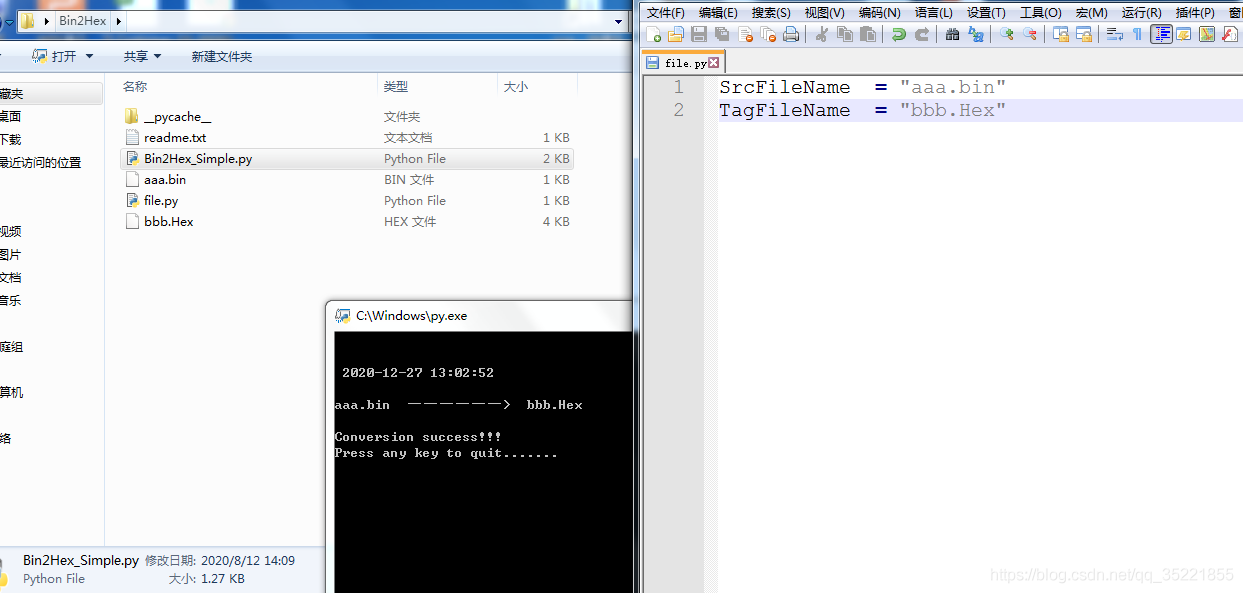

1.将eclipse编译完生成的.bin文件放在运行bin2hex.py文件文件夹目录下,根据readme提示修改file.py文件后,然后生成对应的hex文件:

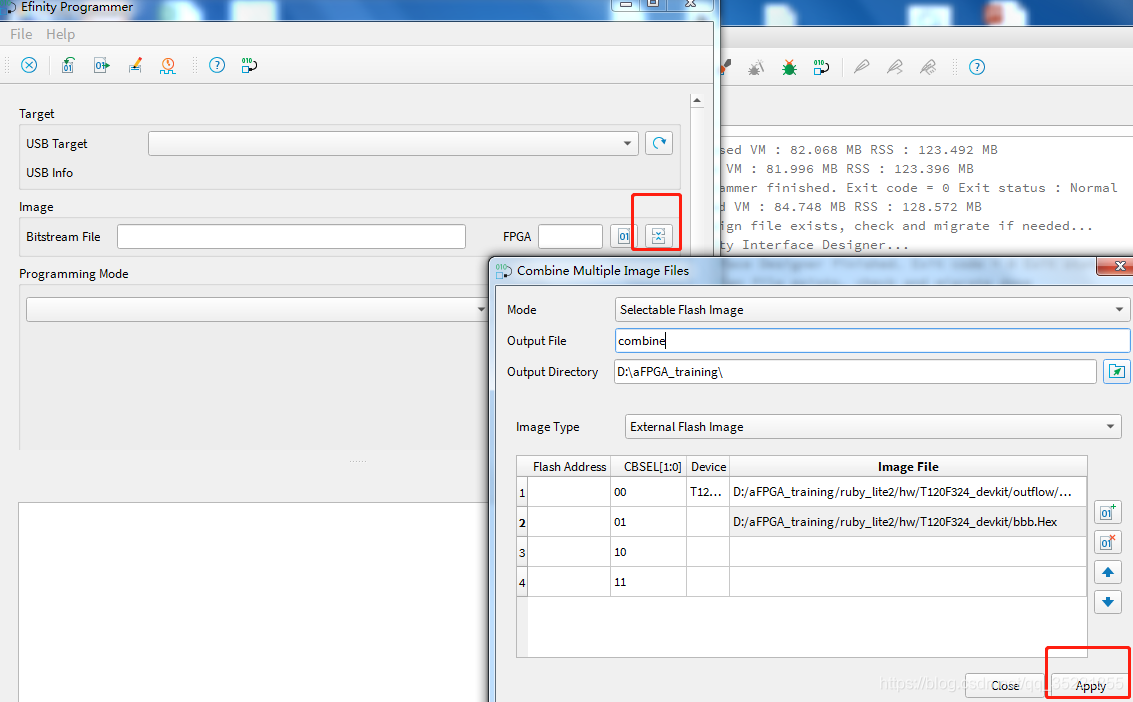

2.使用Efinity的programmer工具的combine multi image files 功能,合并FPGA程序和软件程序,并可以在Flash address处自定义烧写的flash地址:

3.烧写完成以后Programmer会提示校验错误,这是因为转换以后的hex文件并不是真正的FPGA bitstream,可以忽略掉这个错误提示。

五、总结

以上就是RiscV环境搭建的全过程,环境是比较复杂,在实操的过程中经常会出现因为路径不对,大小写命名错误,设备选择不对出现的错误,甚至有因为电脑性能不够而跑崩的情况,可以参考ug和ds手册来进行判断。

针对会出现的错误我也会更新出来的。

此链接4个视频详细介绍了调试riscv内核的流程 https://pan.baidu.com/s/1ePDWgaDgZ7wGmUFD2UNCkA 提取码:nihh

————————————————

版权声明:本文为CSDN博主「Fol屃」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_35221855/article/details/109838849

关于易灵思

易灵思® 是可编程产品的创新者,通过该公司的Trion™ FPGA产品平台推动了人工智能及边缘计算的未来发展。Trion FPGA的核心是易灵思的突破性Quantum™ FPGA技术,与传统FPGA技术相比,它具有4倍的功耗-性能-面积优势。Trion FPGA提供4K至120K逻辑单元,面积小,功耗低,适合大批量生产。第二代产品Trion TitaniumFPGA 更将其推向新的高度,16nm工艺,具有增强的“Quantum 计算架构”,可提供更低的功耗和更高的性能。TitaniumFPGA的密度从25K到500K 逻辑单元,可以随时助您攻克下一个设计挑战。我们的Efinity®集成开发环境提供从RTL到比特流的完整FPGA设计流程。凭借其功耗-性能-面积优势,Trion FPGA可满足定制逻辑,计算加速,机器学习和深度学习等应用需求。通过Efinity,我们的客户可以将FPGA平台或整个系统无缝地迁移到Quantum ASIC中, 以进行超大批量的生产。

易灵思® 是可编程产品的创新者,通过该公司的Trion™ FPGA产品平台推动了人工智能及边缘计算的未来发展。Trion FPGA的核心是易灵思的突破性Quantum™ FPGA技术,与传统FPGA技术相比,它具有4倍的功耗-性能-面积优势。Trion FPGA提供4K至120K逻辑单元,面积小,功耗低,适合大批量生产。第二代产品Trion TitaniumFPGA 更将其推向新的高度,16nm工艺,具有增强的“Quantum 计算架构”,可提供更低的功耗和更高的性能。TitaniumFPGA的密度从25K到500K 逻辑单元,可以随时助您攻克下一个设计挑战。我们的Efinity®集成开发环境提供从RTL到比特流的完整FPGA设计流程。凭借其功耗-性能-面积优势,Trion FPGA可满足定制逻辑,计算加速,机器学习和深度学习等应用需求。通过Efinity,我们的客户可以将FPGA平台或整个系统无缝地迁移到Quantum ASIC中, 以进行超大批量的生产。

有关更多信息,请浏览:https://www.elitestek.com

/5

/5