最近有些项目中有涉及到DDR应用,虽然比较简单,都是单颗粒形式,不像复杂的多颗粒形式,但还是打算总结一下,本篇就先介绍基础知识。

1. DDRx简介

DDR是DDR SDRAM的简称,只是人们习惯了称之为DDR,全称为Double Data Rate Synchronous Dynamic Random Access Memory,中文名为:双倍速率同步动态随机存储器,同步是指需要时钟。

本人在实际工作中用的最多的内存颗粒还是DDR3和LPDDR3,闪存颗粒则是NAND和EMMC,其他的DDR也只是作为了解居多。DDRx颗粒的常见部分参数如表1所示。

表1

1.1 SSTL电平

LVTTL电平

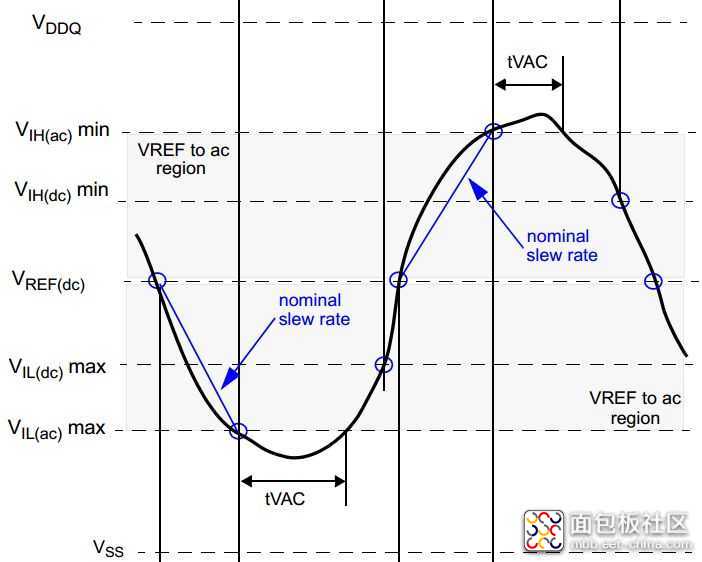

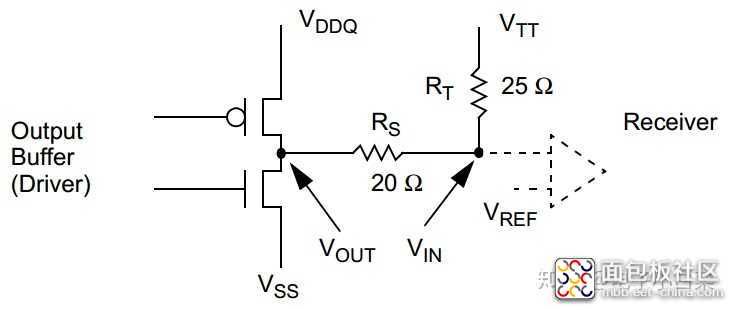

为单端信号,而SSTL电平本质上是差分对,其实现机制是将信号与参考电平Vref组成差分对进行比较,如图1所示,VIH和VIL各有一个交流参数AC和直流参数DC,信号第一次越过AC门限的时刻,作为时序计算的参考点,此后只要信号保持DC门限内,逻辑状态保持不变,这种设计减小了噪声、振铃等对于信号质量的影响。在SSTL_18中,规定了端接电阻上拉到VTT电源,如图2所示。在典型应用中,VREF和VTT等于VDDQ/2,因此接收端的电压同时取决于驱动器、端接电阻RT和端接电压VTT,驱动器的输出电阻Ron一般不会大于21R。这个端接电阻最主要的作用是提高信号完整性,特别是在一驱多的Fly-by拓扑中,此外还能增强驱动能力,当DDR颗粒较少时(1颗或2颗时,可咨询DDR原厂确定),VTT可以不用。另外,当驱动端电平分别为高或低时,电流流向相反,因此VTT电源需要具有提供电流和吸收电流的能力,不能使用普通的电源。

图1

图2

1.2 HSUL电平

HSUL-12电平主要用于点到点的无端接总线拓扑结构,不需要外部串行或者并行匹配电阻,降低了端接功耗,LPDDR3使用的就是该种电平。

1.3 POD电平

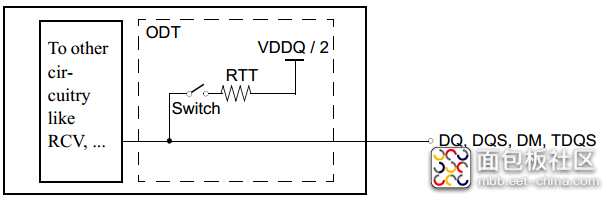

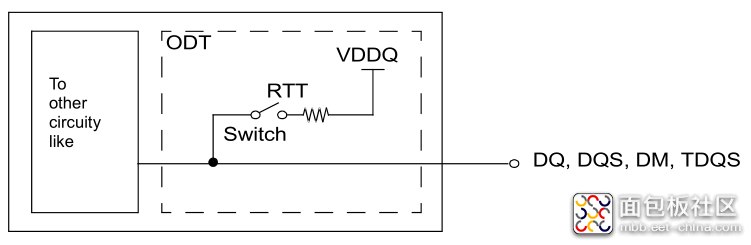

POD是伪漏极开路电平,其内部端接上拉到VDDQ,而SSTL内部是上拉到VDDQ/2,分别如图3和图4所示。因此,当驱动端输出高电平时,由于驱动端和接收端端接电压均为VDDQ,因此没有电流流动,降低了功耗;驱动端输出低电平时,POD由于上拉电压高,功耗稍大于SSTL。正因此,DDR4多了一个DBI功能,即数据总线翻转,当一个字节里0的位数大于1的位数时,可以将0和1反转,以降低功耗。

由于POD的参考电平Vref大小会随着驱动强度、负载、传输线特性等不同而改变,因此DDR4数据信号的参考电平Vref DQ是由芯片内部自己产生的,没有外接该电平的管脚,只有地址信号的参考电平管脚VrefCA。POD的VrefDQ通过控制寄存器设置值由芯片自行优化调整,称为VrefDQ Training。

图3

图4

另外需要提及的一点是,LPDDR3的内部端接ODT也是上拉到VDDQ。

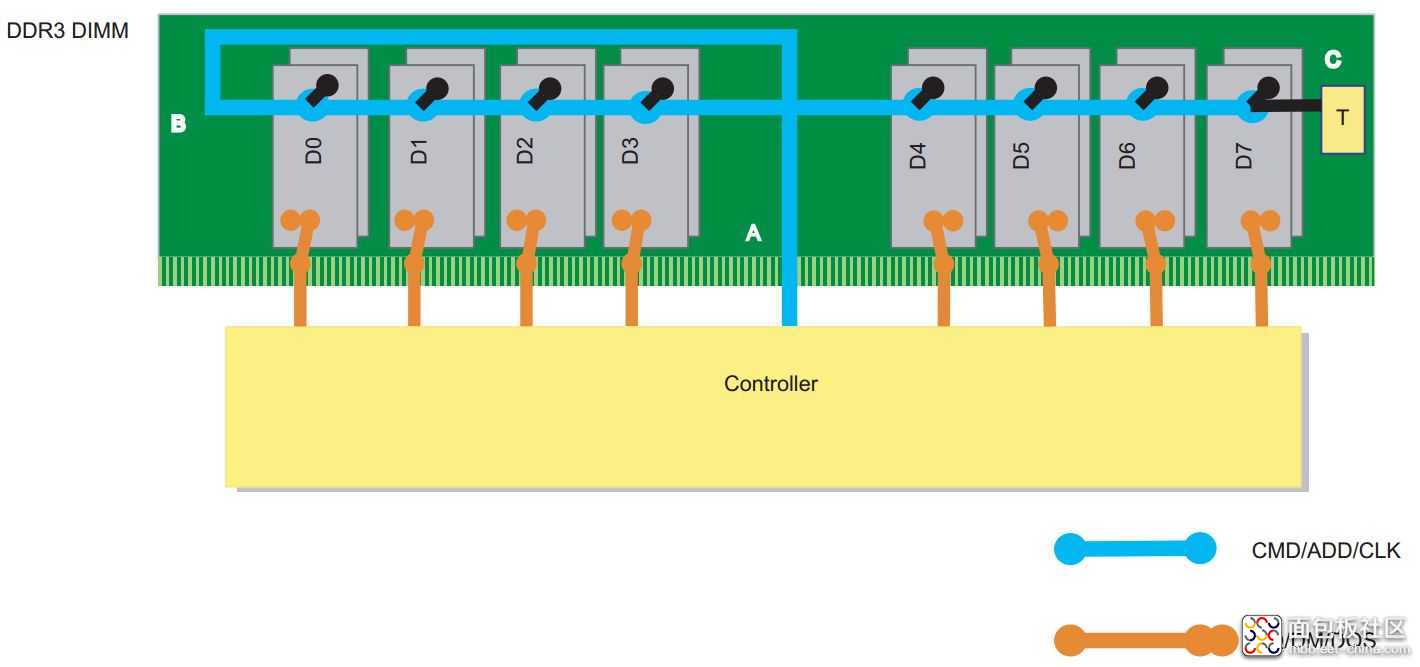

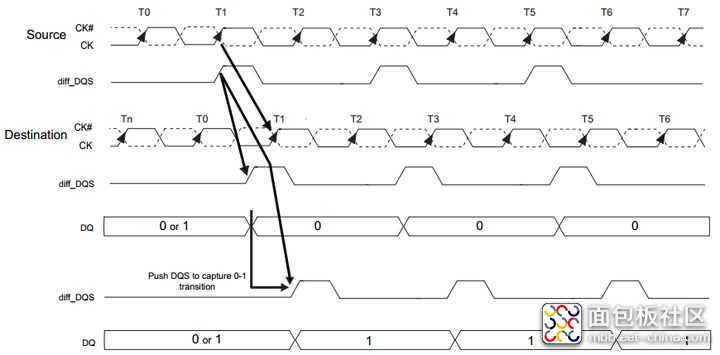

1.4 Writing Leveling

为了更好的信号完整性,DDR3内存模块对命令、地址、控制和时钟信号线采用了fly-by拓扑结构(一种特殊的菊花链),如图5所示。该拓扑结构能够减小stub的数量和长度,但同时也会引起各内存颗粒CLK和DQS信号之间的飞行时间偏差,因此,DDR3颗粒引入了Writing Leveling功能,如果DDR控制器同时也支持该功能的话(并非所有控制器都支持该功能),就可以补偿CLK和DQS之间的飞行时间偏差。Write Leveling的本质目的是使DQS信号的上升沿在到达DDR颗粒时能够和CLK时钟信号对齐。DDR控制器通过不断地调整DQS的发送延时,DDR颗粒则在DQS信号的上升沿采样CLK时钟信号,并通过DQ数据信号将CLK时钟状态反馈回给DDR控制器,直到DQ信号从0变成1,此时就使CLK和DQS对齐了,确定DQS延时值,完成调整过程,如图6所示。

图5

图6

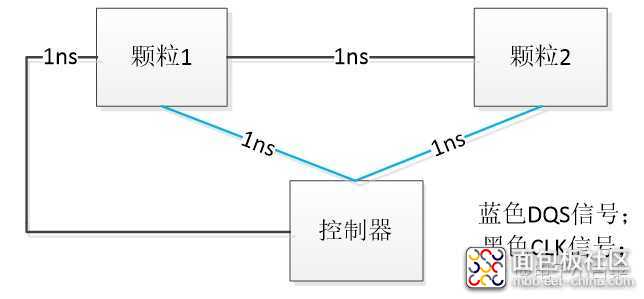

上述调整过程的文字描述可能不是很直观,下面通过一个简单的例子来说明,如图7所示,颗粒1的CLK飞行时间为1ns,颗粒2的CLK飞行时间为2ns,颗粒1和颗粒2的DQS飞行时间均为1ns。如果不进行Write Leveling调整,颗粒2的CLK信号和DQS信号的飞行时间偏差为1ns,没有对齐。经过调整后,控制器在发送颗粒1的DQS后,延时1ns再发送颗粒2的DQS,则颗粒1在1ns后收到对齐的DQS和CLK,颗粒2在2ns后收到对齐的DQS和CLK,从而满足了时序关系。

图7

2. DDRx引脚说明

2.1 引脚功能

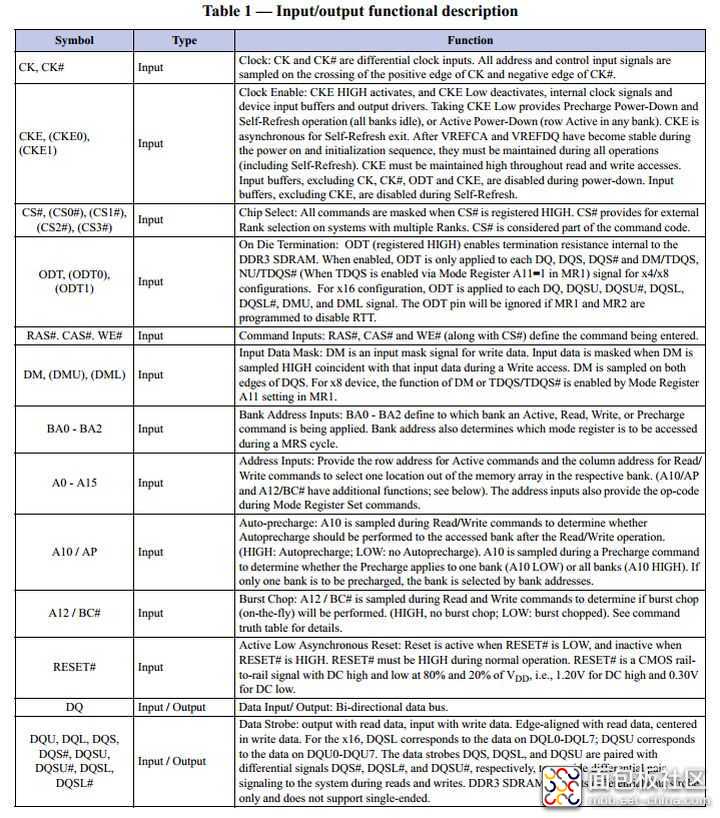

DDRx是典型的源同步时钟(另一种时钟系统是共同时钟),其信号引脚主要有差分时钟CK/CK#、时钟使能CKE、片选CS#、行地址选通RAS#、列地址选通CAS#、写使能WE#、BANK地址选通BA0~BAn、地址A0~An、数据DQ0~DQn、数据选通DQS/DQS#、数据掩码DM。不同一代的DDR/DDR2/DDR3的引脚有所不同,以下几幅图分别是DDR3,LPDDR3和DDR4的引脚说明。

图8 DDR3引脚说明

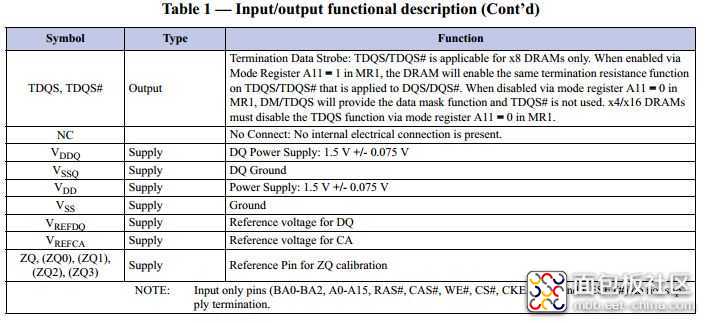

图8续 DDR3引脚说明

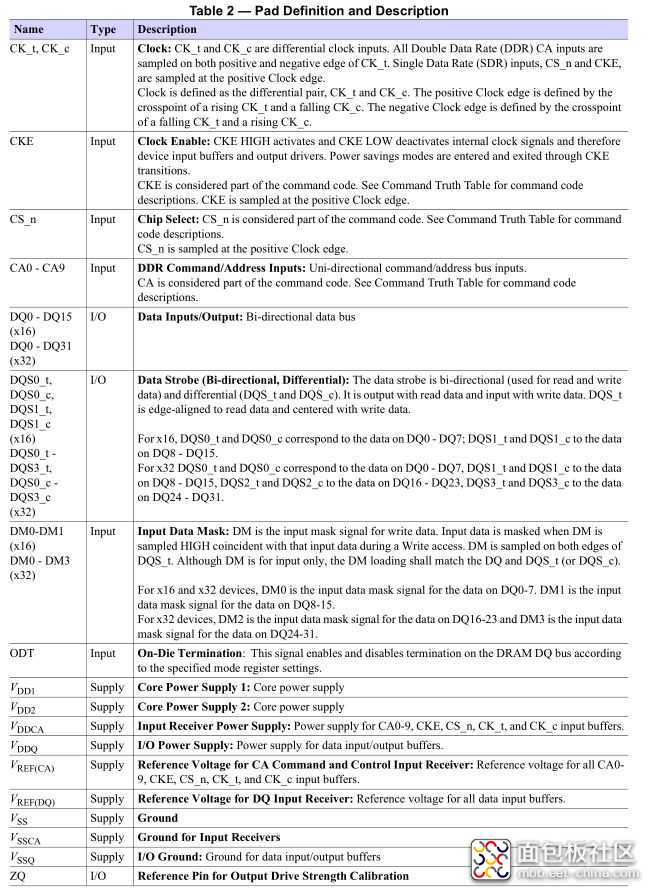

图9 LPDDR3引脚说明

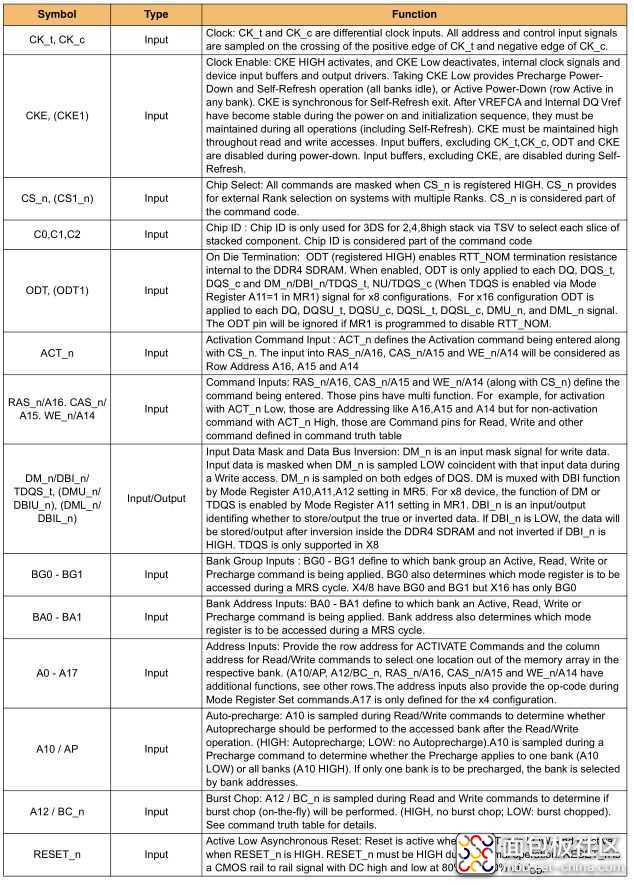

图10 DDR4引脚说明

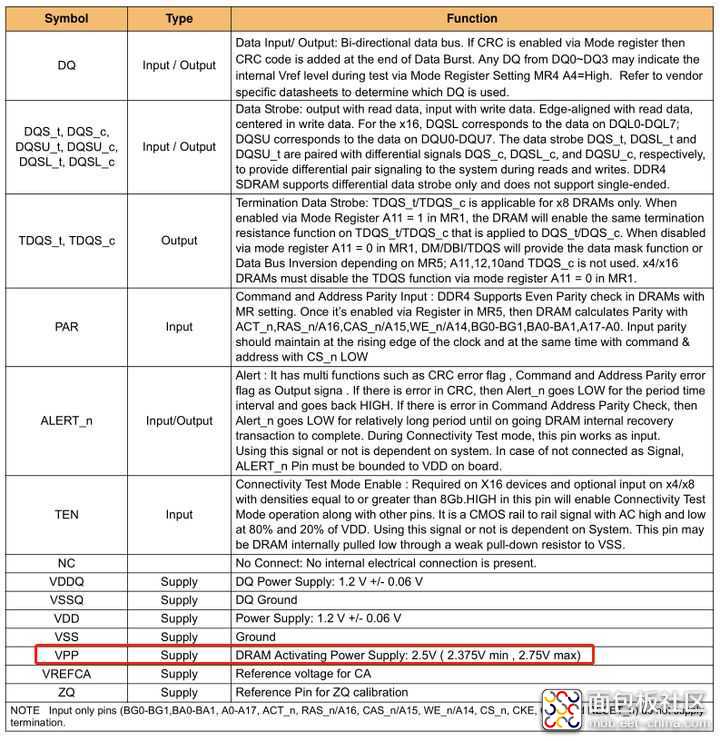

图10续 DDR4引脚说明

除了上述引脚,DDR3引入了新的引脚,RESET#复位引脚在正常运行时必须是高电平。ZQ引脚必须接一个 240 欧姆的1%高精度电阻到GND,该电阻的作用是校准内部ODT电阻值和DDR导通电阻值Ron,因为内部的电阻会随着温度而发生变化,需要校准才能保证准确的终端匹配。

DDR3的参考电压也分为2个,分别是数据信号的VREFDQ和地址控制信号的VREFCA。

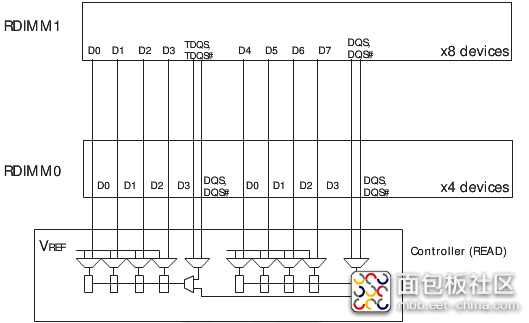

2.2 TDQS功能

另外,在DDR3的规格书里能看到TDQS/TDQS#功能,这个功能比较冷门,工作当中也没有用过,在JEDEC里描述也是一笔带过,让人迷糊。后来在镁光文档上(TN-41-06:Micron-Technical Note DDR3 Termination Data Strobe)看到解释就明白了,在此也分享一下,对电路设计来说有个了解就行,不用过于深究。该功能仅在数据位宽x8的内存颗粒上使用,主要用于简化x4位宽与x8位宽内存混合使用的存储器控制系统的设计,如图11所示,x8的内存条中每8bits需要一对DQS,而x4的内存条中每4bits需要一对DQS,即8bits的x4内存条需要两对DQS,而x8内存条只需要一对DQS,这就会造成DQS信号的负载不均衡,从而引起信号完整性(SI)问题。因此,x4内存条的其中一对DQS信号连接到x8内存条的TDQS上进行端接,并开启x8内存条的TDQS功能,从而保证负载均衡,不产生SI问题。

图11

来源: 硬核电子

/5

/5