一些随便写的科普

第一次写材料物理,从小就没学好,一边学一边写的dbq(我知道很复杂,因为我是从头到尾到一些中段(末端系列分支是真的多,写不得,写出来没个100w字出不来的)

光刻的基本流程

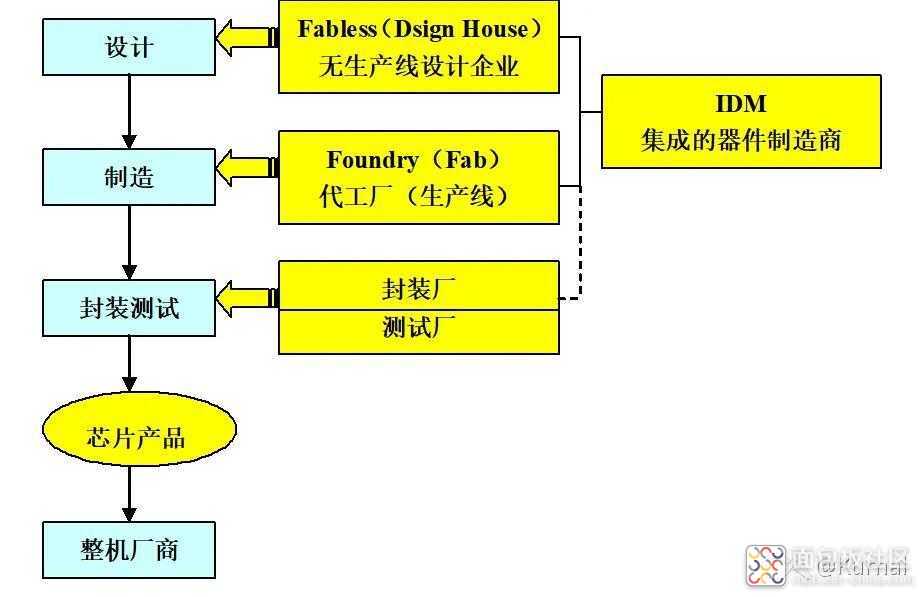

其实就基本3个大类:IC设计,IC制造,IC封测

IC设计,首先是电路设计(今天先单纯讲这个)

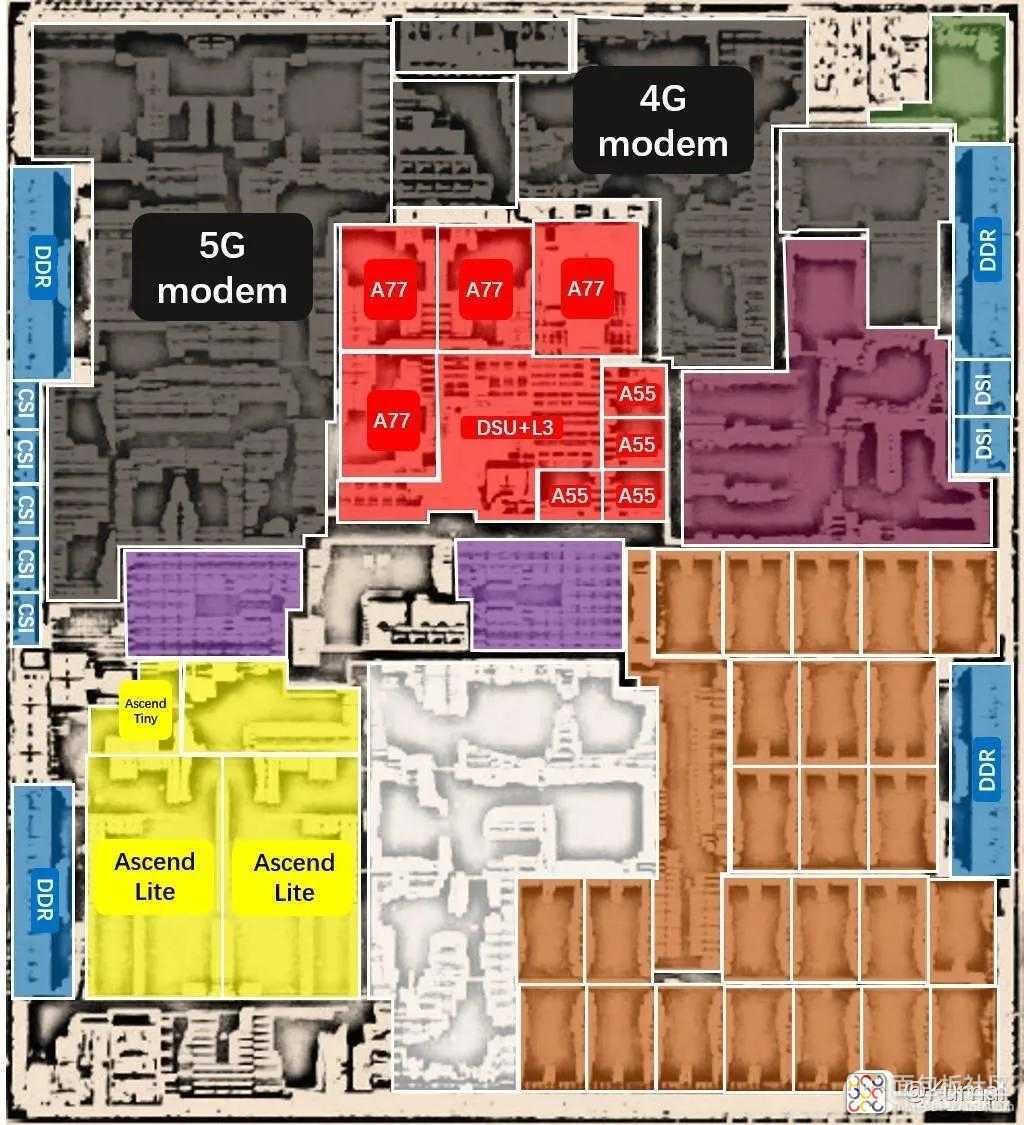

一般来说一个芯片基本有一个主要的需求,例如:处理(图像)(运算)或者单纯的dram堆叠,

然后就是其spec了,spec其实就是要求算是,例如我需要他在多少°的环境下运行,多大尺寸,运行多少频率,怎么定spec也是个学问,很复杂,但是我不是这玩意的人我也母鸡,基本就分两种,前端和后端

这个原则上好像也算(草)

说白点就是

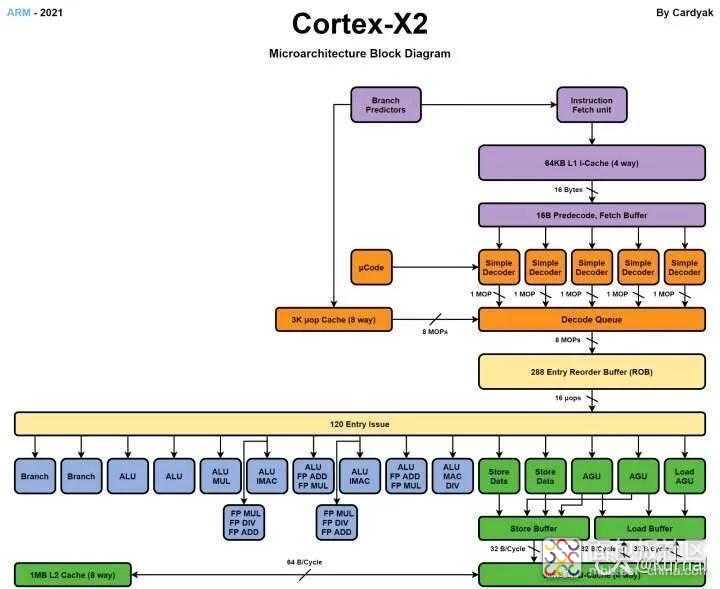

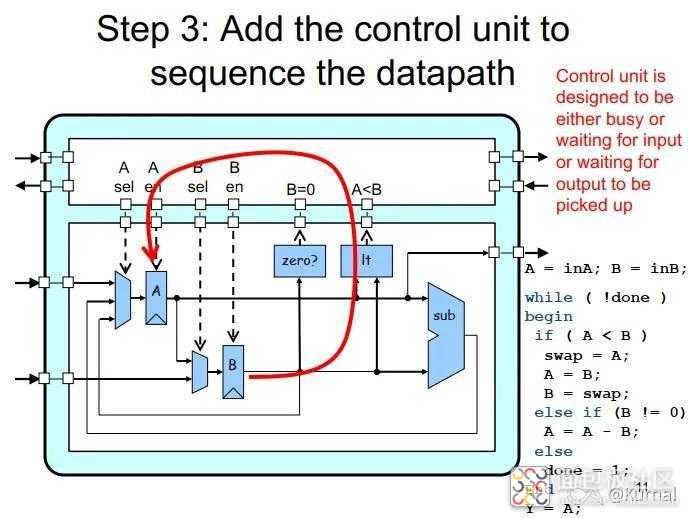

IC前端设计指逻辑设计

IC后端设计指物理设计

首先是前端了,先写一些RTL代码(例如硬件描述码),然后用一些eda软件把其synthesis,就是把软件转换成硬件能看懂的代码,生成netlist(就是网表)

后端再把这个netlist转换成实际的电路,像是画pcb一样,一些元器件摆好然后再用导线连接起来,最后设计成一个GDS file

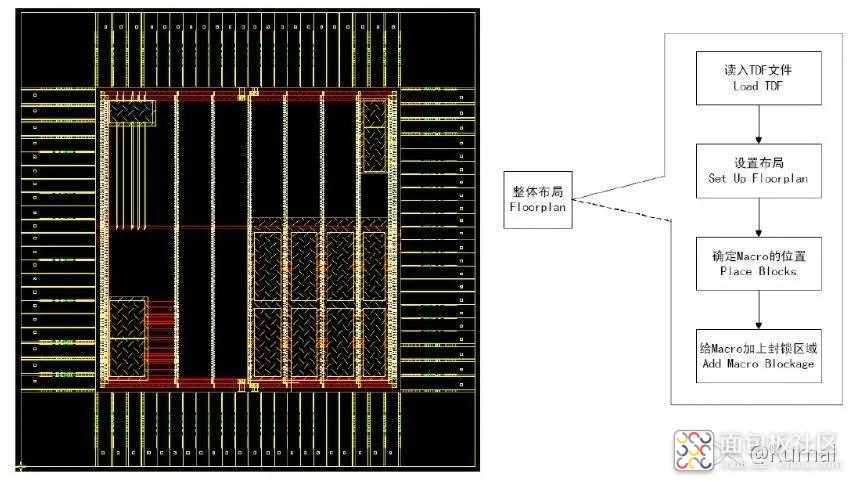

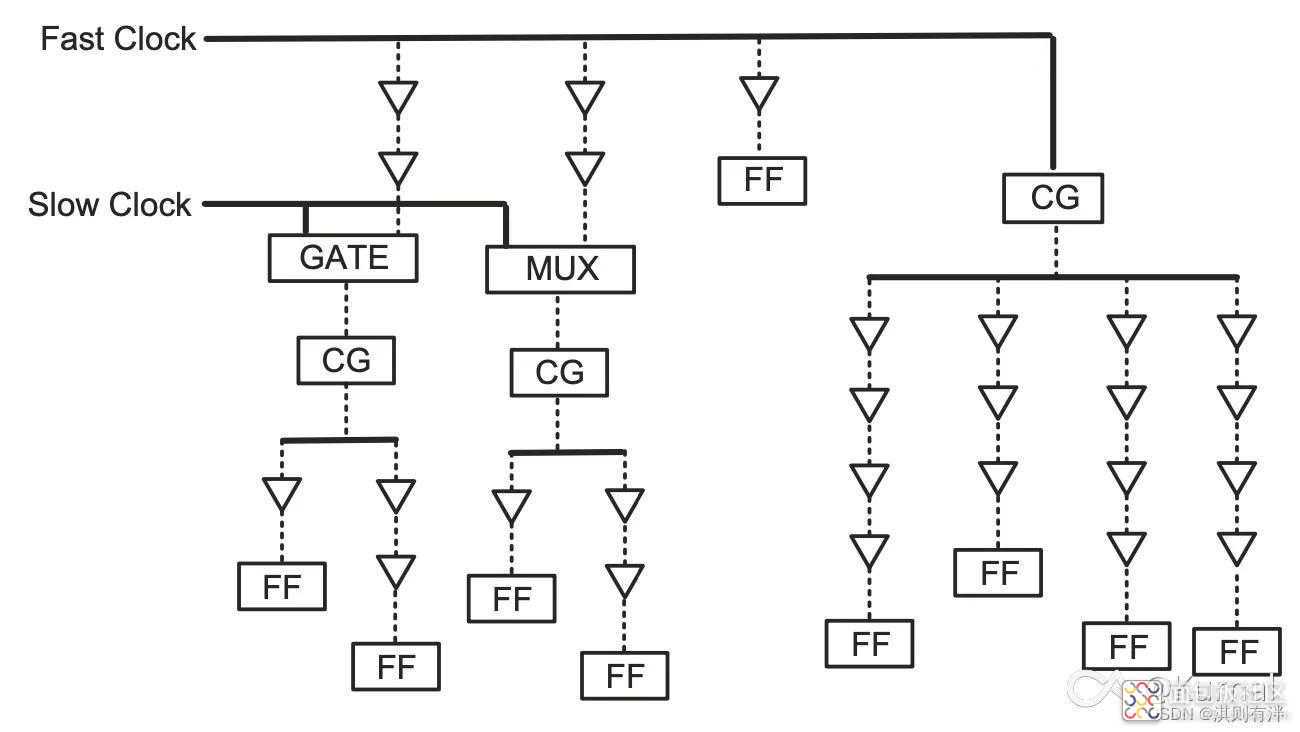

后端设计基本都靠APR,就是Auto P/R,pr分别是摆放和绕线。其设计基本分四个步骤,布局(floorplan),单元摆放(placement),CTS(时钟树综合 clock tree synthesis),绕线(route)

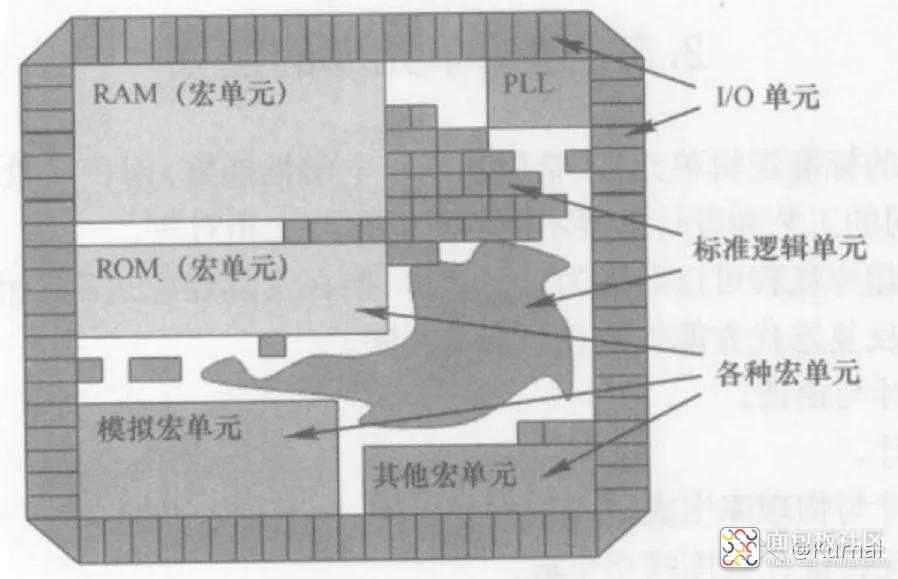

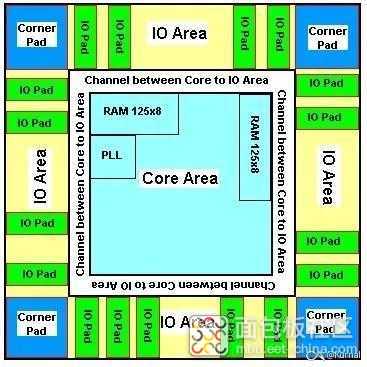

Floor:Floorplan就是布局规划,首先得确定这个芯片的面积,确定core的位置,die的尺寸,io的位置,cache的位置,bump的位置,有时候还得画powerplan,也就是电源规划,一般得在这时候画power gate,确定电压域

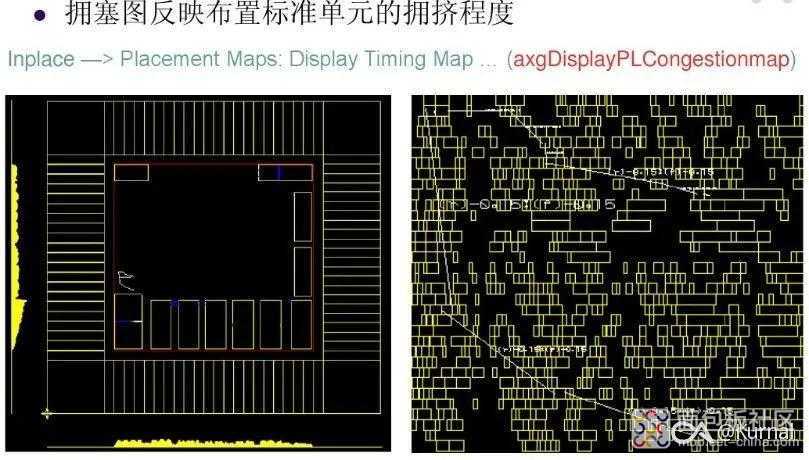

Place:然后就是Placement了,一般特指标准单元的摆放,其最重要的任务就是把一些cell库给摆放好,在place的时候,并不是单单把cell给摊开罢了,还得顺带考虑绕线,把关系紧密的给摆放在一起,又不能太过于密集

(会导致密度过高,出现拥堵,或者power不能上供电之类的奇奇怪怪的问题)

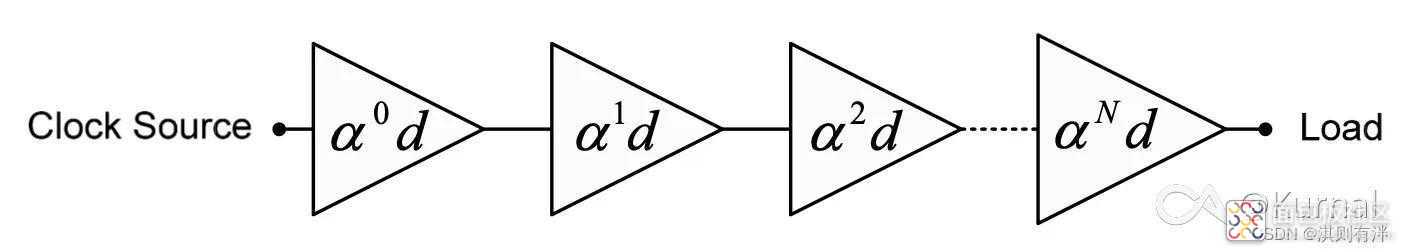

CTS:再就是时钟树综合(Clock tree synthesis(CTS)首先,一个芯片包括组合逻辑和时许逻辑,时许逻辑包括filp flop(触发器)和latch(门),还没写

然后就是最简单的绕线了,这也是最难的,简单是理解,难是操作

首先,不能有open/short,drc(设计规则检查)而且如果在floor和place中,如果在floor的时候就少给了一些绕线资源,或者说在place摆了很多cell库在一个地方导致congestion,或者说你跑stage过了,全部runing,但是有些cell与cell的timing过长,那么还得重新跑

跑一次stage,疯狂debug,一想到早期工程师纯手工pr就非常佩服

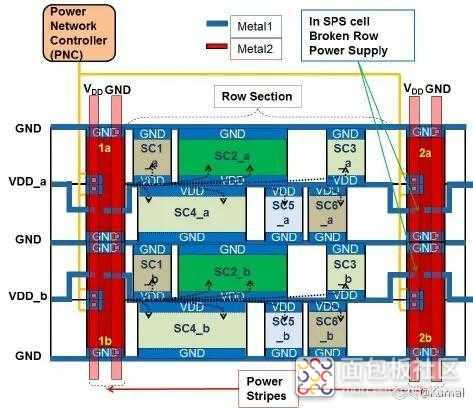

最后还得做电源层

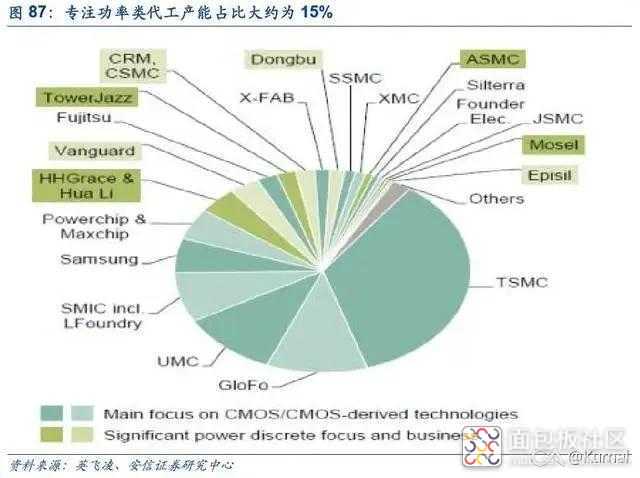

这些只是ic设计中的电路设计,做出来的东西叫做版图,GDS file,拿着GDS交给一些FAB,就是代工厂,比如tsmc啊,samsung/intel/GF之类

下面就是代工厂的事了

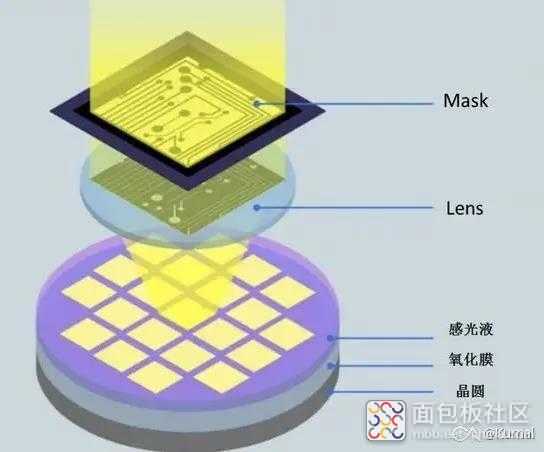

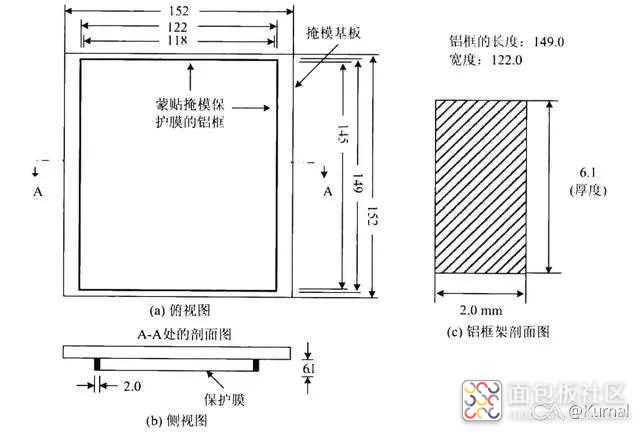

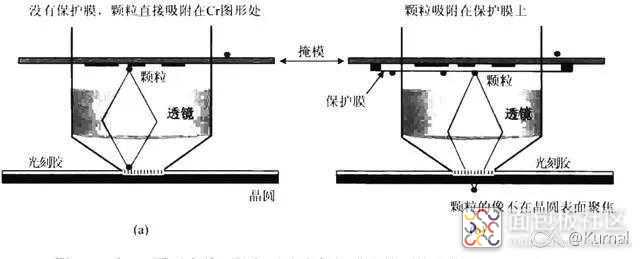

代工厂拿着GDS,做出相对于的光罩(mask)目前常用的就是mask,一种是倍缩光掩膜(reticle)一种是光掩膜(mask),当铬玻璃只能覆盖局部的Si晶圆,叫做倍缩光掩膜,基本放大5-10倍,反之,当铬玻璃图像能覆盖整个晶圆,就叫光罩(mask)

这就是reticle

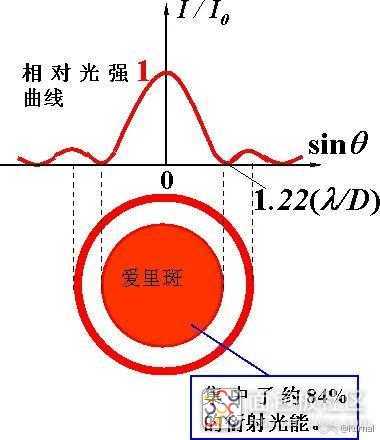

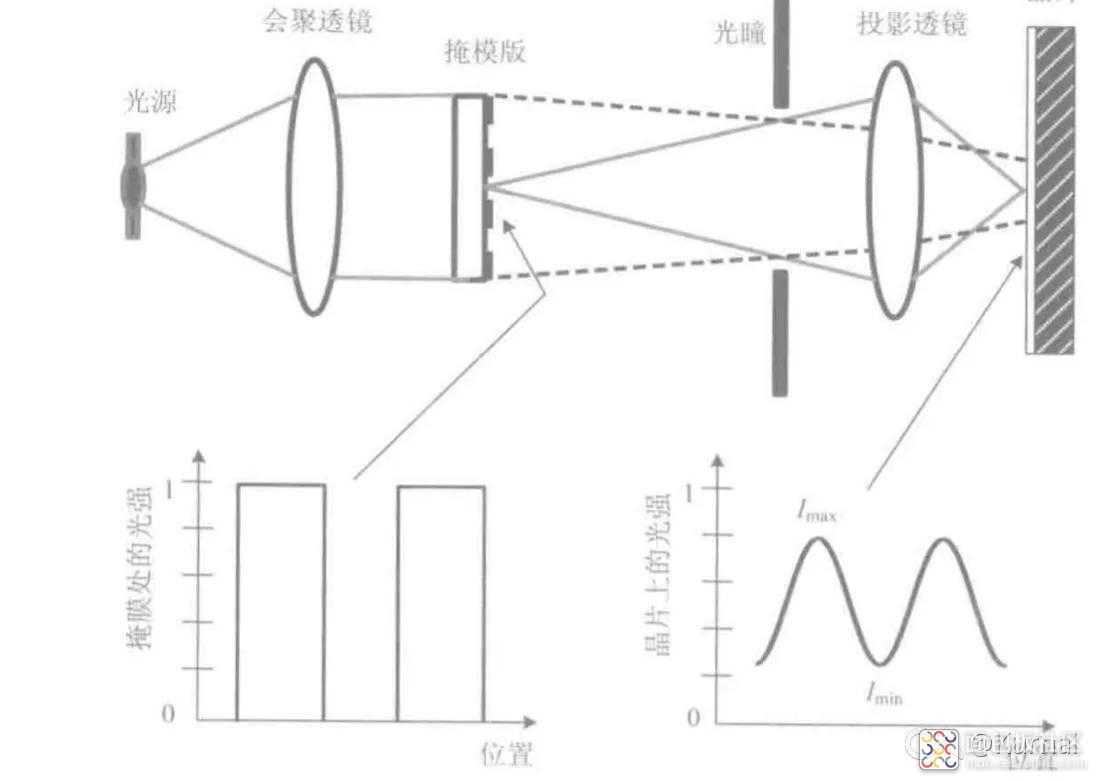

光线透过掩膜上的透光部分会发生衍射,光强会衍散到附件不透光的区域。投影透镜收集这些光线,会聚投影到晶圆表面成像。

做光罩有三大部分

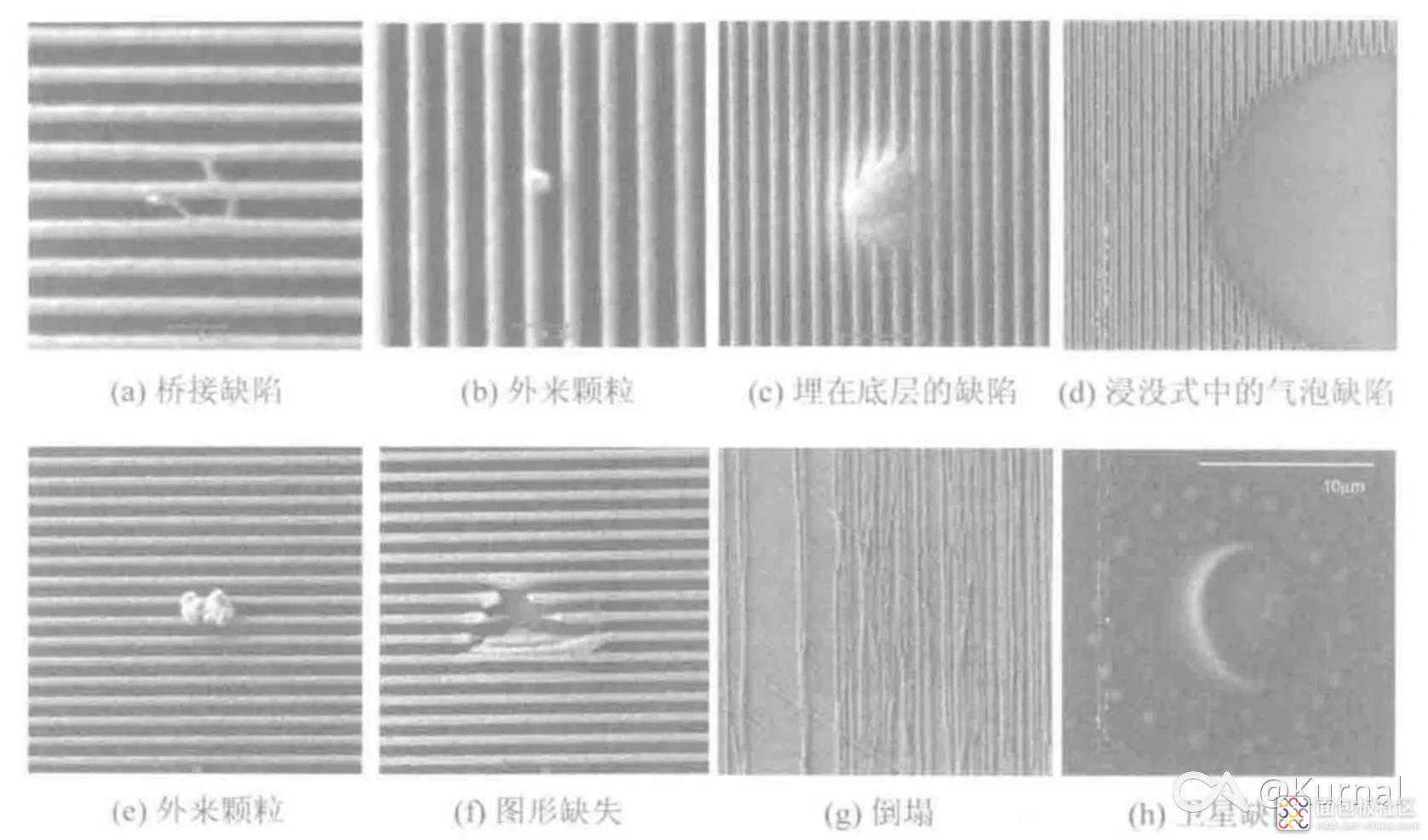

首先是图像处理,FAB拿着GDS做出处理,首先会验证你的drc符不符合,再进行排版,并在切割道上添加tab自己的测试模块,比如偏移量测量,各个层次的尺寸控制,或者说wat测试单元之类

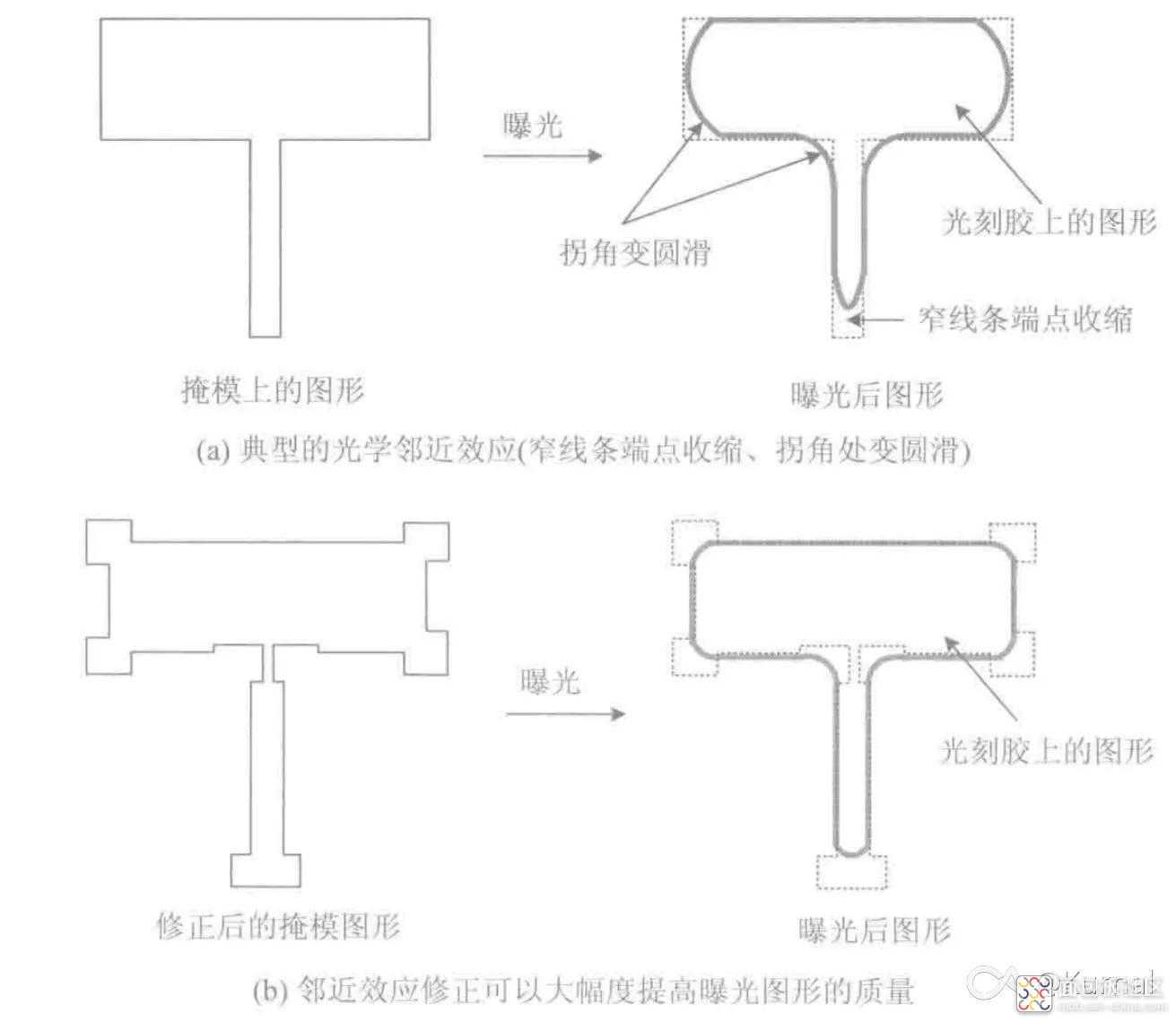

然后进行一个修正

OPC就是光学临近效应校正

OAI就是离轴照明技术,其实都是为了增加MTF值

再把这个数据提交给mask house(有些fab厂有maskhouse,如果没有就只能找mask shop去购买)输出就得到了mask这个光罩

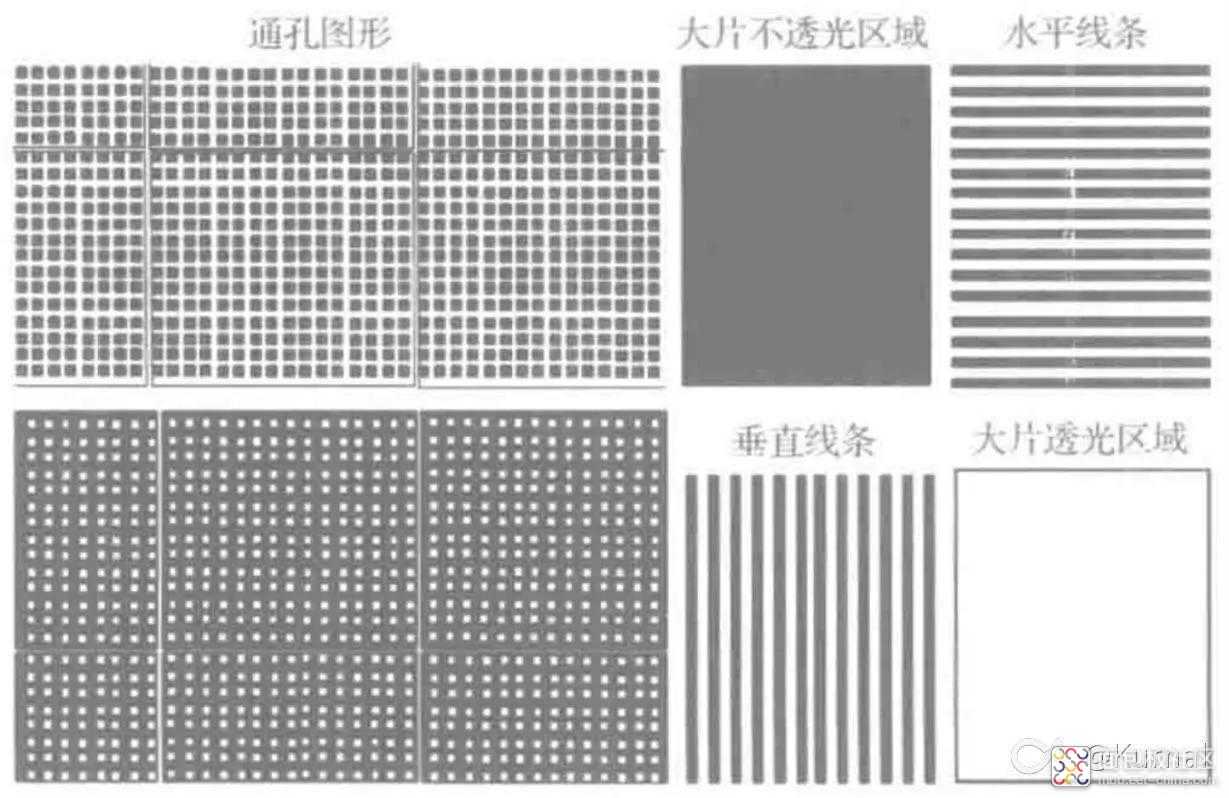

掩模版有几种

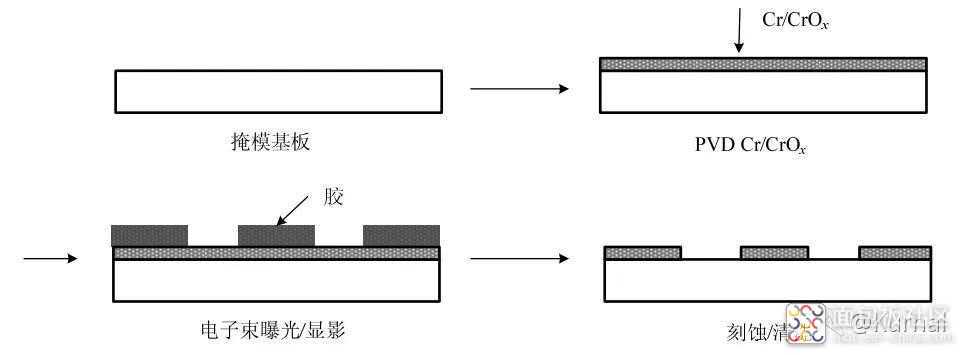

Cr双级型掩膜(binary intensity mask(BIM),双级就是透光/不透光。原材料基本都是铬基板,铬基板通常使用高纯度的石英玻璃所做成的,然后在Si板下镀一层700a的铬层,然后再在铬上一层氧化铬,作用是增加铬与玻璃的粘附力,最后在铬膜下再镀一层光刻胶

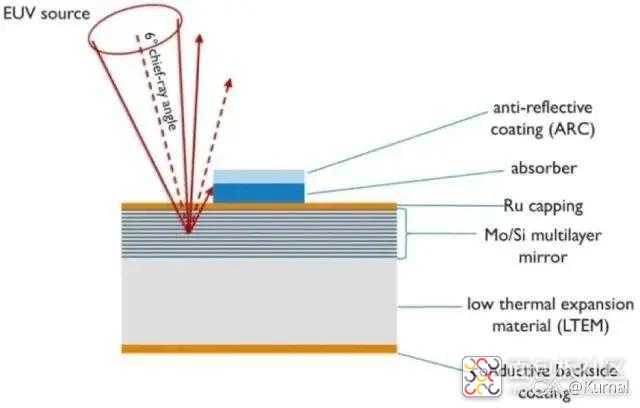

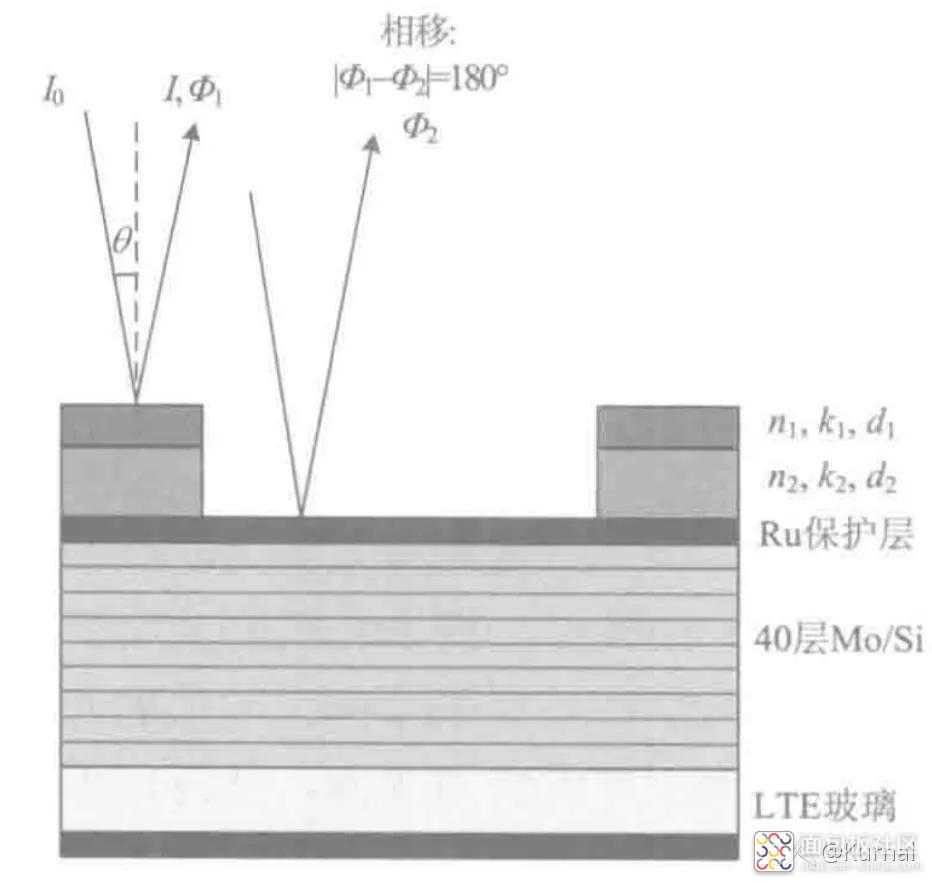

MoSi双级型掩膜(opaque MoSi on glass(OMOG)

随着大数值孔径193i(na>=1)的光刻机引入,mask上的尺寸越来越小,若其挡光的CR越厚,光波与Cr的相互作用就越强,就会导致曝光的最佳聚焦值随着图像尺寸发生偏移,这就叫做mask 3d效应

为了降低其效应,只能把cr越弄越薄,但是目前的bim已经薄到极限了,所以在32nm节点以后,只能用更高光密度(optical density(OD)的MoSi,其OD>=3)作为吸收层(absorber)这就叫做MoSi双级掩膜

再新一点就是比如Ta的掩膜,叫ABF,没怎么了解

还有很多复杂的掩膜工艺

来源:Kurnal

/2

/2