- 引言

- 一、D 触发器的Verilog代码实现和 RTL 电路实现

- 二、Latch 锁存器的Verilog代码实现和 RTL 电路实现

引言

D 触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

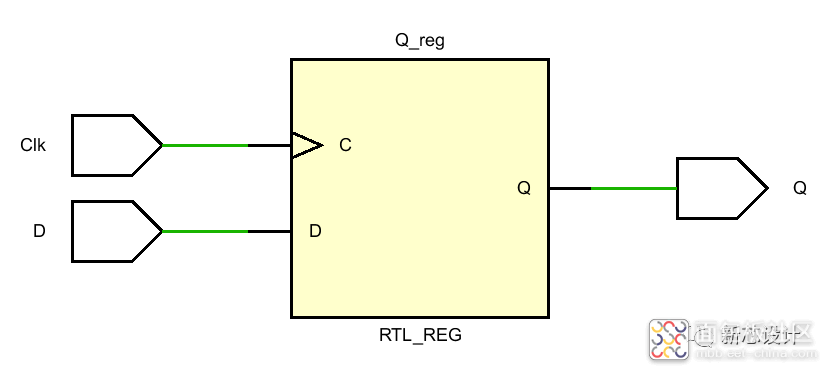

一、D 触发器的 Verilog 代码实现和 RTL 电路实现

Plaintext module D_FF( input Clk, input D, output reg Q ); always @(posedge Clk) begin Q <= D; end endmodule |

触发器(Flip - Flop):能够存储 1 位二值信号的基本单元统称为 D 触发器,简称 DFF,多个 D 触发器的级联便构成了能够存储多位二值信号的基本电路。时钟信号(Clock),简称 Clk,当系统中有多个 D 触发器需要同时动作时,就可以用同一个 Clk 信号作为同步控制信号。

电路中的输入端处没有小圆圈表示 Signal 以高电平为有效信号。(如果在 Signal 输入端画有小圆圈,则表示 Signal 以低电平作为有效信号)。

D 触发器的 RTL 电路图如下所示:

D 触发器的 RTL 电路图

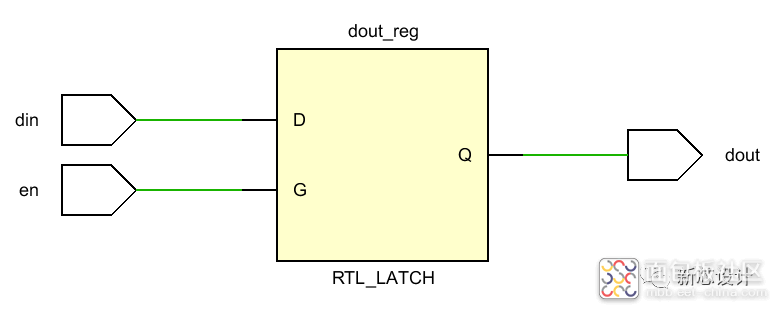

二、Latch 锁存器的 Verilog 代码实现和 RTL 电路实现

Plaintext module Latch( input din, input en, output reg dout ); always @(din or en) if(en) dout <= din; endmodule |

锁存器(Latch):一种对脉冲电平敏感的存储单元电路,可以在特定输入脉冲电平作用下才改变状态;而锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,利用电平控制数据的输入与输出,它包括不带使能控制的锁存器和带使能控制的锁存器。锁存器的缺点是容易产生毛刺,不稳定,不利于静态时序分析。

锁存器的 RTL 电路图如下所示:

锁存器的 RTL 电路图

/4

/4