- 引言

- 一、并串转换器的Verilog代码实现

- 二、并串转换器的 RTL 电路实现

引言

设计的思想是这样的:我们先将 N 位并行的数据(N 根线)暂时寄存在一个 N 位的寄存器中,然后通过移位寄存器的移位,依次输出到一位输出端口即可实现并串转化。

一、并串转换器的 Verilog 代码实现

Plaintext module Pal2Serial( // 四位并串转换程序:PiSo_Shift = 4 input Clk, input Load, // 输入数据加载信号 input [3:0] din, // 4 位并行输入数据 output dout // 1 位串行输出数据 ); reg [3:0] databuff = 4'b0000; // 中间缓冲通道 always @(posedge Clk) if (Load) databuff <= din; else databuff <= databuff << 1; assign dout = databuff[3]; endmodule |

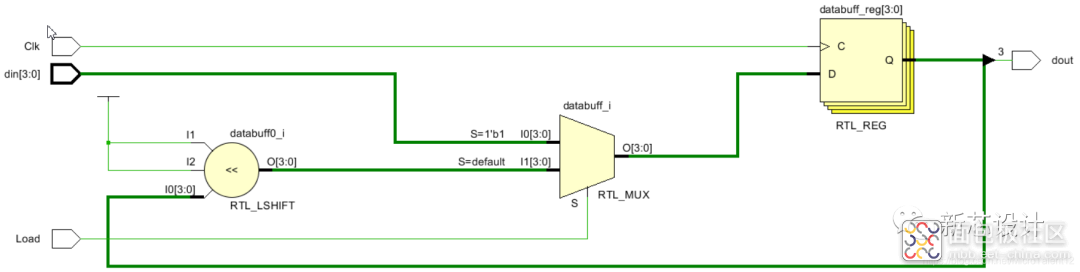

二、并串转换器的 RTL 电路实现

并串转换器的 RTL 电路图

/5

/5