抖动和相位噪声是晶振的非常重要指标,本文主要从抖动和相位噪声定义及原理出发,阐述其在不同场景下对数字系统、高速串行接口、数据转换器和射频系统的影响。

1. 抖动和相位噪声

1.1. 抖动

1.1.1. 抖动定义和分类

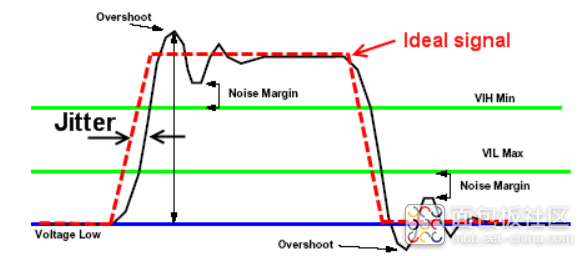

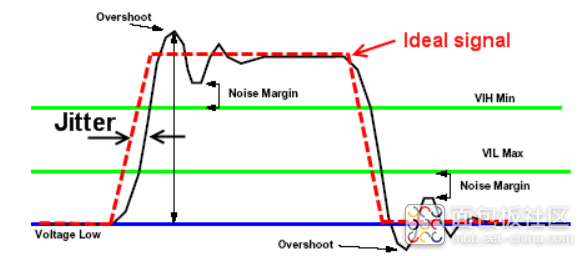

ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。

对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的。即使是同一个时钟,此刻时钟周期的边沿与它下一个时钟周期的边沿都是会发生变化的。

1.1. 抖动

1.1.1. 抖动定义和分类

ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。

对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的。即使是同一个时钟,此刻时钟周期的边沿与它下一个时钟周期的边沿都是会发生变化的。

图1 抖动的图示

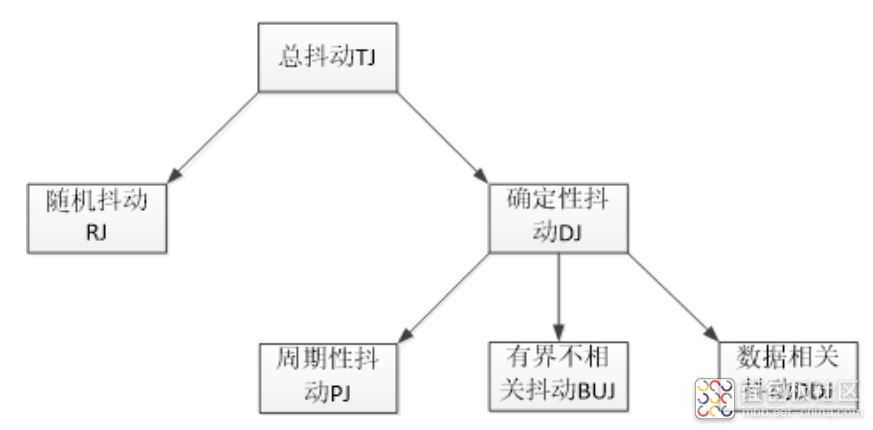

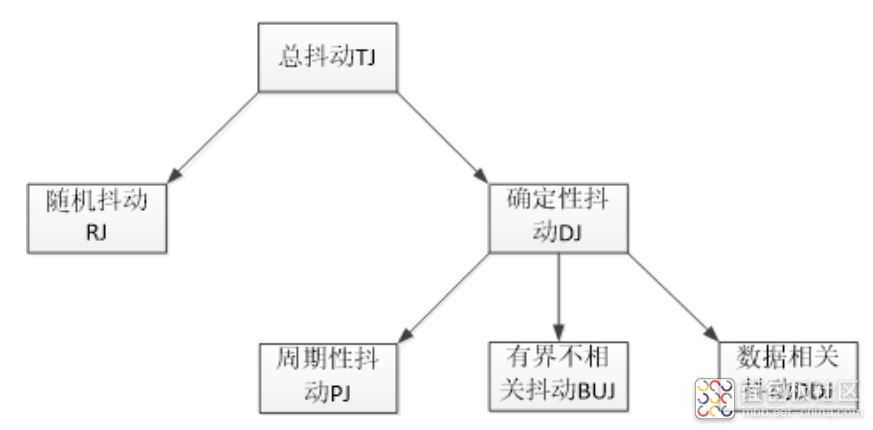

抖动分确定性抖动(Deterministic jitter,DJ)和随机性抖动(Random jitter,RJ)两种。DJ通常幅度有限,以单位时间表示,可粗略地分为周期性抖动(PJ)、有界不相关抖动BUJ和数据相关的抖动DDJ;RJ为高斯分布,以RMS均方根值表示。

图2 抖动分类

1.1.2. 随机抖动

随机抖动是在任何周期中都是无法预测的,只能预测其统计特性。最常用于随机抖动测量的是正态分布的标准差,也叫RMS抖动。

随机抖动来自真正的随机行为,器件的内部热噪声、闪烁噪声、晶体的随机振动、宇宙射线等都可能引起随机抖动,这些来源很难消除。

1.1.3. 确定性抖动

确定性抖动是遵循已知模式的抖动,非高斯分布,通常是有边际的,它是可重复可预测的。确定性抖动的峰值可以直接测量,并且测量的结果是绝对的。

(1)周期性抖动PJ

周期性抖动测量主要是针对时钟信号,它测量实时时钟的每一个周期,然后对实际时钟周期进行数据统计,最后根据概率统计给出该时钟周期大小的分布规律,此测量将显示信号的整体质量。可能的抖动源有:电源的EMI干扰与扩频时钟SSC的调制信号。

(2)有界不相关抖动BUJ

主要由电源或相邻信道的串扰等引起的,可以是周期的(Periodic),也可以是非周期的(non-periodic)。其来源通常有3种:电源噪声、串扰和外部噪声。

(3)数据相关抖动DDJ

DDJ分为ISI和DCD两种。

符号间干扰ISI是由于信道带宽受限,相邻的码元冲击效应叠加产生。

DCD 值是相对于50%的理想占空比偏差,一般分两种情况:

①信号的上升沿和下降沿的斜率不同;

②信号DC平均值发生变化而导致波形的判决门限高或者低于判决阈值;

随机抖动是在任何周期中都是无法预测的,只能预测其统计特性。最常用于随机抖动测量的是正态分布的标准差,也叫RMS抖动。

随机抖动来自真正的随机行为,器件的内部热噪声、闪烁噪声、晶体的随机振动、宇宙射线等都可能引起随机抖动,这些来源很难消除。

1.1.3. 确定性抖动

确定性抖动是遵循已知模式的抖动,非高斯分布,通常是有边际的,它是可重复可预测的。确定性抖动的峰值可以直接测量,并且测量的结果是绝对的。

(1)周期性抖动PJ

周期性抖动测量主要是针对时钟信号,它测量实时时钟的每一个周期,然后对实际时钟周期进行数据统计,最后根据概率统计给出该时钟周期大小的分布规律,此测量将显示信号的整体质量。可能的抖动源有:电源的EMI干扰与扩频时钟SSC的调制信号。

(2)有界不相关抖动BUJ

主要由电源或相邻信道的串扰等引起的,可以是周期的(Periodic),也可以是非周期的(non-periodic)。其来源通常有3种:电源噪声、串扰和外部噪声。

(3)数据相关抖动DDJ

DDJ分为ISI和DCD两种。

符号间干扰ISI是由于信道带宽受限,相邻的码元冲击效应叠加产生。

DCD 值是相对于50%的理想占空比偏差,一般分两种情况:

①信号的上升沿和下降沿的斜率不同;

②信号DC平均值发生变化而导致波形的判决门限高或者低于判决阈值;

表1 确定性抖动和随机抖动的比较

1.2. 相位噪声和抖动转换

相位噪声是时钟频域上的表现,抖动是时钟时域上的体现,相位噪声可以通过数学变换转换成抖动。

1.2.1. 相位噪声定义

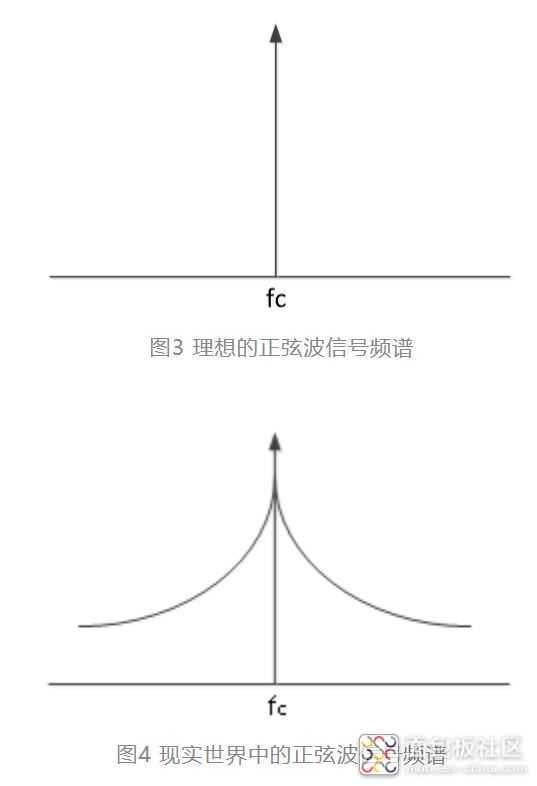

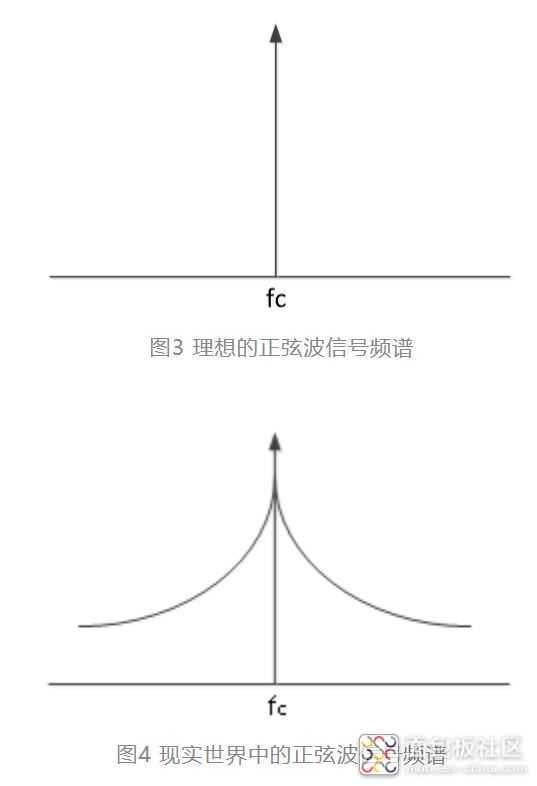

理想正弦波信号V(t)=Asin(2*pi*fc*t),其频谱就是一条以fc为中心的直线。现实世界中的正弦波信号有不稳定性,从而产生了边带,其频谱是一条类似裙子的逐渐衰落曲线。

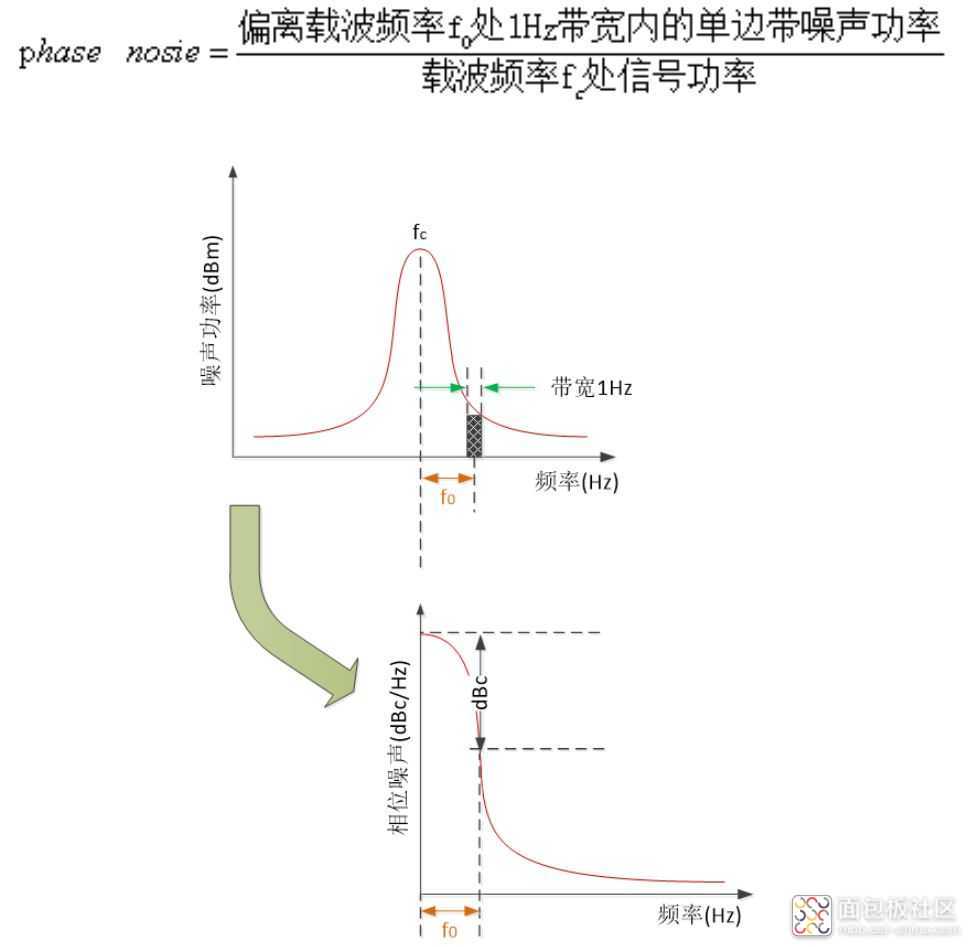

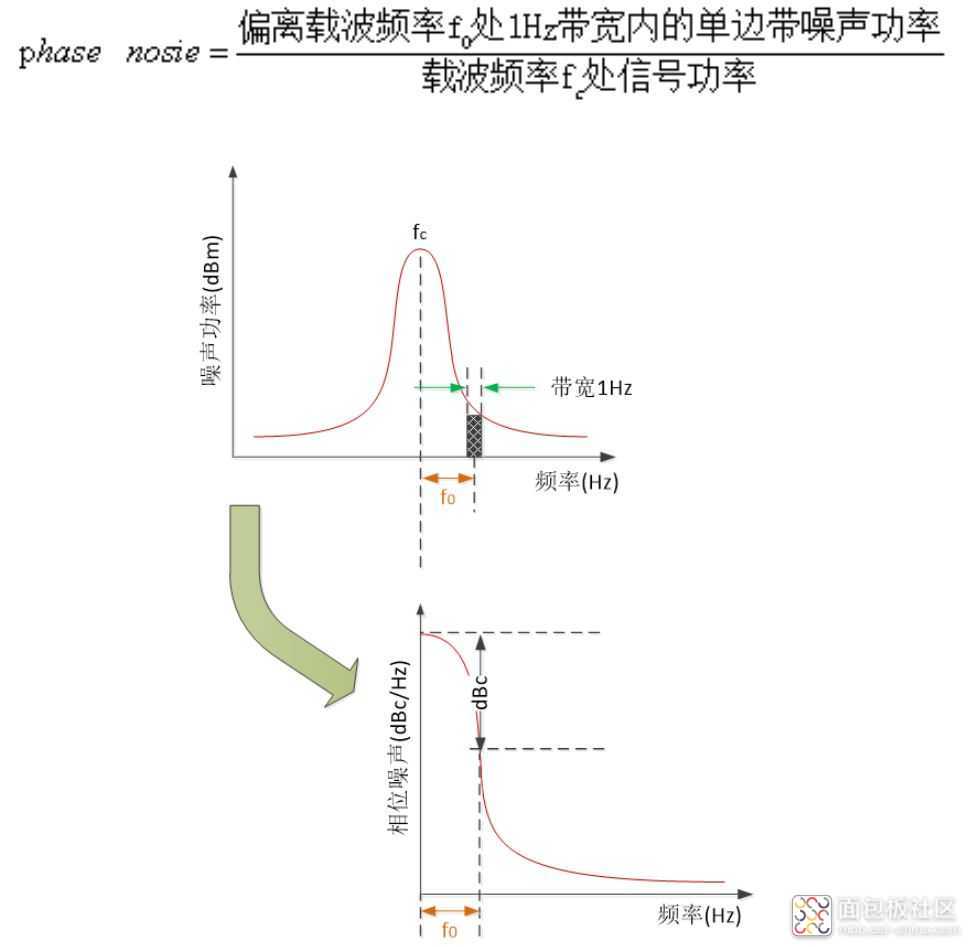

相位噪声(Phase Noise)是抖动在频域上的表现,通常定义为在某一频率偏移f0处1Hz宽带内的单边噪声信号积分功率和信号功率比值,单位是dBc/Hz,通常表示为dBc/Hz@ f0,数学表示如下:

相位噪声是时钟频域上的表现,抖动是时钟时域上的体现,相位噪声可以通过数学变换转换成抖动。

1.2.1. 相位噪声定义

理想正弦波信号V(t)=Asin(2*pi*fc*t),其频谱就是一条以fc为中心的直线。现实世界中的正弦波信号有不稳定性,从而产生了边带,其频谱是一条类似裙子的逐渐衰落曲线。

图5 相位噪声定义图示

晶振相位噪声的来源主要有三方面:

①晶体品质因数Q值,主要影响1Hz~1KHz近端相位噪声;

②晶体外围电路,包括电源、振荡电路、驱动线路等,主要影响1KHz~10MHz的相位噪声;

③信号输出的白噪声,主要影响10M~20M远端相位噪声。

1.2.2. 相位噪声转换成抖动

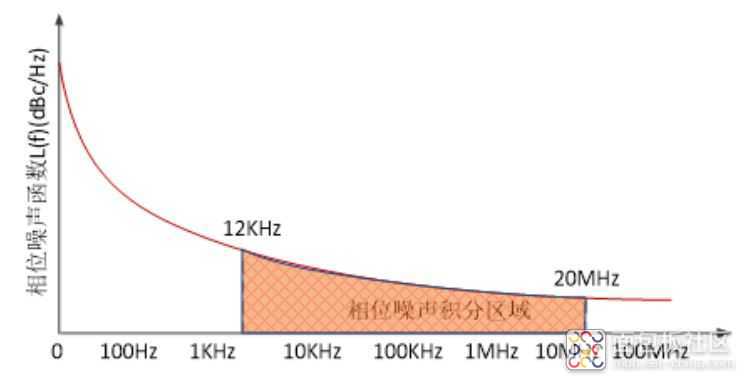

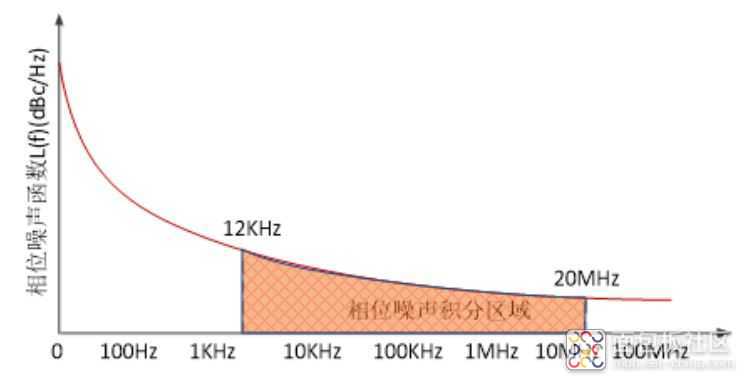

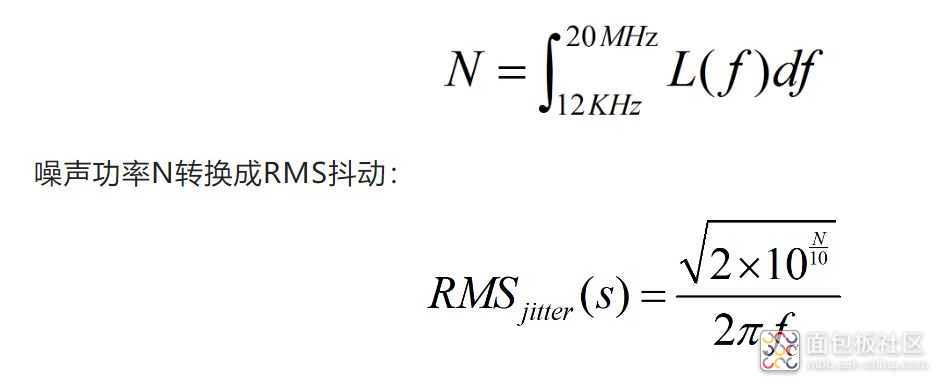

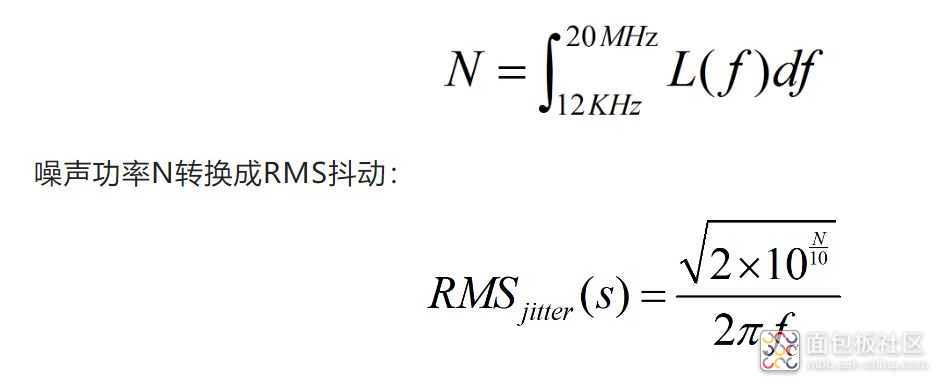

抖动是信号的时域表现,相位噪声呈现出的是信号的频域特性。这两者本质上是一样的,只是表述方式不同而已,下图6给出从相位噪声转换成抖动的示意。

①晶体品质因数Q值,主要影响1Hz~1KHz近端相位噪声;

②晶体外围电路,包括电源、振荡电路、驱动线路等,主要影响1KHz~10MHz的相位噪声;

③信号输出的白噪声,主要影响10M~20M远端相位噪声。

1.2.2. 相位噪声转换成抖动

抖动是信号的时域表现,相位噪声呈现出的是信号的频域特性。这两者本质上是一样的,只是表述方式不同而已,下图6给出从相位噪声转换成抖动的示意。

图6 相位噪声积分图示

L(f)以功率谱密度函数的形式给出了边带噪声的分布,单位为dBc。单边带的总噪声功率N可以由L(f)函数在整个感兴趣频段内(通常选用的积分范围为12KHz到20MHz)积分得到。

2. 抖动和相位噪声的影响

在通信网络、无线传输、CPRI和SONET等高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。下面描述时钟抖动和相位噪声对数字系统、高速串行接口、数据转换器和射频系统的影响。

在通信网络、无线传输、CPRI和SONET等高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。下面描述时钟抖动和相位噪声对数字系统、高速串行接口、数据转换器和射频系统的影响。

2.1. 数字系统

在数字系统中时钟边沿决定了每个基本单元的开始和结束时间。当抖动改变了时钟边沿从而导致时钟周期变化时,每个基本单元的有效工作时间也会发生变化,可能会导致信号的建立时间和保持时间不能满足要求,从而影响电路的正常工作。

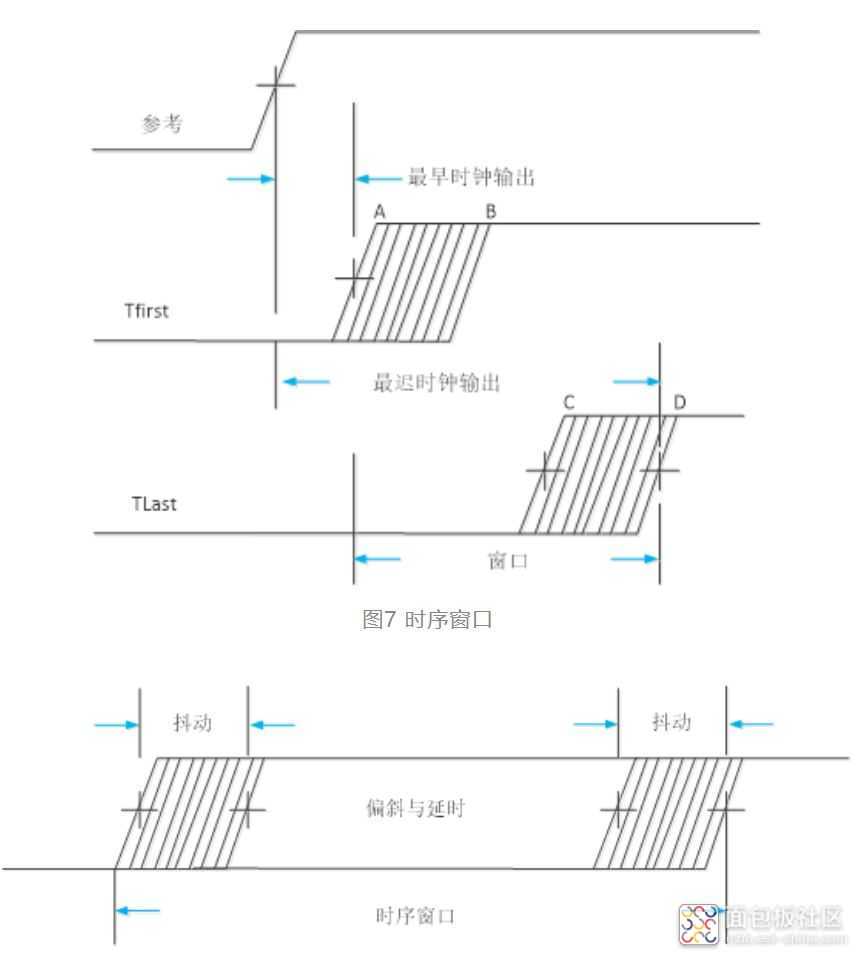

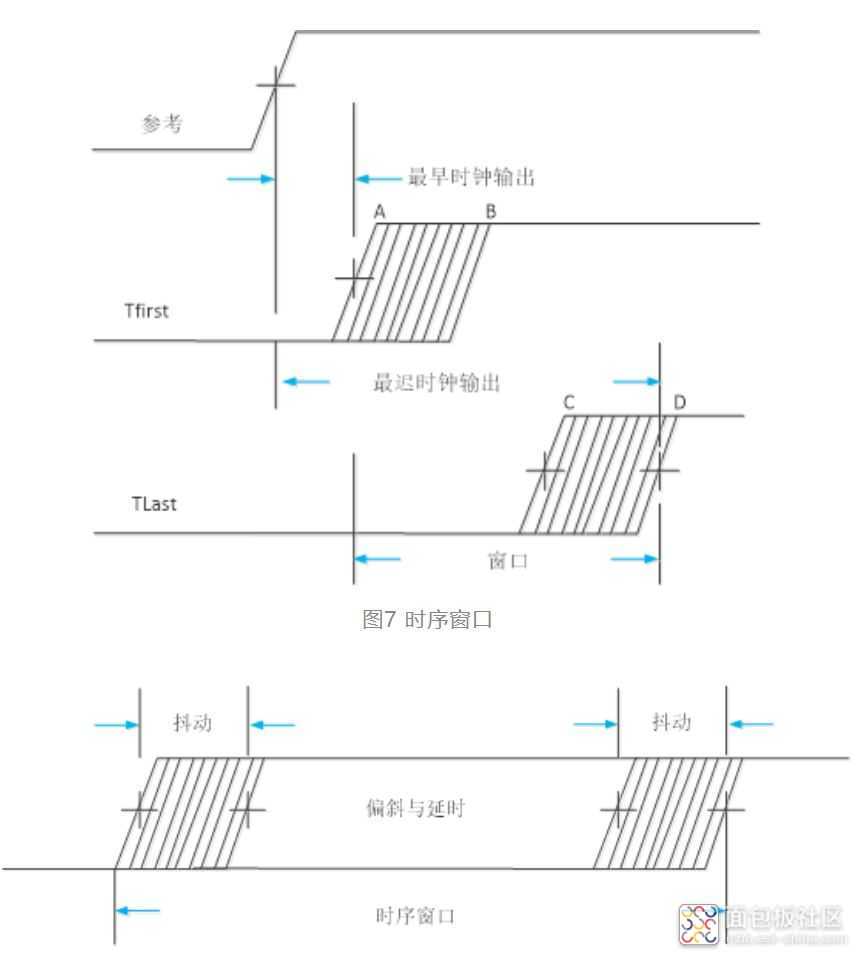

确定时钟容差最好的方法是建立时序预算。如下图7所示,最早达到时钟的上升沿标志着窗口开始,最晚到达时钟的上升沿标志着窗口的结束,两者的时间差为窗口。为了创建时序窗口,还需要考虑加上偏斜、延时和抖动等指标(见图8)。

随着系统时钟速度的提高,要求时序电路的容差更小,减小时钟抖动有利于提高系时钟的容差,给系统的偏斜与延时提供更多的余量。

在数字系统中时钟边沿决定了每个基本单元的开始和结束时间。当抖动改变了时钟边沿从而导致时钟周期变化时,每个基本单元的有效工作时间也会发生变化,可能会导致信号的建立时间和保持时间不能满足要求,从而影响电路的正常工作。

确定时钟容差最好的方法是建立时序预算。如下图7所示,最早达到时钟的上升沿标志着窗口开始,最晚到达时钟的上升沿标志着窗口的结束,两者的时间差为窗口。为了创建时序窗口,还需要考虑加上偏斜、延时和抖动等指标(见图8)。

随着系统时钟速度的提高,要求时序电路的容差更小,减小时钟抖动有利于提高系时钟的容差,给系统的偏斜与延时提供更多的余量。

图8 时序窗口的组成

2.2. 高速接口

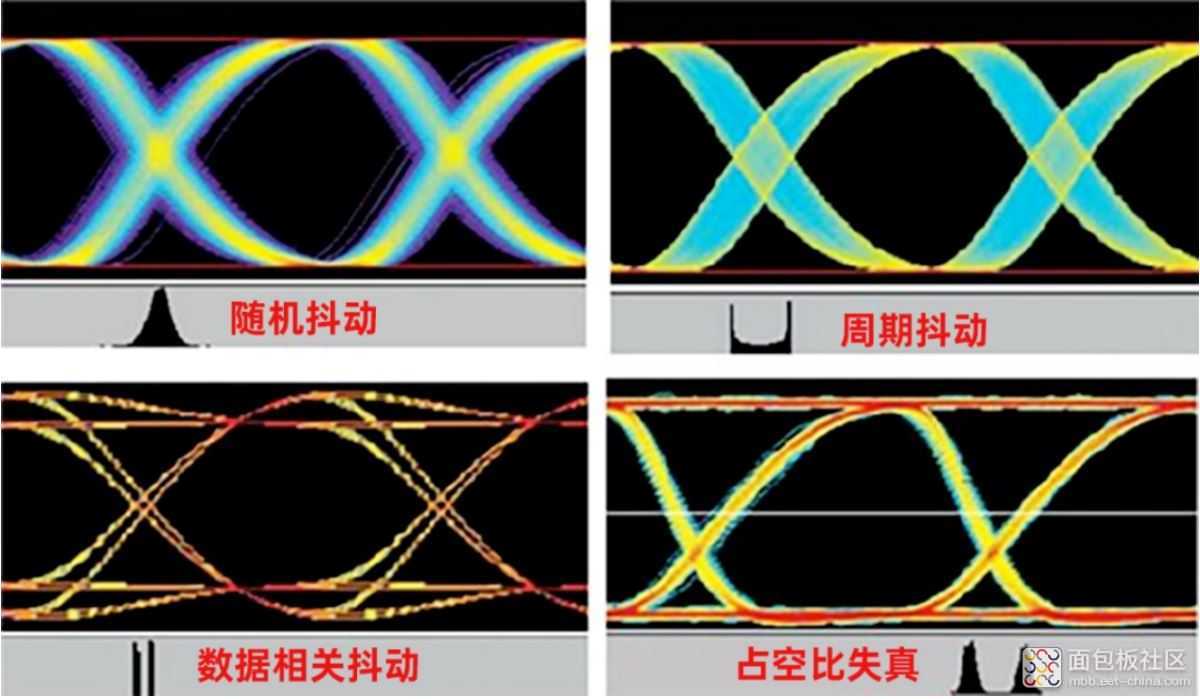

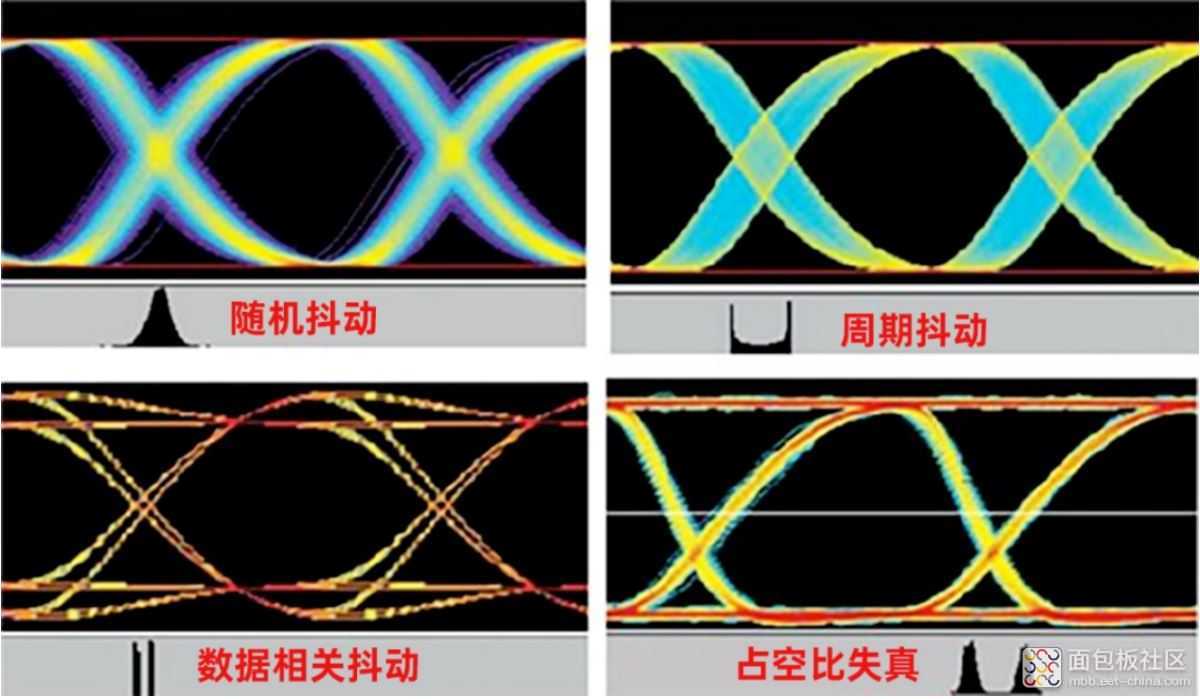

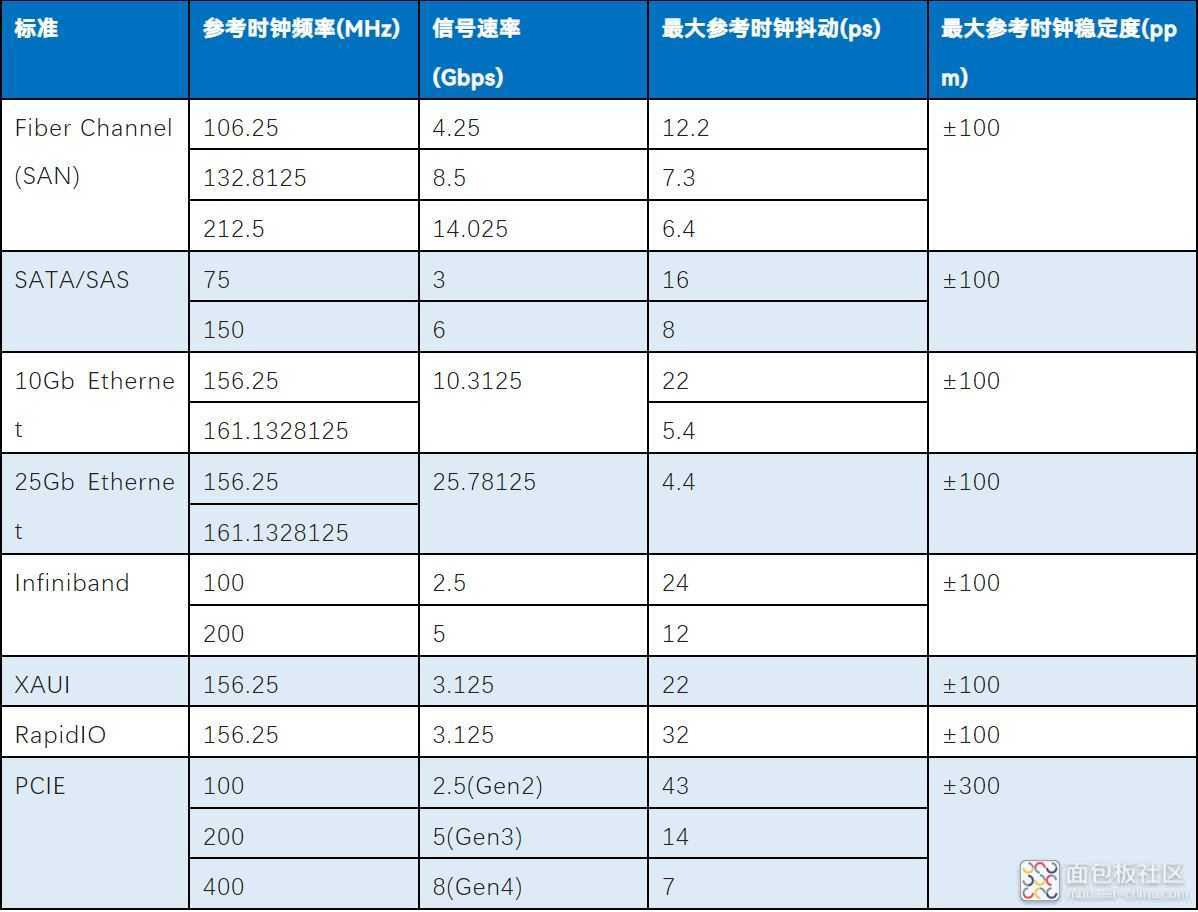

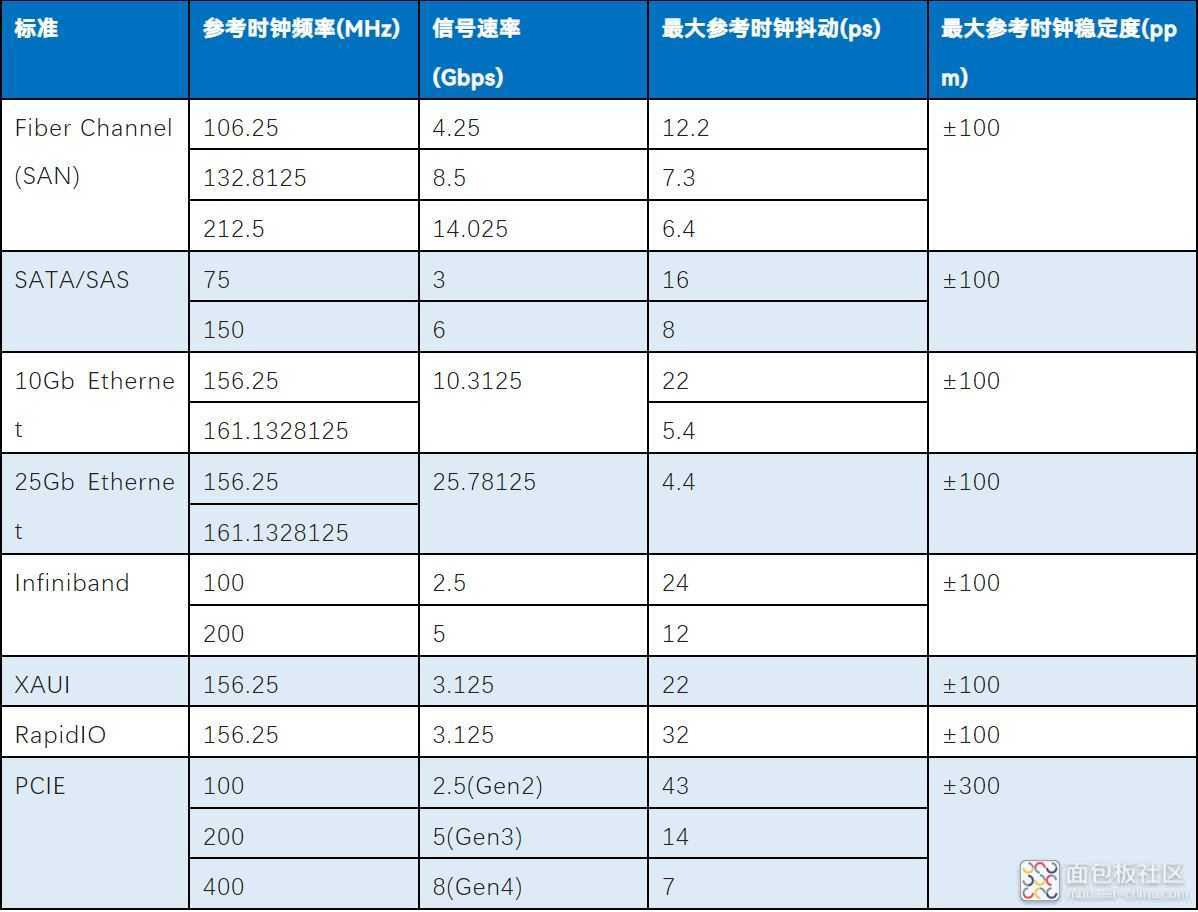

当使用Serdes发送或者接收串行bit流时,时钟是用于对传输的数据进行编码,并将时钟信息嵌入到传输的数据中。接收器会从传输的比特流中分离出单独的时钟,用于对数据进行采样和捕捉。在该系统中累计抖动决定了bit到达与采样之间的时间差,因此它是最重要的。如果整个系统中抖动太大,会出现如图9中所示的眼图,从而会导致接受端采样到错误的bit。表2给出了常见的高速接口抖动要求。

当使用Serdes发送或者接收串行bit流时,时钟是用于对传输的数据进行编码,并将时钟信息嵌入到传输的数据中。接收器会从传输的比特流中分离出单独的时钟,用于对数据进行采样和捕捉。在该系统中累计抖动决定了bit到达与采样之间的时间差,因此它是最重要的。如果整个系统中抖动太大,会出现如图9中所示的眼图,从而会导致接受端采样到错误的bit。表2给出了常见的高速接口抖动要求。

图9 时钟抖动对高速接口的影响

表2 常见的高速接口抖动要求

2.3. 数据转换器

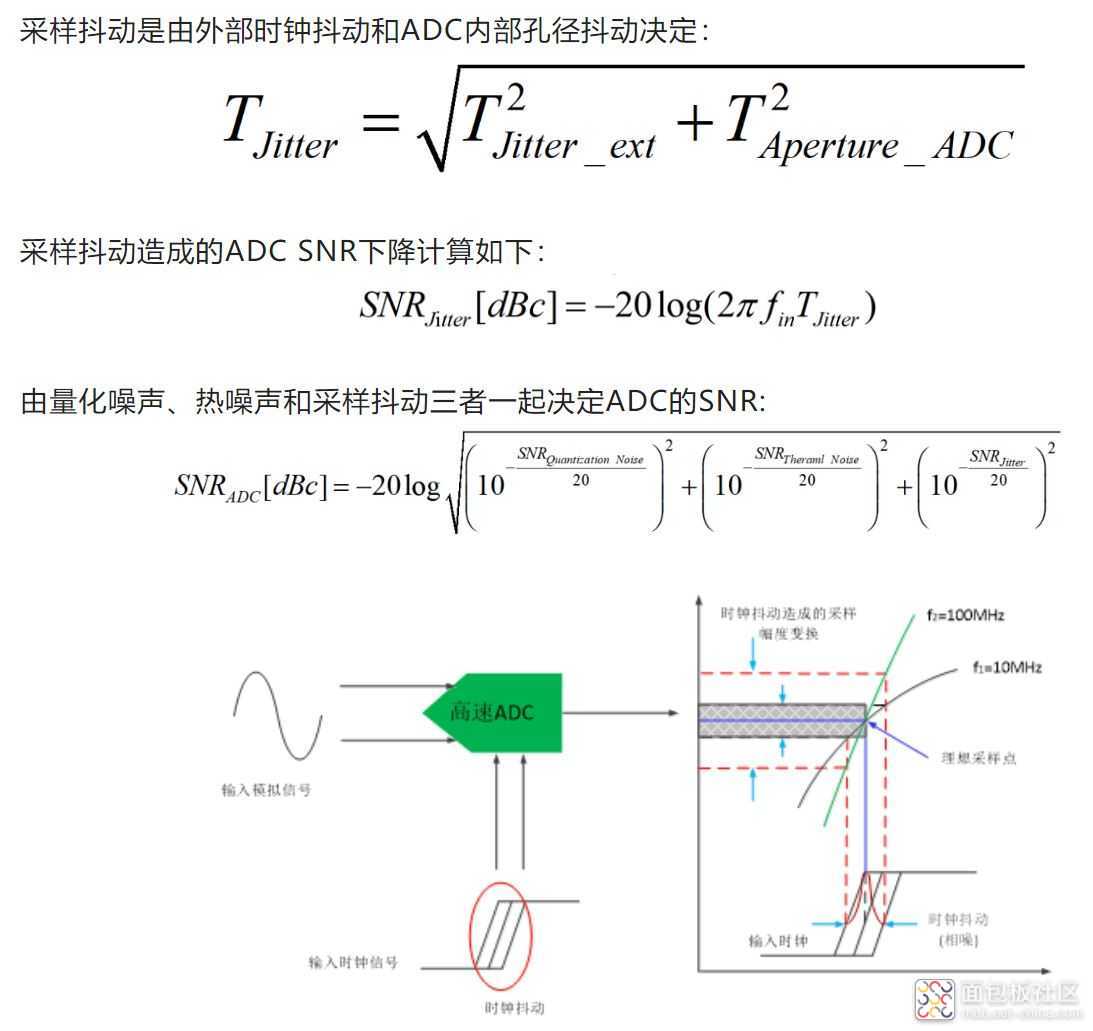

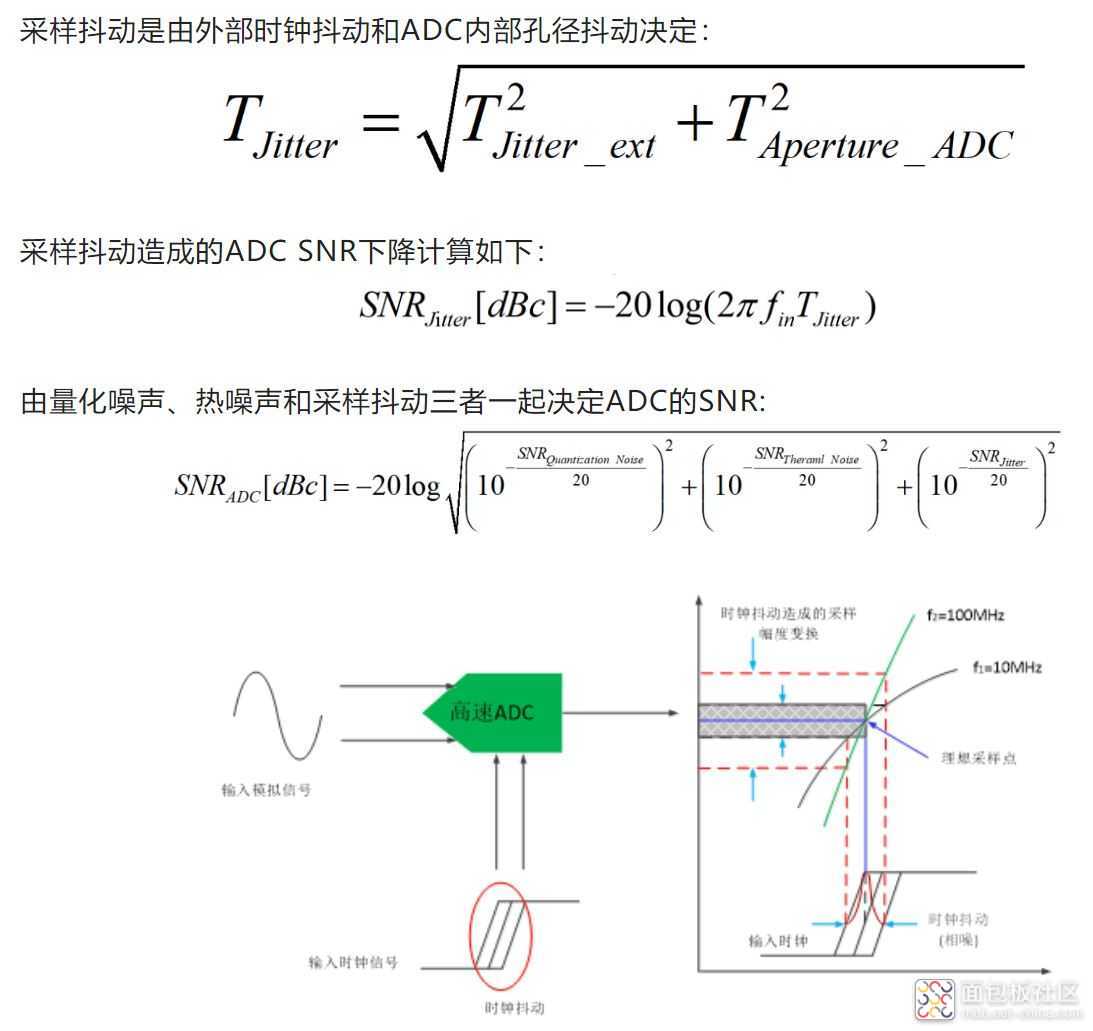

在模数转换器(ADC)和数模转换器(DAC)中,对信号的采样可以转换为信号与时钟时域乘积。时钟决定了信号采样时间,如果时钟抖动导致采样时间偏离了理想采样时间,会导致采样到的信号值相比于理想的信号值发生变化,从而恶化信噪比和动态范围,降低转换器的有效分辨率。

采样抖动是由外部时钟抖动和ADC内部孔径抖动决定:

在模数转换器(ADC)和数模转换器(DAC)中,对信号的采样可以转换为信号与时钟时域乘积。时钟决定了信号采样时间,如果时钟抖动导致采样时间偏离了理想采样时间,会导致采样到的信号值相比于理想的信号值发生变化,从而恶化信噪比和动态范围,降低转换器的有效分辨率。

采样抖动是由外部时钟抖动和ADC内部孔径抖动决定:

图10 时钟抖动对ADC采样影响

2.4. 射频系统

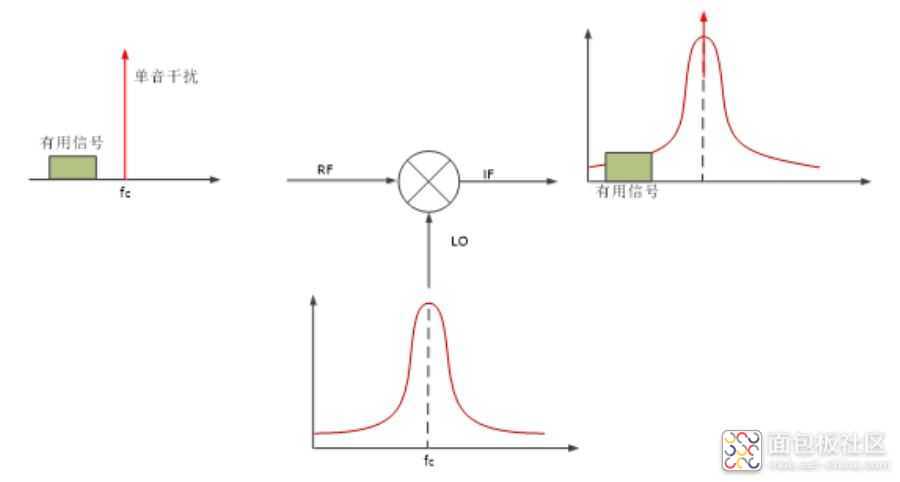

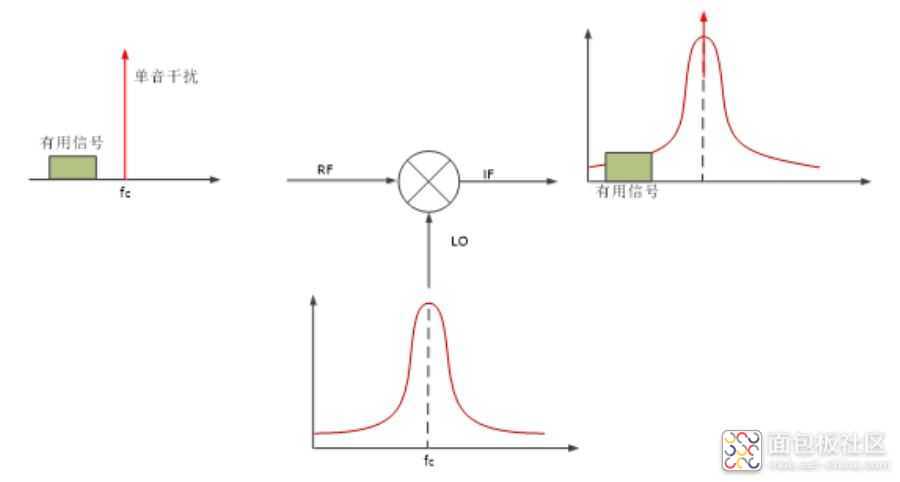

在射频系统中,时钟主要为产生本振的锁相环提供参考。锁相环合成出来的本振信号通常为混频器或者正交调制、解调器提供稳定的高频振荡频率,用于产生发射信号或者下变频的接收信号。当混频器工作时,源信号会在时域上乘以本振时钟来进行上变频或下变频,得到目标信号的频谱为源信号频谱与本振时钟频谱的乘积。

因此,本振时钟中的任何相位噪声都会在输出端产生不想要的信号并混在目标信号中,可能会出现倒易混频,从而降低系统中有用信号的信噪比,降低接收机的灵敏度,恶化发射机的ACLR和EVM,这就要求晶振和时钟选型必须满足严格的相位噪声指标。

在射频系统中,时钟主要为产生本振的锁相环提供参考。锁相环合成出来的本振信号通常为混频器或者正交调制、解调器提供稳定的高频振荡频率,用于产生发射信号或者下变频的接收信号。当混频器工作时,源信号会在时域上乘以本振时钟来进行上变频或下变频,得到目标信号的频谱为源信号频谱与本振时钟频谱的乘积。

因此,本振时钟中的任何相位噪声都会在输出端产生不想要的信号并混在目标信号中,可能会出现倒易混频,从而降低系统中有用信号的信噪比,降低接收机的灵敏度,恶化发射机的ACLR和EVM,这就要求晶振和时钟选型必须满足严格的相位噪声指标。

图11 单音干扰时的倒易混频

大普通信的Crystal和SPXO在-40℃~+85℃范围内具有±20ppm的稳定度,42fs@156.25MHz的低相位抖动,具有单端和差分两种输出接口;TCXO具有-150dBc/Hz@1KHz的相位噪声,OCXO极低相位噪声-170dBc/Hz@1KHz,并达到-120dBC/Hz@1Hz的优越近端相噪。这些产品非常适合精密仪器、高速接口、数字系统、射频系统等对相位噪声有高需求的场景。

另外大普通信的SO系列全硅振荡器,抗振动性能好,典型抖动为350fs,符合PCIe Gen1/2/3/4/5,支持频率可配置,非常适合服务器、高速存储、交换机等产品。

3. 相关术语

4. 参考文献

[1] Telcordia GR-253-CORE Issue 4

[2] Renesas Application Note839《RMS phases jitter》

[2] Renesas Application Note839《RMS phases jitter》

文章来源:大普通信

/4

/4