来源:卓乎知芯

日前,中科院计算所等机构用 AI 技术设计出了世界上首个无人工干预、全自动生成的 CPU 芯片——“启蒙1号”。相关论文《Pushing the Limits of Machine Design:Automated CPU Design with AI》(机器设计新突破:使用人工智能自动设计CPU)中科院团队已于6月27日发布。

图源:中科院计算所论文

一、“启蒙1号”与比GPT-4设计芯片对比

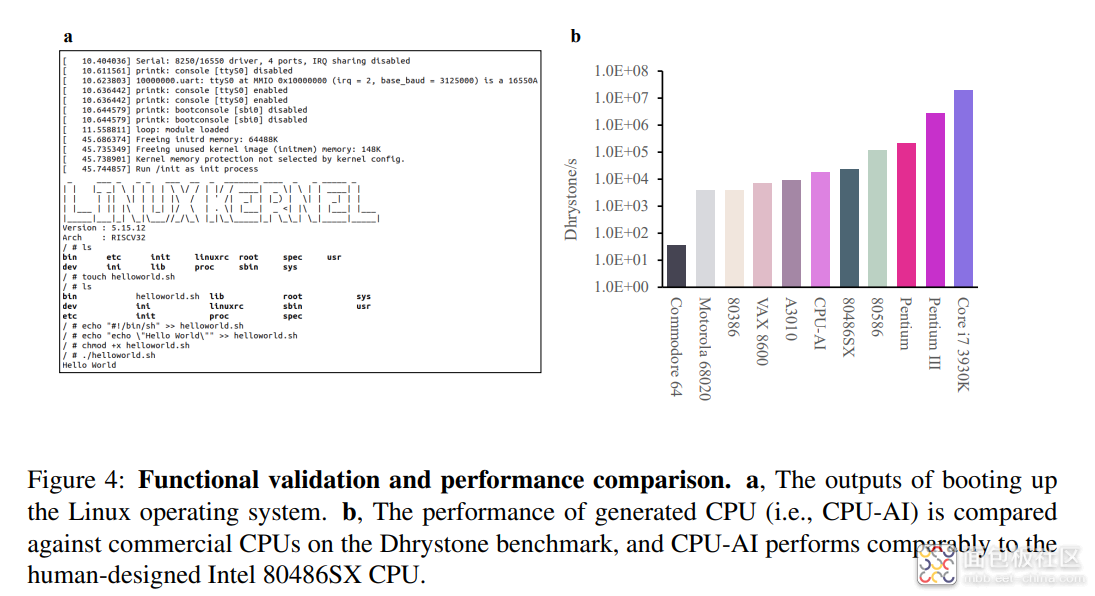

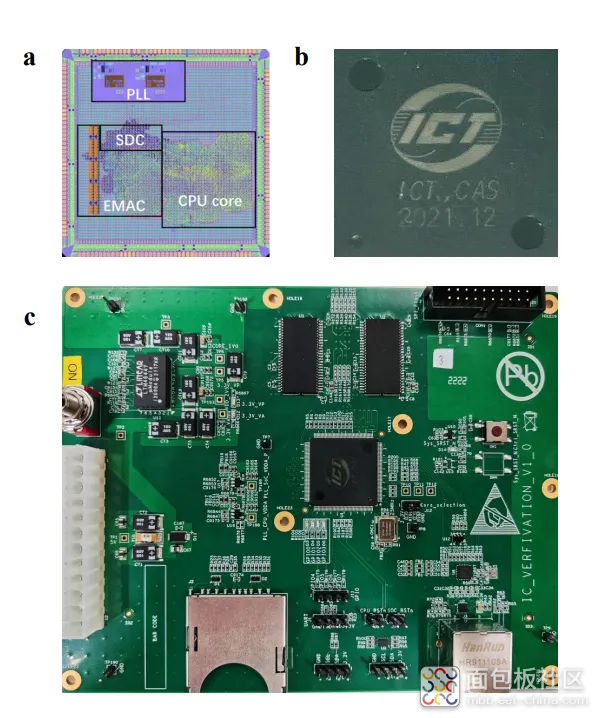

启蒙1号处理器是完全由AI设计的处理器,采用了基于RSIC-V指令集的32位架构。该处理器早在2021年12月就完成了流片验证。流片采用了65nm制造工艺,并且具备高达300 MHz的运行频率,能够运行Linux操作系统,并且在SPEC CPU2000测试程序中表现出与Intel 486相当的性能。且在同一测试中,该处理器似乎比Acorn Archimedes A3010还更快一些。此前,纽约大学Tandon工程学院的研究人员就曾使用GPT-4通过简单的英语对话设计了一款微处理芯片。不过该芯片相对简单,采用了130nm工艺,并缺乏实际应用。与此相比,中科院的启蒙1号处理器基于BSD二元猜测图(Binary Speculation Diagram)算法进行设计,采用了65nm制造工艺,并且仅用了5个小时就生成了400万逻辑门,比GPT-4能设计的芯片大4000倍。

芯片功能性验证比较

二、数字芯片设计流程

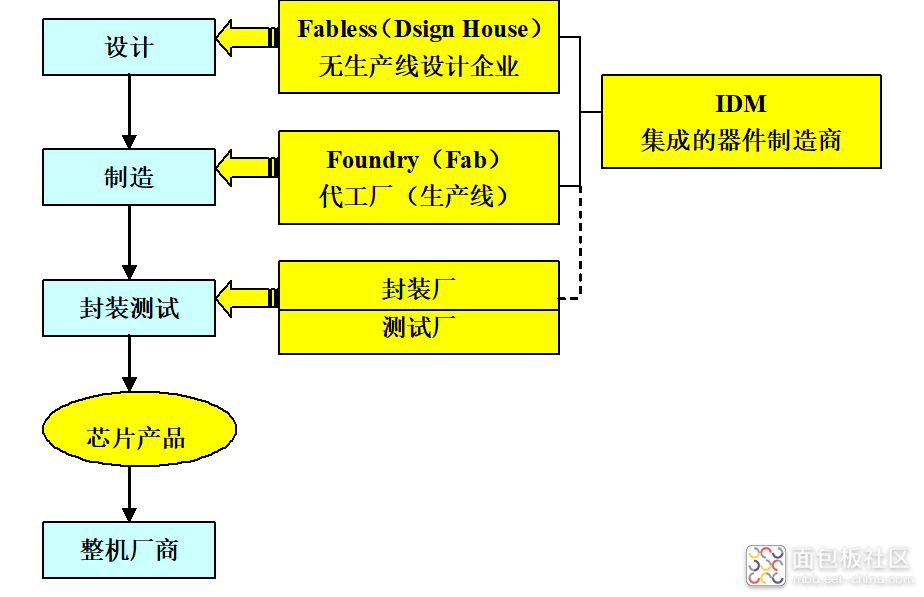

数字芯片设计流程是指将数字电路设计转化为物理实现的过程。概括说,数字芯片设计流程分为,芯片设计,芯片制造,芯片封装。

图源:网络

常见的数字芯片设计流程。首先,要明确设计的需求和目标,了解芯片应该具备的功能、性能、功耗和面积等要求。在需求分析的基础上,进行芯片的整体架构设计,确定各个功能模块之间的关系和接口,以及整体的数据流和控制流。设计师会使用专门的验证工具和技术,对设计的功能进行模拟和验证,这一阶段主要用于发现和修复设计中的错误和缺陷。在验证完成后,进行寄存器传输级(RTL)设计,这一阶段将设计转化为硬件描述语言(如Verilog或VHDL),描述电路的逻辑行为。

然后再将RTL设计进行综合,将其转化为门级电路网表,综合工具会根据目标库中的标准单元和约束条件,生成具体的门级逻辑电路。接着使用物理设计工具,对门级网表进行布局和布线。布局阶段决定了电路中各个元件的位置和布局方式,布线阶段则决定了电路中各个元件之间的连线方式。进行布局和布线后,需要进行物理验证以确保电路的正确性和可制造性。包括电气规则检查(DRC)、布线规则检查(LVS)和时序分析等。

根据物理验证的结果,对电路进行优化,以改善性能、功耗和面积等指标。然后,需要进行静态时序分析,以确保芯片能够满足时序要求,这包括时序路径的收敛性、时钟频率等的分析。接着进行物理仿真,验证电路在实际物理环境中的行为,包括电压噪声、功耗分析等。当设计验证完成后,就能生成用于制造芯片的掩膜数据。到此,设计环节结束。设计好的掩膜数据就可以提供给芯片厂商制造和封装了。最后,对制造好的芯片还进行测试和验证,确保其符合设计要求和规格。

值得注意的是,在芯片设计环节的各个环节,如今都使用了电子设计自动化EDA工具,但EDA也只是辅助设计,更多环节还是需要工程师来完成。就比如,前端硬件描述语言 (HDL),就必须要工程师们对简单语言进行描述翻译(如Verilog)。然后在电子设计自动化(EDA)工具(如逻辑综合或高层次综合工具)的辅助下生成电路逻辑。由于需要相当多的专业知识,操作过程非常耗费时。

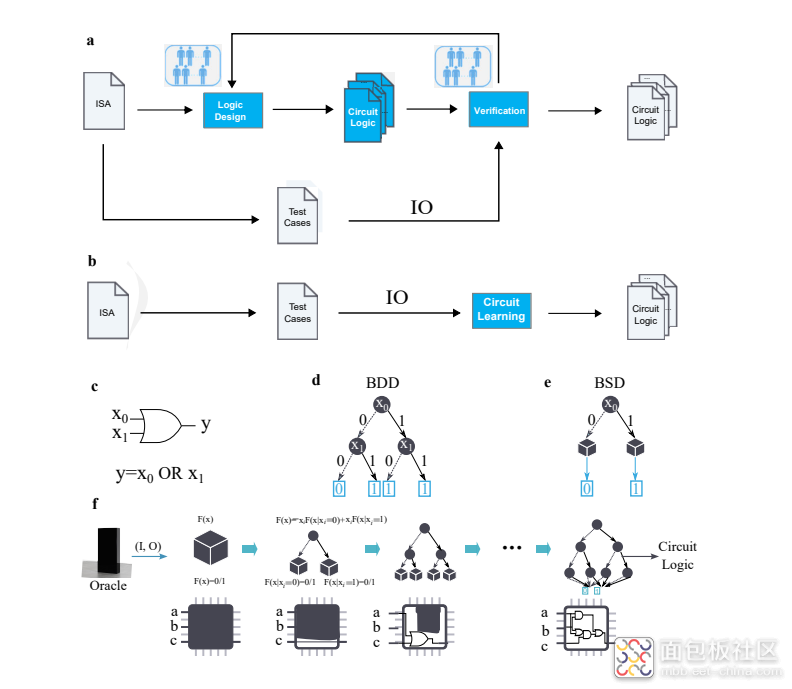

三、全自动CPU设计流程

与传统CPU设计流程中需要大量人工参与不同,根据论文内容显示,“启蒙1号”研究人员是基于对二元决策图(Binary Decision Diagram,BDD)进行扩展的二元猜测图(Binary Speculation Diagram,BSD)。采用AI技术,以输入-输出(IO)作为输入的方法,可以直接从现成的测试用例中获取或生成IO。这样一来,CPU自动设计问题就被形式化为“生成满足输入-输出规范的电路逻辑”的问题。

CPU学习流程:a传统的CPU设计流程、b全自动CPU设计流程

这一方法对传统的CPU设计流程带来了巨大变革,只需要测试用例就能直接生成满足功能需求的电路逻辑,完全消除了传统CPU设计中的手动编程和验证过程。且仅用了5个小时就生成了这款芯片,远远小于常规的处理器完成设计的时间。要知道,一项大型芯片设计项目有时候甚至需要数月甚至数年时间才能完成。此外,与人工设计的CPU相比,该方法缩短了约1000倍的设计周期,且具有99.99999999999%的准确率。

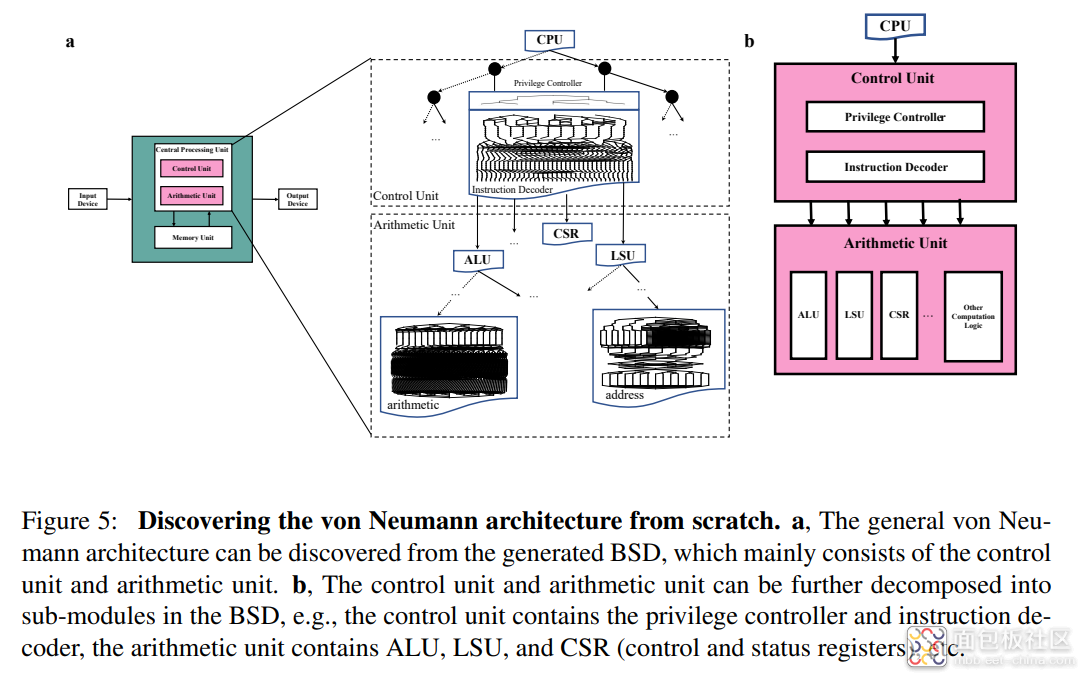

自主探索冯·诺伊曼架构过程

值得注意的是,这一方法甚至自主发现了冯·诺伊曼架构。冯·诺伊曼架构是一种将程序指令存储器和数据存储器合并在一起的电脑设计概念结构,由二进制逻辑、程序存储执行和计算机由五个部分组成的三个基本原则构成,包括运算器、控制器、存储器、输入设备和输出设备。

基于BSD的CPU设计包含控制单元和运算单元。控制单元由BSD的顶层生成,用于整个CPU的全局控制,而运算单元则负责执行算术和逻辑运算。控制单元和运算单元可以进一步分解为BSD中的子模块,例如控制单元包含特权控制器和指令译码器,算术单元包含ALU、LSU和CSR(控制和状态寄存器),直到底层由基本逻辑门构成。

不过,自动芯片设计也面临着两个挑战,挑战一:准确性。推断的布尔函数必须确保对给定的输入输出示例的正确性,并对未见过的输入输出示例具有确定性和高准确性。例如,功能验证准确率必须达到超过99.99999999999%。由于任何微小的错误都可能导致巨大的损失,因此这个准确性要求远远超过传统的AI算法和应用对精度的要求。

挑战二:可扩展性。推断的布尔函数的规模与工业级中央处理器(CPU)相当,可能由数百万行公式组成。在如此巨大的设计空间中,找到一个功能正确的CPU超出了当前自动化设计方法的能力。布尔函数(Boolean function)在复杂性理论的问题和数字计算机的芯片设计中扮演了基础角色,它描述了如何基于布尔输入进行某种逻辑计算以确定布尔值输出。

布局、制造的芯片和印刷电路板

四、AI制作芯片的意义和应用前景

当然,无论是纽约大学利用 GPT-4 设计的芯片,还是中科院的“启蒙1号”相对当前顶级CPU规模还是较小,但自动生成的芯片具有巨大的潜力,在芯片设计中加速了布局优化的过程,为芯片带来了更高的性能和更低的能耗。在验证和测试阶段,AI还能最大程度地提高测试覆盖率,节省时间,将推动半导体领域的革命与创新。由AI生成的CPU有望在未来达到甚至超越人类专家设计的水平。在ITF World 2023半导体大会上,英伟达创始人兼首席执行官黄仁勋就曾强调AI在芯片制造中的潜力,他认为芯片制造是加速和AI计算的理想应用。AMD首席技术官Mark Papermaster也透露,AMD已经开始在半导体设计、测试和验证阶段应用AI,并计划在芯片设计领域更广泛地使用生成式AI。

随着机器学习的不断突破和电路设计复杂性的增加,机器学习技术已经被应用到芯片设计流程的不同阶段。例如,谷歌利用人工智能设计了比人类更快的芯片布局增强学习(RL)方法。英伟达也提出了基于增强学习(RL)方法,用于设计并行前缀电路,如加法器或优先编码器。此外,还有研究将深度卷积神经网络(CNN)和图神经网络(GNN)等技术应用于自动设计空间探索、功耗分析、VLSI物理设计和模拟设计等领域。

关于AI是否会取代芯片研发工程师的工作,AMD首席技术官Papermaster的观点是否定的。他认为AI不会取代芯片设计师,而是作为辅助工具,具有巨大的加速设计过程的潜力。因为总会有一些工具和工作是 AI 做不到的,因此芯片设计师仍然扮演着重要的角色。此外,当前的AI设计相关安全因素和潜在问题,还需要通过进一步的测试来识别和解决。

/1

/1