如今,许多片上系统 (SoC) 设计的复杂程度已经超乎人们的想象。在今年的 HotChips 研讨会上,展出了许多面向边缘和数据中心领域的全新 SoC 设计,这些设计刷新了业界对于大型芯片的定义。究竟哪些系统设计需要采用具有高度复杂性的 SoC 呢?事实上,除了大型数据中心的 AI 芯片外,自动驾驶车辆(例如汽车、卡车和无人机)、自行着陆的可重用火箭、可实施远程诊断的医疗器械、以及支持智能制造的联网机床控制器,都是此类芯片的需求主力。

这些芯片因其尺寸与复杂性惊人,而被称为“巨型芯片”。现在,我们来共同解读巨型芯片崛起背后的驱动因素。事实上,巨型芯片的产生主要是为了满足互联网连接的需求,这种连接能力不仅能够带来“大数据”信息,同时还能实现有助决策的分布式处理机制。这些与互联网连接的系统需要具有每秒超过 1 万亿次的运算能力,以及部分甚至全部的自主决策能力,而这又进一步推动了软硬件的又一轮创新,以及芯片复杂程度的大幅度提升。

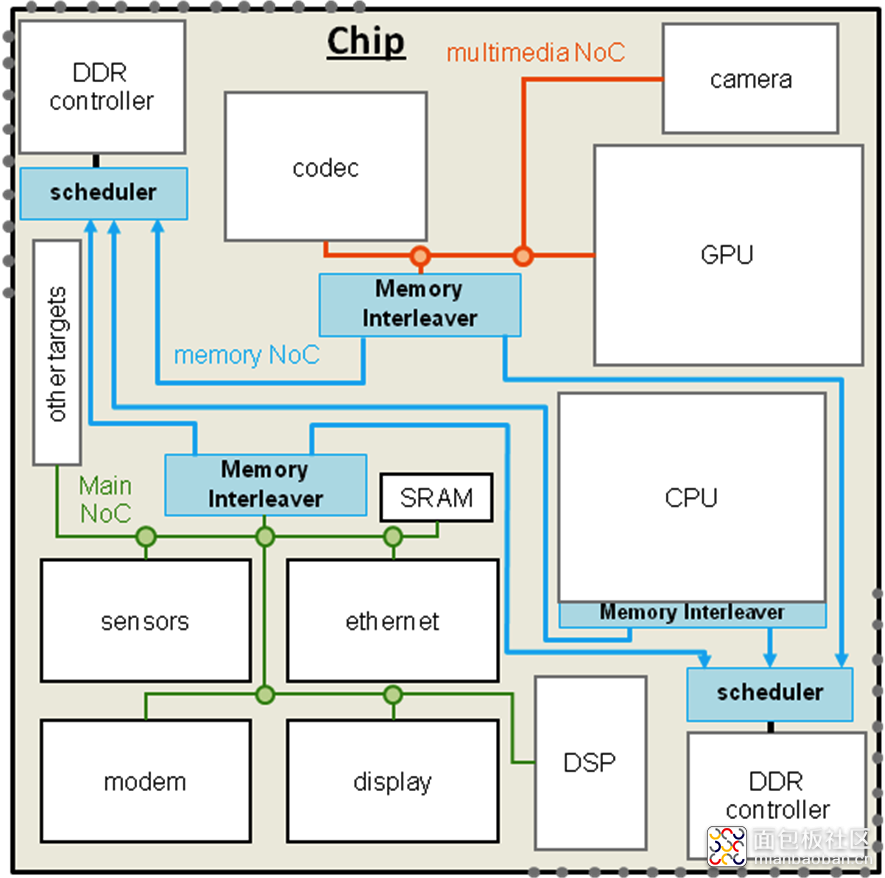

图 1:自动驾驶、机器学习和区块链处理领域的高复杂性需求催生新一代 SoC 设计。图片来源:Arteris IP

尽管有些应用领域只需要系统报告信息,但这类应用数量非常有限,而且往往代表着低价值市场,利润率相对较低。要想真正提高系统的价值,互联系统必须能够自主地制定决策,而这就给软硬件带来前所未有的挑战。

首先,要想自主制定决策,这些系统必须搭载多种类型的传感器以及由复杂软件算法驱动的高性能数据处理系统。硬件不仅要配合软件的需求,同时设备本身也需要支持一些相关算法,以使系统能够与现实世界交互。

尽管我们可以在软件与硬件之间增加一些中间件层,但这对于许多任务关键型应用而言意味着性能的降低和成本的增加。

巨型芯片中的缓存一致性

随着巨型芯片时代的到来,新型系统将能够在复杂的软硬件构件基础上自主地制定决策。此外,IP 块和 EDA 设计工具技术也将随之得到进一步发展,以确保设计人员能够在合理的时间和成本范围内从容应对这种复杂程度的项目。

以巨型芯片中的多处理器缓存一致性为例。这是一套 SoC 中使用的计算机子系统,旨在简化辅助处理子系统(例如视觉加速器及其他图像处理器)的编程。

除了主 CPU 子系统外,巨型芯片还会搭载多层级处理器,以实现专门化的数据处理和高效的控制。此外,为了进一步提升处理能力,配备的处理器数量也在不断增加,这就要求芯片本身支持数十个缓存一致性端口,并在这些端口上运行异构缓存一致性协议。

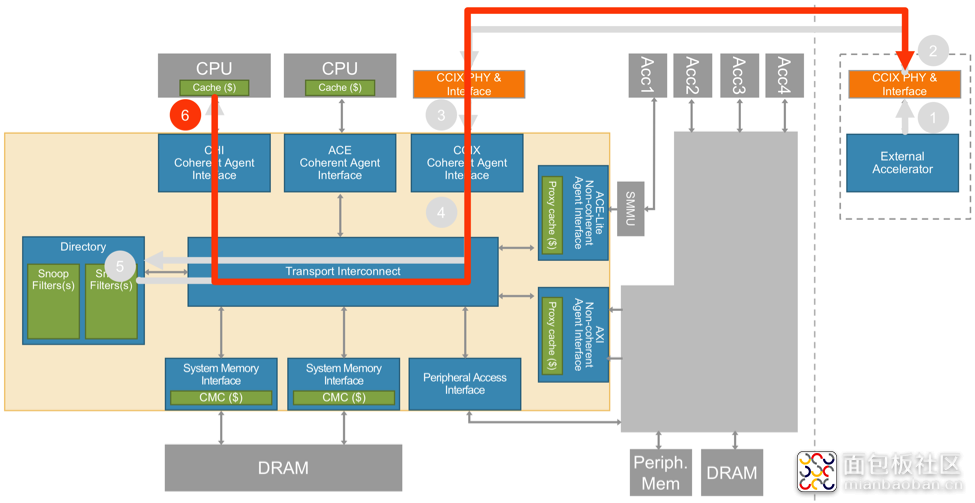

图 2:大型 SoC 设计中的缓存一致性工作原理示意图。图片来源:Arteris IP

随着多级片上缓存的使用,片上缓存存储器最多将达到四级。设计人员逐渐开始使用这种多级缓存结构来改善内存带宽,并最大程度地减少因片外内存访问带来的延迟。事实证明,随着设计人员不断寻求对内存性能的提升,高带宽内存接口的应用也变得越来越普遍。

网格状芯片

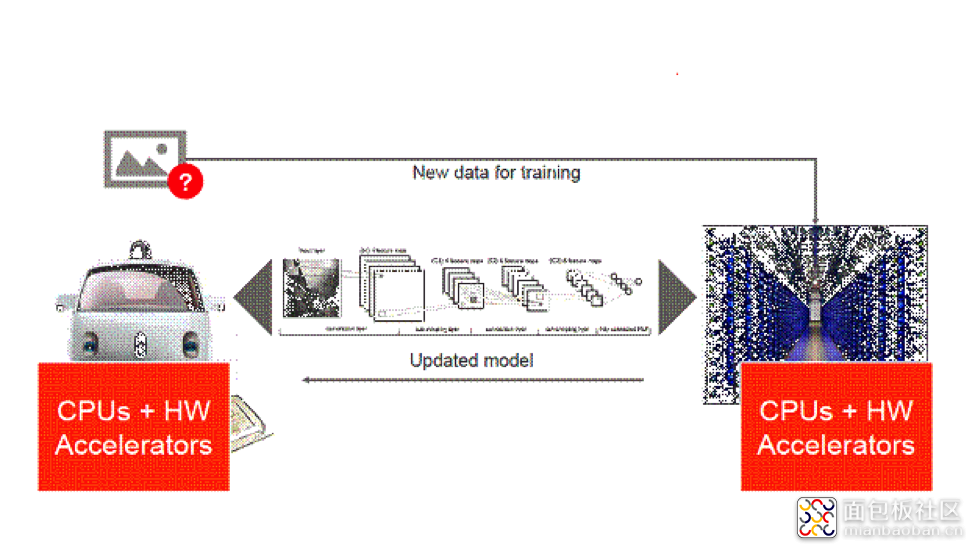

多个处理子系统往往会产生大量的数据,而这些数据必须在整个 SoC 芯片内传输。以高级驾驶员辅助系统(ADAS) 应用中目前采用的汽车 SoC 为例,该芯片内每天可生成超过 20GB 的数据。因此,在巨型芯片中,将利用多节点网格来实现片上深度学习,从而将数据转换为可操作的对象。

目前,边缘设备子系统中通常包含 20 个网格节点,而在高端人工智能 (AI) 应用中,这一数字将达到一百多个。例如,用于机器学习的卷积神经网络 (CNN) 中的网格节点数量正在不断增加,以便更好地支持训练和推理。此外,芯片设计中的挑战不仅在于如何实现 CNN 节点内的数据转换,同时也要求实现数据在节点间的高效移动。

图 3:汽车 SoC 中机器学习和神经网络架构的示例。图片来源:Arteris IP

为了有效管理这类巨型芯片的功耗水平,电源域和频率域的数量也在不断增加。此外,巨型芯片极高的复杂性也给设计工作的效率带来压力。这种复杂性往往需要引入更为便捷的 IP 块和 EDA 工具,使设计人员既能进行手动优化,又可以对非增值的复杂性因素采用自动化管理。

巨型芯片的神经系统

用于 ADAS 和自动驾驶汽车的 SoC 是巨型芯片的典型代表。自动驾驶汽车是一种由软件驱动的应用,可能需要编写多达 1 亿行代码才能实现与现实世界交通环境的顺畅交互。这类软件的配套硬件(即汽车 SoC)必须兼具高性能、低功耗、经济高效且功能安全等特点。

因此,为了实现处理子系统和存储子系统复杂性的全面提升,势必需要能够实现巨大数据带宽、低延迟和高效电源利用率的新一代互连 IP。换言之,巨型芯片推动着互连技术向 SoC 神经系统的方向发展。

处理器无疑是系统中最关键的 IP,而内存带宽则是决定一切的基础,但就目前而言,如何利用先进的互连 IP 将SoC 的各个部分组装起来,则越来越成为 SoC 设计可行性的决定因素。归根结底,互连 IP 对 SoC 的性能、成本及发展进度都将产生重大的影响。

----本文作者:Arteris IP 公司总裁兼首席执行官 K Charles Janac

Janac 先生是 NoC 技术概念的先驱者 Arteris IP 公司的总裁兼首席执行官,主要负责推动公司的全面发展,帮助企业打造强大的全球影响力。在二十年的职业生涯中,他曾涉足多个行业,其中包括电子设计自动化、半导体资本设备、纳米技术、工业聚合物和风险投资。

前十年,他就职于 Cadence Design Systems 公司 (NYSE: CDN),先后担任多个市场营销职务,帮助这家公司成功跻身全球十大软件公司行列。随后,他加入 HLD Systems 公司出任总裁一职,成功将公司的核心业务从咨询服务转向 IC 布局规划软件,使企业的管理、分销和客户支持实力得到进一步增强。之后,他创立了一家半导体自动化设备制造公司 Smart Machines,并最终将其出售给 Brooks Automation (NASDAQ: BRKS)。他还曾加盟全球领先的早期风险投资公司 Infinity Capital 担任驻点企业家,负责提供有关信息技术投资机会的咨询服务。一年后他加入 Nanomix 出任总裁兼首席执行官,帮助这家纳米技术创企实现发展。Janac 先生拥有塔夫茨大学有机化学专业的学士和硕士学位,以及斯坦福大学商学院的 MBA 学位。

/3

/3