近年来DC/DC变换器发展十分迅速,由于其效率高、体积小、可靠性高的特性,被广泛应用于手机、iPad等便携设备上。但在直流电压中,经常存在叠加在直流稳定量上的交流分量,也就是纹波。纹波容易在电子系统中产生谐波从而降低变换器的效率、干扰数字电路的逻辑关系、干扰系统的正常工作,给整个电子设备的正常工作带来非常严重的隐患。

降低DC/DC变换器的电压纹波可以通过增加电感值、滤波电容值或堆叠不同类型的电容来降低ESL(等效串联电感)和ESR(等效串联电阻)。然而,从负载暂态、阶跃响应和输入噪声辨识或线性调整率的角度来看,这必然会导致变换器尺寸的增加,并限制了整个系统的性能。

现有的研究都是在尺寸与性能之间进行妥协,只关注了无源元器件对纹波幅值的影响,而忽略了其他的性能参数,如超调量、高阶噪声谐波以及环路带宽等。例如,有的研究为低纹波条件下的最佳电感值计算提供了一种分析方法,还有的研究根据额定性能和电气等效模型提供了选择最佳无源元器件的简化分析。

1. 满足纹波要求的滤波电容的选择

DC/DC变换器的输出端滤波电容的选择取决于三个参数:

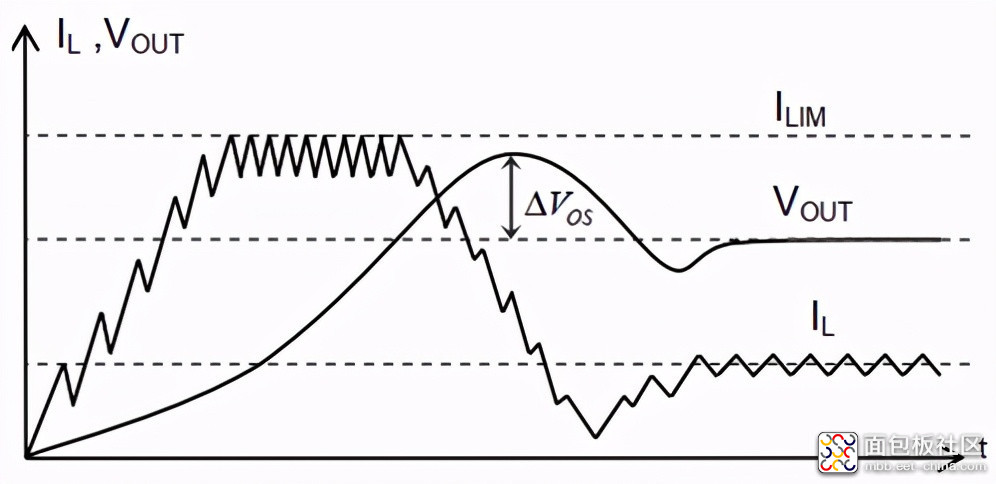

- 启动阶段结束,特别是当电感电流在稳定前达到了限制电流时的超调电压(见图1);

- 由LC滤波器形成的双极点支配的环路带宽;

- 由,电感电流纹波幅值引起的电压纹波。

变换器输出端电容大小的选择通常由电流达到极限时的电压超调量决定,因其构成了电感和电容之间能量交换的最坏情况以及调节回路最大扰动的情况。这就使得电路设计者可以通过选择电容器(如MLCC多层陶瓷电容、钽电解电容)去间接地设置在估计输出电压纹波时要考虑的主要寄生元件ESL和ESR的大小。

图1 DCDC变换器在启动阶段结束时刻的电压超调量

我们可以很好地估计在启动阶段结束时的电压超调量,从而确定输出端所需的电容值。假设在启动过程中,为防止磁场饱和或过热,电感电流的上限值为ILIM。当输出电压达到一个调节值时,储存在电感中的多余能量将全部转移到输出端电容,从而导致电压发生超调(见图1所示)。

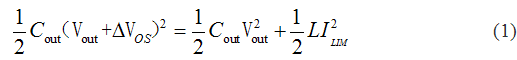

等式(1)表示在负载不吸收电流的情况下,电感L与输出端的滤波电容Cout之间的能量交换:

其中VLIM为输出电压,ILIM为电感电流的上限值,∆VOS为输出电压的超调量。

假设∆VOS相对于Vout来说很小,那么可表示如下:

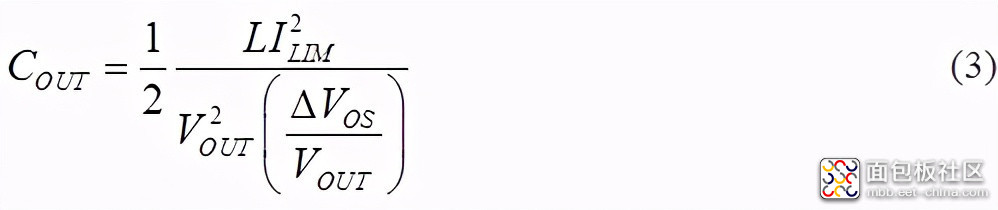

电路设计人员就可以根据等式(3)去确定输出端的滤波电容值。例如,一个输入电压为3.6 v、输出电压为1.2 v、输出电流0.5 A的buck变换器,其工作频率为6 MHz,电流上限值为1 A,电感值为470 nH,输出电压的超调量为10 %,根据等式(3)就可以确定输出端的滤波电容值为1.6 μF。

就环路带宽而言,与LC滤波器的极点位置的关系如下所示:

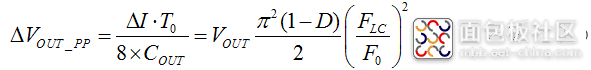

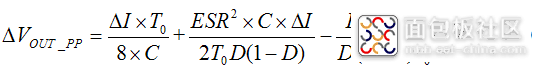

最后,由峰值表示的输出电压纹波可以写成如下形式:

其中∆I为电感电流的纹波,D为占空比,F0为开关频率,T0为开关周期。

输出电压纹波可能已经满足设计要求,而带宽则需要进一步改进,以实现更好的环路响应。在这种情况下,电路设计者可以通过电流注入和高频零补偿技术去扩大带宽。

特定应用,如模拟前端或射频功率放大器虽然允许电压超调量在瞬态阶段增加,但其对DCDC变换器的频谱非常敏感,因为它们都处于中频(IF)带宽,并系统地影响信噪比。

接下来,针对输出电压波形进行深入分析,估计电压纹波的幅值,并为确定谐波含量提供理论基础。

2. 输出电压纹波详细分析

在稳定状态下,假设电感电流的直流分量与平均负载电流相等,而交流分量被滤波电容吸收,产生输出电压纹波。

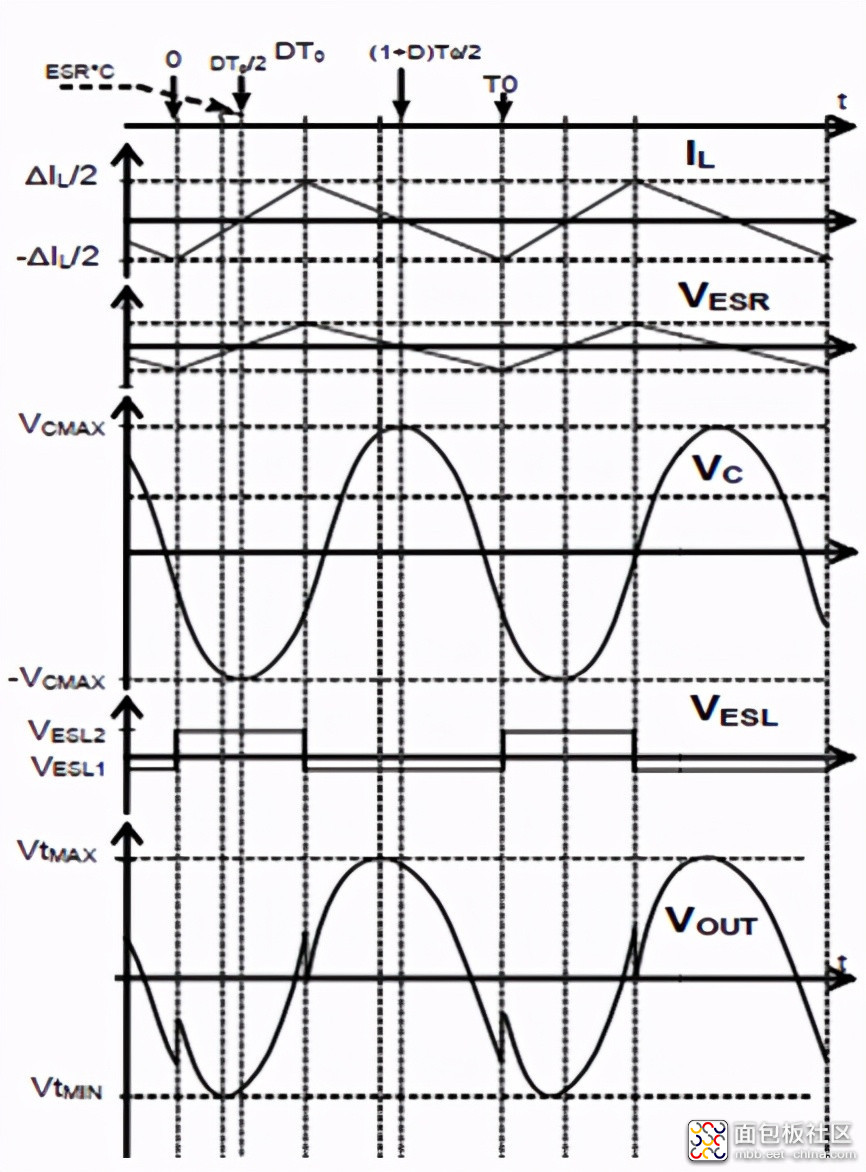

输出电压纹波由三部分组成:ESR感应电压VESR,其波形与电感电流波形相同;ESL感应电压VESL,其波形为方波,但其电感电流为三角波;输出端电容循环充放电形成的VC(见图2)。

图2 寄生元件对DCDC变换器输出电压纹波的影响

图2所示的相应波形突出了各分量对整体纹波的影响,在图2中假设ESR效应比电容器本身产生的电压小一个数量级,而ESL感应电压对电容电压的影响较大,这尤其适用于在高频DCDC变换器中使用的MLCC电容器。更有趣的是,ESL引发的纹波会改变输出纹波的大小,同时引入尖锐的电压变化,增加高频和不良频谱含量。

输出纹波的总幅值如下所示:

等式(6)凸显了ESL在减少纹波幅值方面的作用。

3. 输出纹波的频谱

在射频发射机中,由于RFPA(射频功率放大器)的非线性行为,DCDC变换器的纹波电压会干扰载波频率。系统的互调干扰通常是由二阶和三阶互调导致。由于载波频率(FTX)和DCDC(F0)变换器的开关频率相差较大,所以必须考虑直接混合效应(FCarrier±F0)、(FCarrier±2F0)、(2FCarrier±F0)。

作为约束,电路设计者必须防止与相邻信道的任何干扰,其中RFPA必须放弃33 dBc(第一信道)。

电路设计者可以使用该理论来对DCDC变换器的行为进行建模,以更好的估计ACLR(相邻频道泄漏比)。

使用傅立叶变换,纹波电压的频谱可以写成如下形式:

其中:VESR(nF0)、VESL(nF0)、VC(nF0)分别表示ESR、ESL以及电容电压的离散傅里叶变换。

从上述的频谱研究中再次验证了ESL能够降低电压纹波的幅值。

4. 实验分析

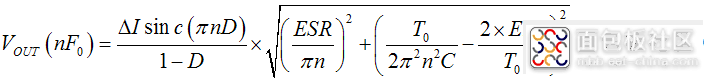

为了验证上述理论的正确性,作者构建了一个开关频率为2 MHz的Buck变换器的实验装置,并将测量结果与使用Cadence® Spectre的仿真结果进行比较。

表 1 DCDC变换器的参数

其中COUT和L的值是经过测量得来的,ESR的值是由数据表提取而来的,ESL的值则由输出电压的锐边估计而来。

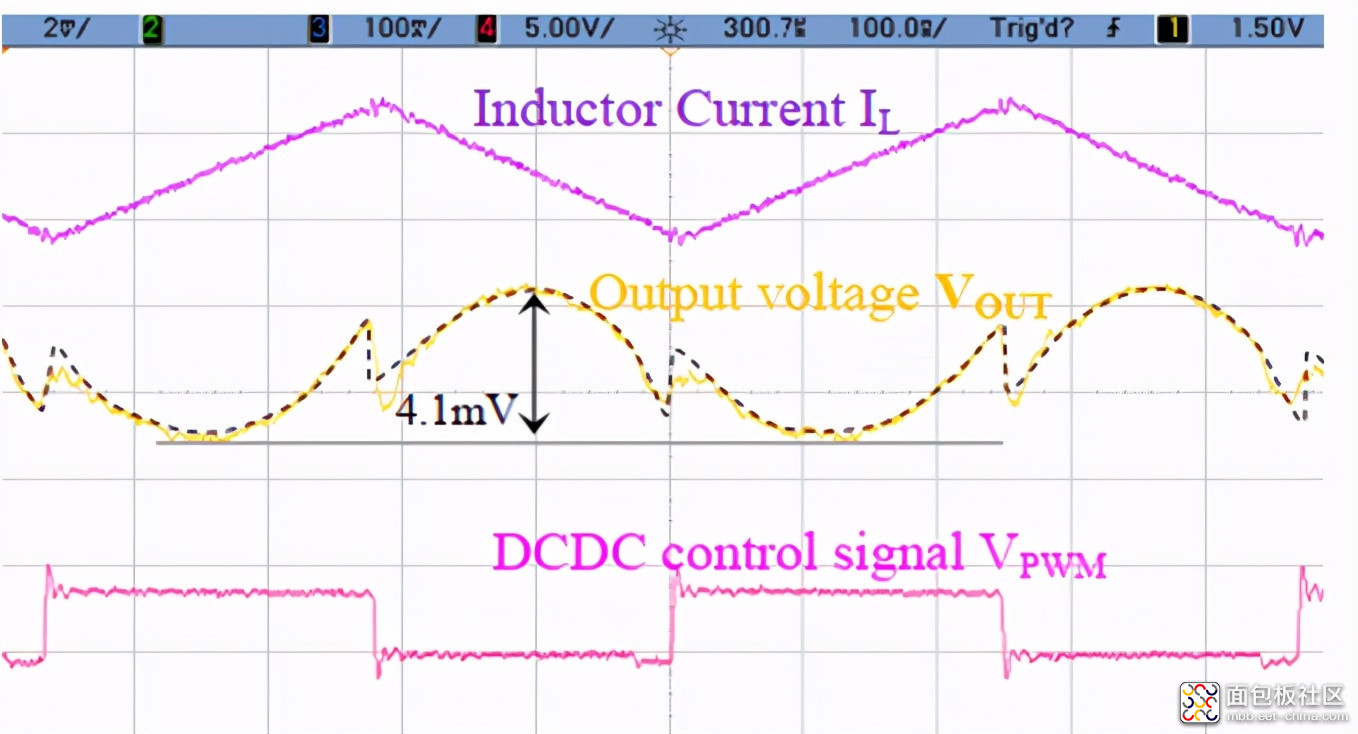

图3 Buck变换器的实验结果(虚线为期望输出电压波形)

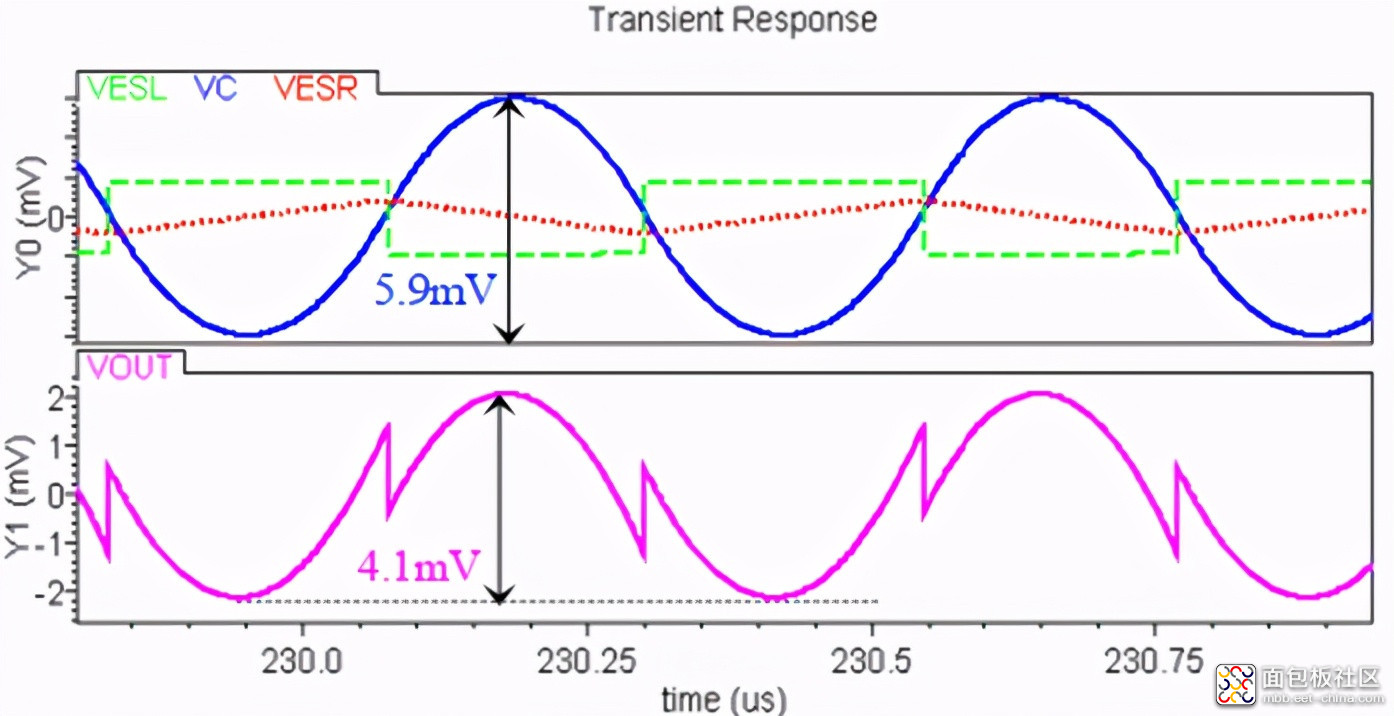

详细的仿真波形如图4所示。

图4 输出电压(VOUT)仿真波形及电容模型的每个元素对输出电压的贡献图

当不考虑ESL以及ESR时,经过输出端电容COUT的纹波电压为5.9 mV,但由图4可见,实际上仅为4.1 mV。

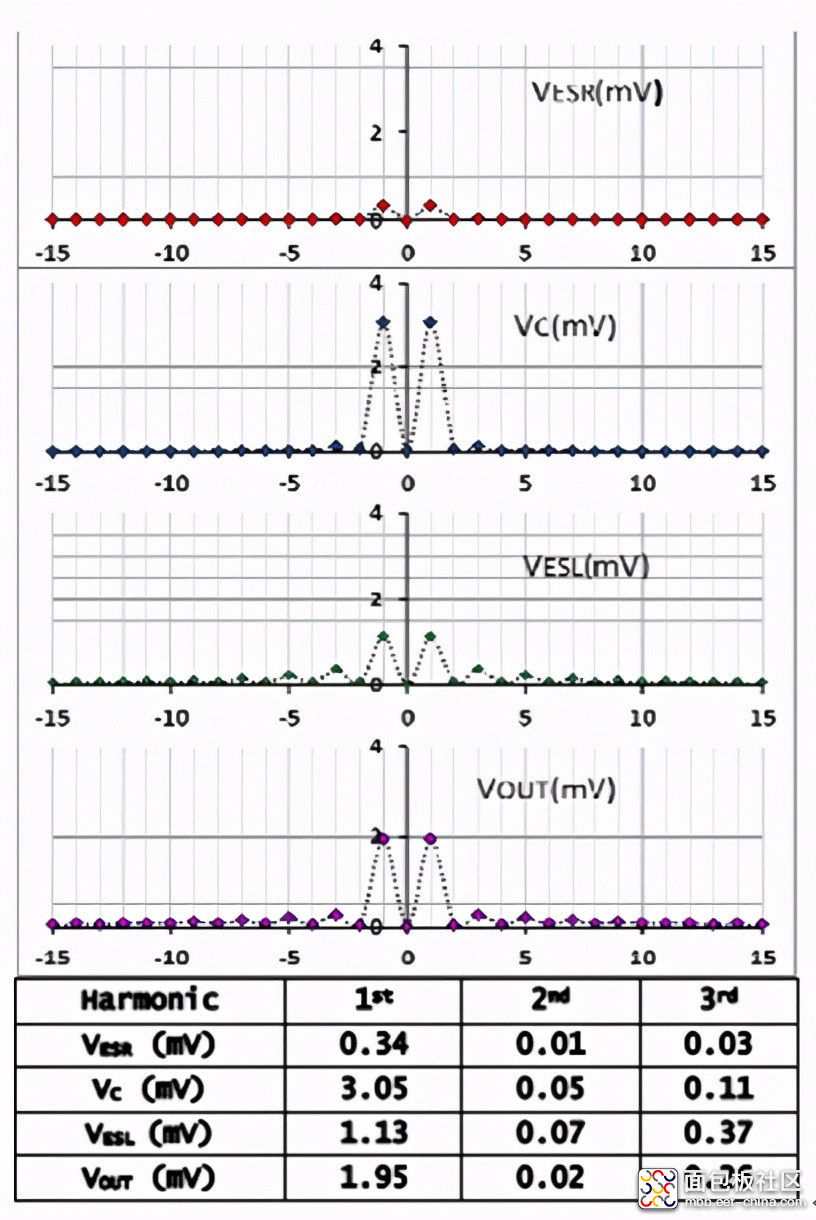

最后由同一个testbench仿真得到的纹波电压的频谱如图5所示。

图5 输出电压的详细频谱内容

由上述频谱可见,与理想输出端电容相比,一次谐波的幅值更低。而二次谐波对输出电压的贡献要远低于三次谐波。

5. 总结

本文分析了DCDC变换器输出端电容对输出电压超调量、带宽以及输出纹波电压的影响。然后进一步研究了输出纹波,并描述了输出端电容对输出纹波的影响。电容的ESL对纹波电压具有主导效应,其中它可以降低纹波幅值,增加频谱中的高频部分;最后通过实验以及仿真验证了分析。

/5

/5