射频板设计PCB叠层时,推荐使用四层板结构,层设置架构如下

- 【Top layer】射频IC和元件、射频传输线、天线、去耦电容和其他信号线,

- 【Layer 2】地平面

- 【Layer 3】电源平面

- 【Bottomlayer】非射频元件和信号线

地平面设计规则

- 作为射频信号线镜像回流地的平面要完整,并且独立定义,同时不要有任何其他信号线在地平面上布置;

- 对于Top Layer和Bottom Layer空白部分,建议做铺地处理,并且通过间距不大于λ/20的过孔将各部分地连在一起;

- 对于高密度电路板(例如含CSP封装)不建议使用2层电路板,尽可能采用4层板进行设计;

- 尽量不要将地平面做分地处理,除非保证在地平面上电流不会形成环流;

- 射频信号线下的地平面要尽可能的宽,地平面过窄会引起寄生参数同时增加衰减;

- 地平面、顶层的地已经连接两层的过孔,应尽量保证射频信号线做到完全的“屏蔽”,以增加产品的EMC能力。

- 同时建议通过地孔将电源平面包裹起来,避免不必要的电子辐射。

通常电源层相对于地层需要满足“20H”原则,“20H原则”是指要确保电源平面边缘比地平面(0V参考面)边缘至少缩进相当于两个平面之间间距的20倍,其中H就是指电源平面与地平面之间的距离,在20H时可以抑制70%的磁通泄漏,有效的提升EMI性能

射频设计难题「电源退耦篇」

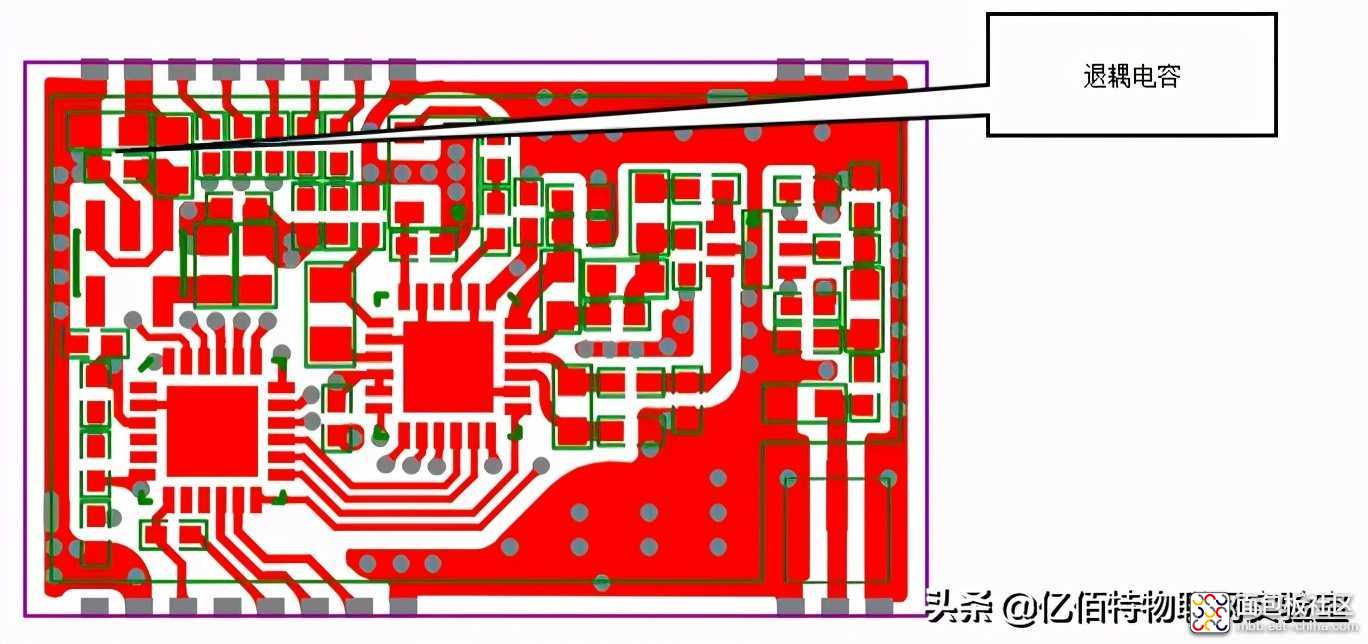

电源供电需要通过退耦电容滤除电源的噪声,如图,避免噪声在不同设备(IC)之间流转,同时电源噪声会增加频率合成器的相位噪声,降低接收机的接收灵敏度,增加信号的杂散,对电路性能具有诸多不利影响。

电源退耦建议

- 退耦电容放置离电源越近越好;

- 退耦电容容值越小离供电管脚越近,为了达到对不同频率噪声进行退耦,常使用一大一小的电容组合;

- 尽量将退耦电容和电源设置在同一个平面,如果无法将所有的电容放置在同一个平面,优先小容值的电容;

- 供电电源经过退耦电容后进入IC,在退耦电容和IC管脚之间不要放置过孔。

- 为每个退耦电容就近连接到地,尽量避免共用地过孔。

- 对于设置了独立电源层的电路板,使用独立的过孔为每个用电“单位”供电,不要共用电源过孔。

射频设计难题「过孔」

过孔是连接不同信号层的关键“装置”,然而他具有极高的寄生参数,会带来很多寄生干扰和问题。

过孔规则

- 使用尽可能的多的过孔连接不同层,且间隔不大于信号波长的λ/20;

- “地孔伴随”,在信号线附近设置尽可能的多的过孔,以降低过孔的寄生电感,如图;

- 焊盘和焊点不要共用过孔,尽量独立;

- 尽量避免射频信号跨层;

- QFN封装的器件,其底部焊盘尽可能多的过孔;

- 可以使用地孔来隔离干扰源和敏感电路;

电源和地的引脚推荐就近打过孔,过孔和引脚之间的引线越短越好,越短其寄生参数对电路影响越小。

来源:亿佰特物联网实验室

/5

/5