长期以来,片外存储器的访问速度难以满足计算机处理器的需求,由此造成的内存墙问题极大地制约了处理器的性能。为了缓解内存墙问题,处理器芯片提供了高速访问数据的高速缓存,高速缓存的访问速度一般比片外存储器的访问速度快两个数量级。然而,受限于制造成本等因素,高速缓存的存储空间有限.计算机体系结构的研究者们提出在高速缓存中使用硬件数据压缩单元,以提升高速缓存的有效存储空间.基于这个构想,众多缓存压缩技术应运而生.有些缓存压缩算法着重针对特定的数据类型,比如计算机应用程序在运行过程中产生的零数据和重复数据等。此类算法硬件开销小,但是无法压缩非特定类型的数据.另一些缓存压缩算法致力于提升数据的压缩比,利用字典编码和熵编码技术降低数据冗余度,代价是复杂的硬件结构和更长的压缩/解压缩延时.在众多压缩算法当中,BDI(Base—Delta—Immediate)压缩算法利用高速缓存行内数据差异小的特点,在数据压缩比、硬件开销以及压缩/解压延时之间取得了良好的折衷。

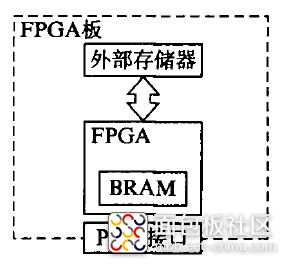

与计算机处理器类似,现代的现场可编程门阵列(Field Programmable Gate Array,FPGA)也采用多层次的存储结构。如下图所示,FPGA芯片集成了大量的块随机存取存储器(Block Random Access Memory,BRAM)作为片内高速缓存。由于成本与功耗等方面的限制,FPGA芯片上的BRAM空间有限。所以,FPGA片外存储器有限的带宽和高访问延时也成为制约FPGA应用的性能瓶颈之一。而数据压缩技术能够有效地缓解FPGA的这一性能瓶颈。

以往对FPGA压缩算法的研究主要考虑提升FPGA片外存储器和高速缓存之间的带宽。为了追求高数据压缩比,许多研究者将各种复杂的数据压缩算法应用到FPGA上:Sukhwani在高速串行计算机扩展总线标准(Peripheral Component Interface Express,PCIE)接VI的FPGA板上实现了842B算法,极大地提升了FPGA的吞吐量;Guan使用混合熵编码算法压缩卷积神经网络(Convolutional Neural Network,CNN)参数加速数据传输速率。然而,增加有效带宽是以牺牲大量硬件资源和数据访问速度为代价的。某些图像/视频处理、高性能计算和神经网络等应用对于计算过程的中间结果有强实时性的需求,复杂压缩算法造成的高延时可能会抵消提升有效带宽所带来的收益。

另一个有效提升FPGA性能的策略是把更多数据缓存在FPGA的高速缓存之中,从而有效降低访问片外存储器的频率。目前,我们还没有发现高速缓存压缩技术应用于FPGA的相关研究。本文基于BDI算法,提出了一种新颖的适用于FPGA的快速在线数据压缩的页式高速缓存(Page Cache,PC)压缩方法。与计算机处理器相比,FPGA访问数据的粒度更为粗糙,访问模式也更为规则。比如,许多FPGA的图像应用访问数据的粒度是一行或者64×64的像素块。针对这一粗粒度的特点,我们提出页式高速缓存压缩算法(Page Cache Compression,PCC),将数据适当切割为多个数据段(segment),并确保每个数据段能被压缩为标准大小的高速缓存行,从而避免其他缓存压缩技术压缩数据后导致的内存碎片化问题.此外,我们还提出了简化的页式内存管理系统,以解决以往新旧数据替换时存储空间不足的问题。实验结果表明,所提出的页式高速缓存压缩算法消耗硬件资源少,压缩/解压缩延时低,能够有效地压缩图像和矩阵数据,从而提升FPGA应用的性能。

/1

/1