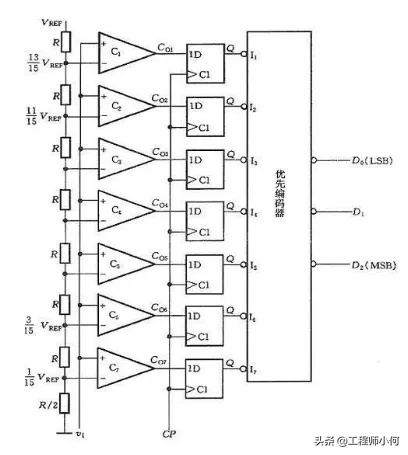

并行比较型ADC采用直接转换的转换方式。它由分压器、比较器、寄存器及编码器组成。图1为3bit ADC:

图1 并行比较型ADC

原理:

根据电阻分压把参考电压分为八个等级。假设最下边比较器C07的参考电压为V0(V0=1/15Vref),则依次往上电压为3V0、5V0、7V0、9V0、11V0、13V0、15V0八个等级。输入电压范围为0~Vref。当处在某一个值时,所有比较器同时动作。例如,Vin=0.5Vref=7.5V0。C04-C07的负端比正端小,输出为1,送入寄存器中。而C01-C03的负端比正端大,输出为1,送入寄存器。送入编码器入口的数字为:(0)0001111,在通过编码器,出来的二进制数为100(B)。

优缺点:

我们可以看到,比较器是同步工作的,因此转换速度非常快,响应速度值取决于门电路的延迟。而显而易见的是,它的缺点在于,如果增加ADC的位数,则内部比较器和寄存器的数量是几何级数增长。3bitADC需要7个比较器,而4bit则需要15(2^4-1)个,8bit则需要255个比较器,导致芯片的面积和成本骤增。

改进:

由于增加位数导致面积和成本的大幅度增加,因此出现了分级的ADC。严谨的说,这种ADC并不是完全的并行了,而是多个并行ADC通过分级串接在一起,例如两个4bit的并行ADC分级接起后,则可以设计出8bit的比较器。而元件数量则比真正8bit的并行ADC要大大减少。然而,这样做由于分级了,所以也是牺牲了转换速度的一种综合考量的结果。

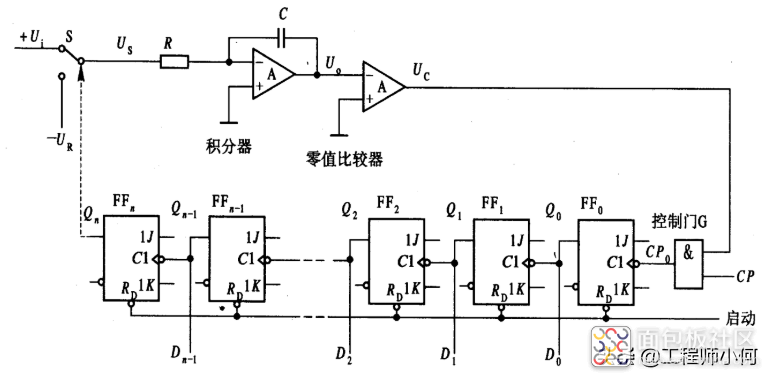

2. 双积分型ADC

双积分型ADC属于间接ADC,采用正反方向两次积分。它是由积分器、比较器、计数器和时钟门电路组成。图2为双积分型ADC。

图2 双积分型ADC

简单来讲原理是先把输入的模拟信号按比例转换成相应的时间间隔,再在该间隔内用计数器对固定频率的脉冲计数,计数值即为输出的数字信号。

原理:

把输入的模拟信号+Ui给到积分器做积分,这时由于积分器负端>正端电压,因此输出Uo<0。Uo送入比较器负端,比较器负端<正端电压0,因此输出Uc=1。Uc为门电路G的导通信号,当Uc=1时,将脉冲信号CP送入输出端CPo。门电路输出端接n位计数器Qn,进行第一次正向积分,直至n位计数器D0~Dn-1输出均为1后,再进一位则全部清零,Qn输出1。Qn为开关S的控制信号,输出为1时,控制开关S打到-Ur处,此时正向积分结束。完成第一步把模拟信号转换成时间间隔。

当正向计分结束时,Uo的输出为Us积分后的输出量,为一个固定正值Uo1。随着输入变成-Ur,积分器开始做负向电压积分,此时Uo逐渐减小。Uo为正值时,Uc一直为1,则计数器从清零之后一直计数。直到Uo因为负向积分,最终减小到0时,比较器正负端电压相等,则输出Uc=0。Uc=0,门电路关断,输出CPo=0,计数器停止计数。此时,计数器的数值,则为+Ui信号通过负向积分放电至0之后的数字信号数值。即完成AD转换。

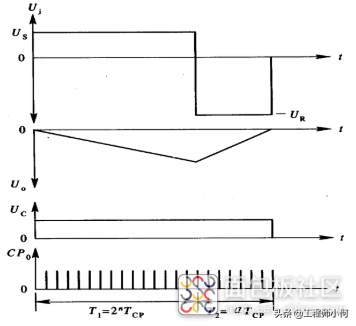

各模块输出波形如图3所示:

图3 双积分型ADC各阶段输出

优缺点:

正向积分时,时间是固定的,转换结果与RC参数无关,因此,双积分ADC具有强干扰性。而由于每次测量都会做正反两次积分,因此速度也很慢。

应用:

由于双积分ADC的特点,主要应用于低速高精度的电路中。较为常见的为数字万用表。

来源:手机射频驿站

/1

/1