本文主要介绍说明XQ6657Z35-EVM评估板Cameralink回环例程的功能、使用步骤以及各个例程的运行效果。

(基于TI KeyStone架构C6000系列TMS320C6657双核C66x 定点/浮点DSP以及Xilinx Zynq-7000系列SoC处理器XC7Z035-2FFG676I设计的异构多核评估板,由核心板与评估底板组成。评估板CameraLink功能支持2路Base输入、或者2路Base输出、或者1路Full 输入或输出)

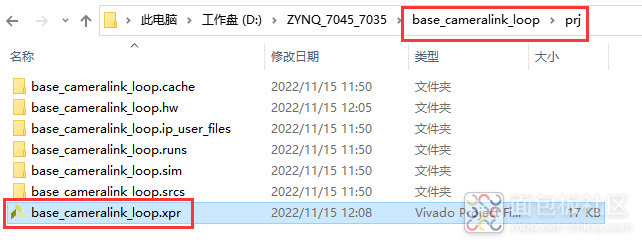

ZYNQ例程保存在资料盘中的Demo\ZYNQ\PL\base_cameralink_loop\prj文件夹下。

Cameralink回环例程将J3、J4当作两个独立的Base Cameralink接口使用,一个接收,另一个发送。

Cameralink接收端,利用Xilinx ISERDESE2原语进行串/并转换,将LVDS串行数据转换成28bit的cameralink并行数据。解串后的并行数据通过ila进行在线分析和查看,并实时检测并行数据是否有误码。

Cameralink发送端,利用Xilinx OSERDESE2原语进行并/串转换,将本地28bit cameralink并行数据串行化为LVDS数据发送出去。

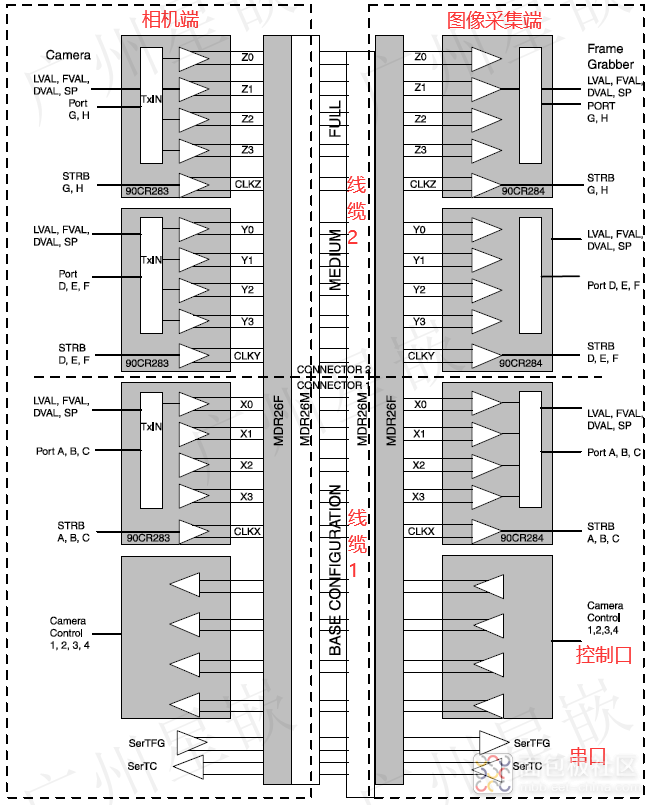

Base模式:只需一根Cameralink线缆;4对差分数据、1对差分时钟;

Medium模式:需要两根Cameralink线缆;8对差分数据、2对差分时钟;

Full模式:需要两根Cameralink线缆;12对差分数据、3对差分时钟。

各种模式下,统一都包含一组控制口和一组串口。控制口有4根信号,用于图像采集端对相机的IO控制;串口用于图像采集端对相机参数的配置。

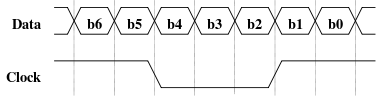

单路Cameralink差分数据与随路的差分像素时钟之间的时序关系如下图所示:

一个时钟周期内传输7bits串行数据,首先传输串行数据的最高位,最后传输串行数据的最低位。7bits数据起始于像素时钟高电平的中间位置,即数据的最高位在Clock高电平的中间时刻开始传输。

Clock高电平时间比Clock低电平时间多一个bit位。

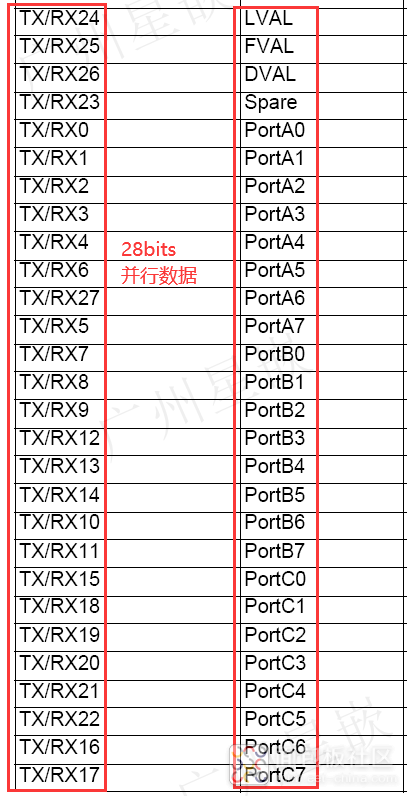

1路差分数据通道上,一个Clock像素时钟周期传输7bits串行数据,那么4路差分数据通道总共就是4*7bits=28bits,我们称这28bits数据为并行数据,为了方便描述,这28bits数据记为TX/RX27~0。Cameralink Base模式下,这28bits数据与图像行/场同步/数据有效标记、图像数据的映射关系如下图所示:

TX/RX24映射为行同步标记LVAL,TX/RX25映射为场同步标记FVAL,TX/RX26映射为图像数据有效标记DVAL,TX/RX23未使用,其余位对应图像数据。

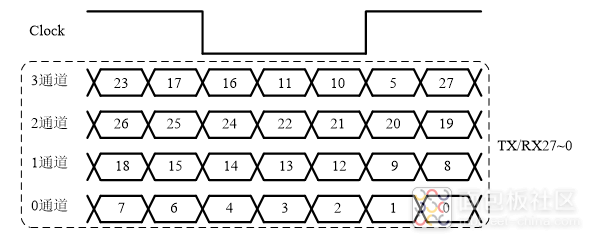

上述28位并行数据是如何通过4路差分数据传输通道进行传输的呢?28位并行数据映射到4路差分数据传输通道各个时刻点的位置关系如下图所示:

1.1.4 管脚约束

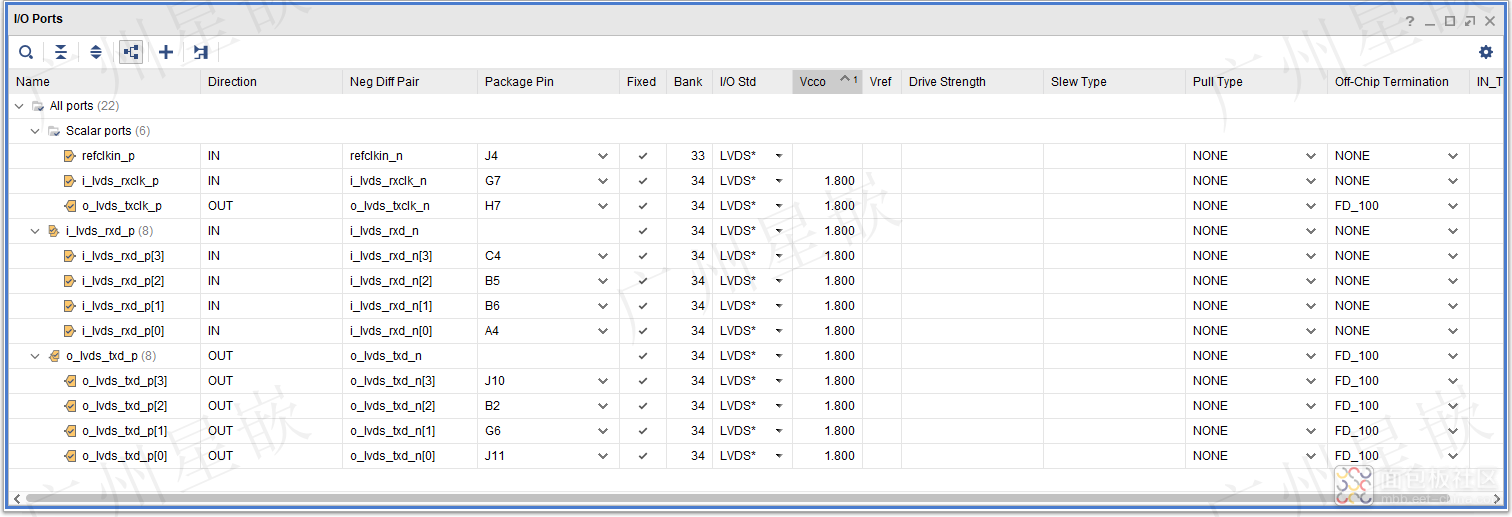

ZYNQ PL工程管脚约束如下图所示:

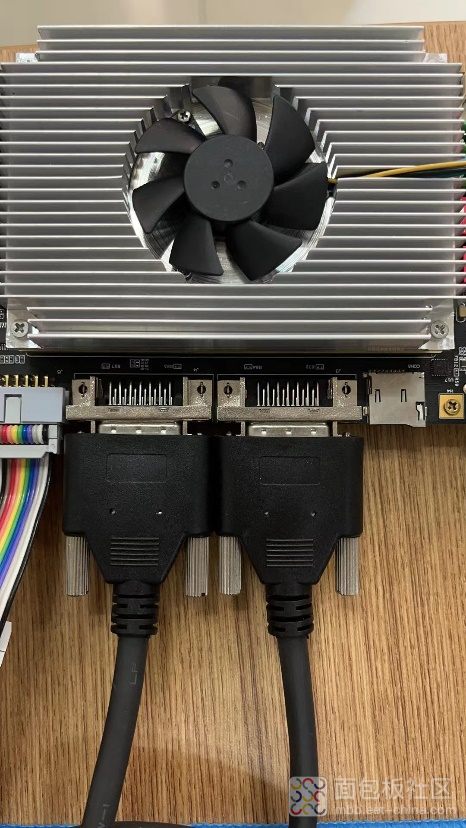

使用Cameralink线缆将J3、J4两个接口连接在一起:

打开Vivado示例工程:

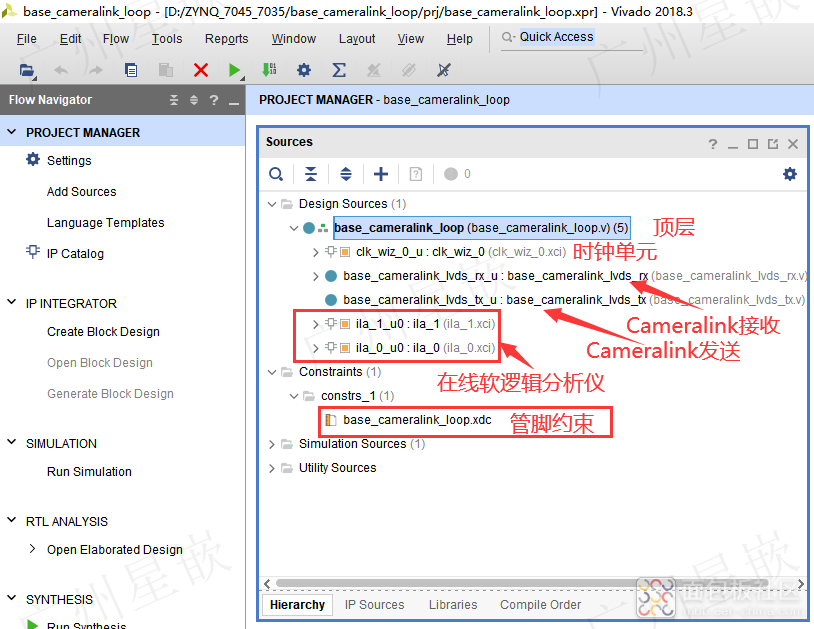

工程打开后界面如下图所示:

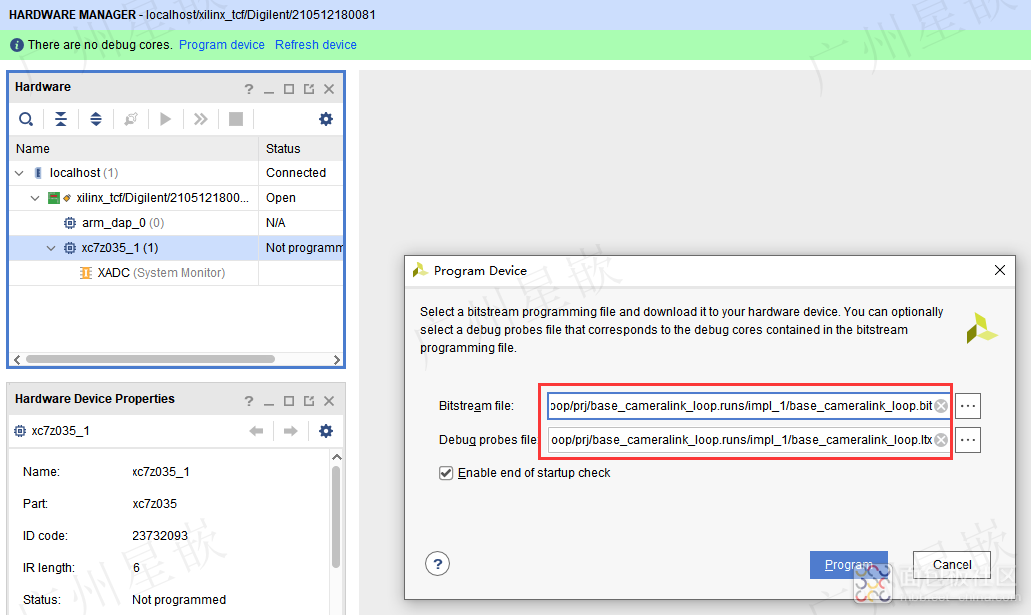

下载bit流文件base_cameralink_loop.bit,并且配套base_cameralink_loop.ltx调试文件,如下图下载界面所示:

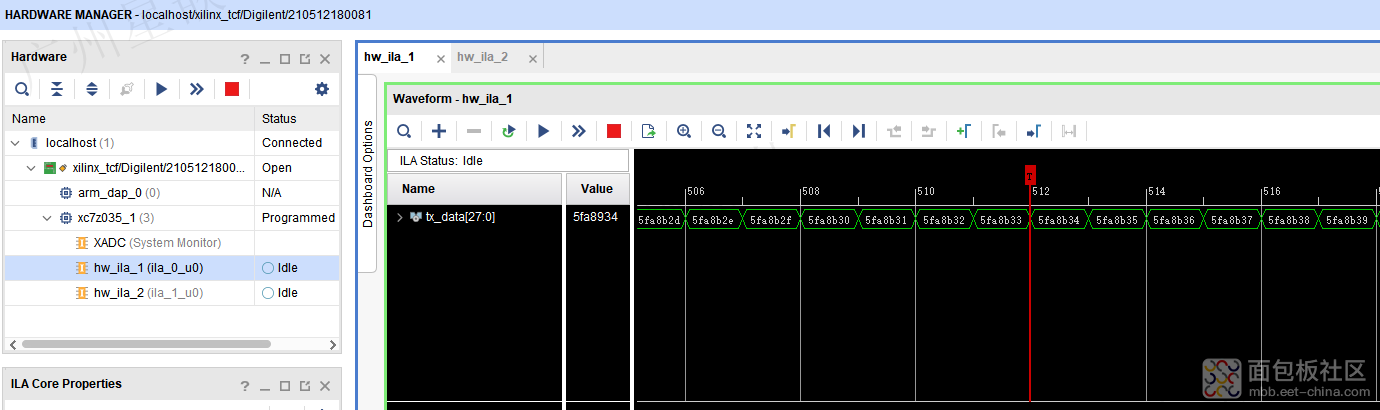

ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集Cameralink并行信号以及错误检测信号的时序波形。

hw_ila_1调试界面抓取Cameralink并行发送数据,是一个28bits的累加数:

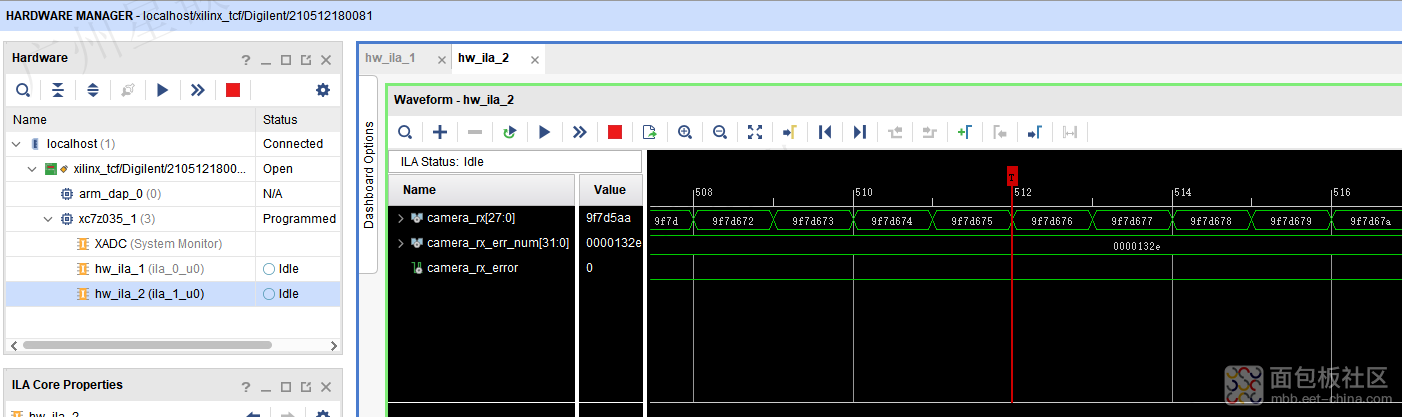

hw_ila_2调试界面抓取Cameralink并行接收数据、接收误码统计以及接收误码实时标识信号,如下图所示:

cameralink_rx_err_num显示有数值,则说明Cameralink接收过程中存在误码。可能在开始通信初始化期间存在误码现象,导致cameralink_rx_err_num误码统计累加。待程序下载完毕后,如果Cameralink通信正常的话,cameralink_rx_err_num误码统计应该不会再累加。如果cameralink_rx_err_num误码统计继续不断累加,则通过触发camera_rx_error信号可以捕捉到误码具体发生时刻。

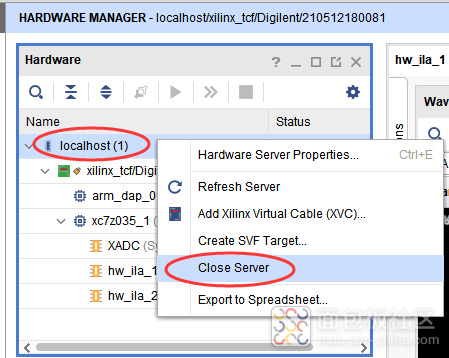

Vivado调试界面Hardware Manager窗口,右键单击localhost(1),在弹出的菜单中点击Close Server,断开ZYNQ JTAG仿真器与板卡的连接:

最后,关闭板卡电源,实验结束。

ZYNQ PL Cameralink回环例程.pdf

(1.32 MB, 下载次数: 0)

ZYNQ PL Cameralink回环例程.pdf

(1.32 MB, 下载次数: 0)

继续阅读本篇相关更多标签

热门资料

热门活动

全部回复 0

暂无评论,快来抢沙发吧

暂无评论,快来抢沙发吧

/3

/3