区域1是SRC区域,模块通常在48V以下输出时工作在这一区域,在这一工作区域中,谐振电路同样可以达到ZVS开通,只是随着工作电压的降低,关断电流越来越大,关断损耗也随着增大。

区域3是ZCS区域,通常发生在过载或短路瞬间,因为在这一区域中,一个工作电压对应于两个频率点,环路存在不单调性,因此是设计时需要尽量规避的区域。

虽然采用全桥电路,但LLC谐振参数的设计与半桥电路并无本质区别,均遵循效率指标,负载要求,外特性曲线和环路的单调性等一些原则,并结合磁性器件的设计来寻求最优化的参数。

全桥LLC电路参数设计原理

LLC谐振电路参数选择是一个折中的过程,需要结合输入电压范围,输出电压范围,负载范围,效率指标以及器件设计和选型等寻求一个优化的结果,具体的需要通过matchcad计算,saber仿真,并最终结合实验来调整和优化参数,满足规格书的各项指标。

LLC谐振电路需要确定三个主电路参数,分别是谐振电感Lr,谐振电容Cr和励磁电感Lm。三个参数相互关联,更改任何一个参数,都会涉及到整个电路工作状态的改变,因此需要纳入统一的范畴来考虑。

因此必须结合LLC谐振电路的特性,考虑LLC谐振参数设计必须遵循的一些原则,从众多的参数中初步筛选一些较合理的参数。

低压大电流输出是非常恶劣的情况,由于开关频率接近谐振频率的2倍频,MOSFET关断电流很大,且开关频率较高,MOSFET的关断损耗急剧增大,导致MOSFET的散热问题非常突出,并可能导致炸机问题。因此要求在全输出电压和全负载范围内,电路的工作频率范围越小越好,最高频率必须考虑低压大电流情况下MOSFET的损耗和热,并要求在较低的输出电压下(比如20V输出)仍然保持调频控制而不是进入调宽态。

全桥LLC设计要点

在功率密度越来越高的情况下,减小磁性器件的体积是非常必要的,这会给整个模块的布局带来非常大的便利。为了尽可能的提高效率,改善模块内部散热,磁性器件的损耗也必须尽可能的小,同时损耗的降低也使得磁性器件使用B级绝缘材料成为可能,可以进一步降低制造成本。另外还需要从绕制工艺和工时方面考虑电感和变压器的成本,这些都需要体现在磁性器件的设计当中。

磁性器件的设计难点在于损耗与热,这两个互为一体,同时也是整个DC/DC电路的设计最难点。

对于LLC谐振电路而言,由于采用调频控制,不同的输出电压和负载条件都对应着不同的工作频率,因此磁性器件的工作范围非常宽,工作频率从170kHz至450kHz,在任何一个工作点均必须保证磁性器件的热设计满足降额要求或稳定性要求,否则整流模块的可靠性就无从保证。

磁性器件的设计遵循以下步骤:

1) 计算;

2)仿真;

3)优化。

根据整流模块规格书要求,结合整体布局考虑,确定磁性器件的基本尺寸(可以有多种方案),通过mathcad进行损耗计算,从而初步得出磁性器件的损耗,进行对比和筛选。

通过ansoft磁性器件仿真平台,对不同方案的磁性器件进行损耗仿真,得出不同磁芯和不同绕组结构的损耗结果,该结果较为接近真实情况,可以对计算结果进行修正,获得更为优化的方案。

根据损耗计算和仿真,进行模块整体布局的热仿真实验,从而得出热设计的裕量,以此为依据考虑是否要进一步优化设计磁性器件或优化模块布局。

在上述计算和仿真的基础上,打样实物器件进行效率和热测试,验证设计是否合理,并在此基础上进一步进行优化。

2. 热设计关系到整个整流模块的可靠性,对于通信电源整流模块而言,工作环境恶劣,通常要求在45度环温下还能够满功率输出,输出电压范围宽广,必须满足42V~58V范围内的各种工作条件,由此对模块内部的热设计提出了更为严格的要求。

对于LLC谐振电路而言,有几个必须重点关注的热风险:低压大电流下的开关管发热;低压大电流下的谐振电感发热;低压大电流下主变线包发热;58V满载条件下主变磁芯发热。

3. 因为在低压大电流工作状态下,开关频率接近谐振频率的2倍频,开关管的关断电流接近峰值,由此造成开关管的关断损耗增大,造成较大的热风险。

减小MOSFET关断损耗的方法是在开关管两端并联电容,等效的加大开关管的结电容,这样在关断的暂态过程中,可以延缓开关管DS两端电压的上升时间,错开电流下降和电压上升的交叠区域,从而减小关断损耗。

传统的电感均采用骨架(有骨架磁性器件)或线包(无骨架磁性器件)紧贴磁芯中柱或边柱的绕制方法,且采用立式放置,磁芯被包裹部分垂直于风道方向,如下图所示。

传统的设计方法主要有以下两个缺陷:1)中柱或边柱被骨架或线包紧紧包裹,热量易累积而得不到有效的发散;2)骨架(或线包)紧贴中柱或边柱,导致磁芯被包裹部分磁通分布很不均衡,磁通密度较大的区域形成局部热点,增加了磁芯内部温度分布的不均匀,易导致局部过热。

针对以上设计难点,为了保证磁芯的热稳定性和开关电源模块的可靠性,采取以下新的技术方案来改善磁芯的局部热点,并加强散热效果,从而使磁芯的温度保持在合理的范围之内。

具体实施方法参见下图:

5. 低压大电流下主变的线包发热主要是由于主变寄生参数与PCB寄生参数(引线电感)振荡引起的,下图是理想情况下主变原副边电流仿真波形:

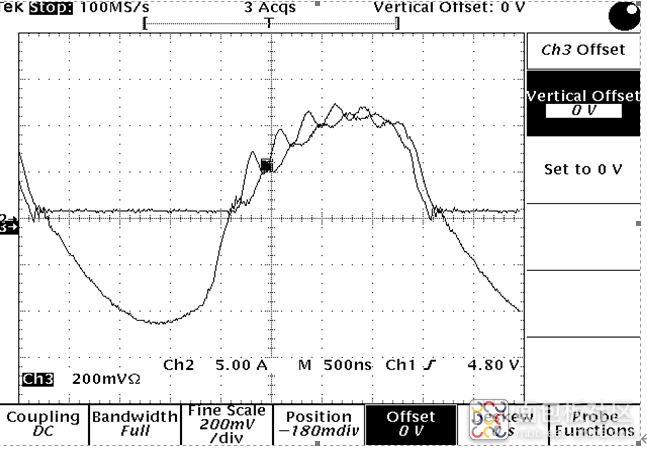

如果考虑主变原副边漏感,原副边寄生电容等寄生参数,仿真42V×61A输出条件下原副边电流波形如下图所示:

主变寄生参数是绕制方法和绕组结构固有的特性,通过绕组结构的改变,并不能显著的改变这些寄生参数的分布,因此最终是通过缩小整个绕组的体积,从而缩小绕组的交流阻抗,从而达到解决主变绕组低压大电流下的发热问题。

/3

/3