1、Verilog HDL模块编写

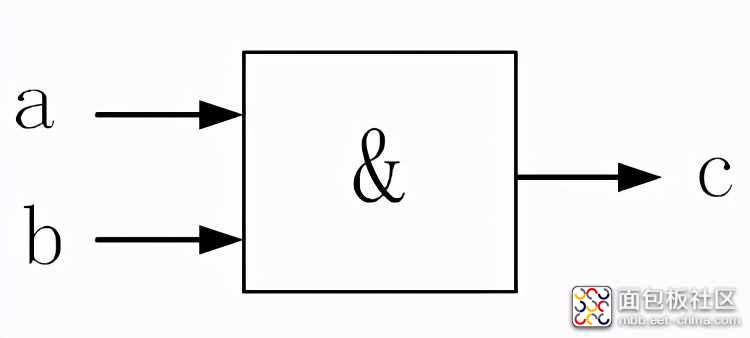

我们知道Verilog HDL是一种硬件描述语言,那么如何做到通过该语言对硬件电路进行描述呢,下面我们给出一个简单的硬件电路,如图1所示,我们需要通过Verilog HDL描述方框里面的内容,即实现一个与门,有两个指向该方框的箭头,我们称之为该硬件电路的输入,一个不指向该方框的箭头,称之为输出。其中输入分别取名为a和b,输出为c。

图1 硬件电路

根据图1的硬件电路,我们给出相应的Verilog HDL代码:

module a_and_b(

input wire a,

input wire b,

output wire c);

assign c = a&b;

endmodule

从图1我们知道需要描述的硬件电路其实就是一个封闭的方框,因此我们写的代码以module开头,并且以endmodule结尾,两者之间是我们需要描述的具体电路内容,而module和endmodule像极了那个方框,将所有的代码内容包含在其中。module后面的a_and_b是我们给该电路取的名字,在此建议最好取相对符合该电路特点的名字,这样方便我们看到名字就可以大概了解该电路的功能,由于我们需要描述的电路为a和b进行相与,因此我们取其名为a_and_b。输入a和b,输出c,若这三个外部的信号想要与该电路进行交互,我们就需要将其定义为相应的端口,在模块名a_and_b之后有个括号,括号内即为端口的定义部分。其中input和output都为Verilog HDL的关键字,input代表输入类型的端口,output代表输出类型的端口,wire同样为Verilog HDL的关键字,其为变量类型,代表的是线性,由于a、b、c都为一条线,因此我们定义它们为线性变量(wire),在此我们需要知道,定义端口(input或output)的同时也需要定义它们的变量类型,若是不定义变量类型,则默认为wire型,具体的变量类型,我们以后再讲。端口定义需要用半角逗号隔开(英文逗号),最后一个端口后面不可以加逗号。定义完端口后,括号外面的分号表示一条语句的结束。

语句c = a&b表示将等号右边的a和b进行相与,结果赋值给等号左边的c变量,这一点和c语言的运算一样,但是在Verilog HDL中仅仅这样是不行的,想要实现一条一句,那么是需要一些关键字的配合,assign就是该条语句执行的关键字,因此我们需要在c = a&b的前面加上assign,跟c语言的语句结束一样需要用分号作为标志。

2、ISE软件使用

2.1 建立ISE工程

打开ISE,界面如图2所示。

图2 ISE软件主界面

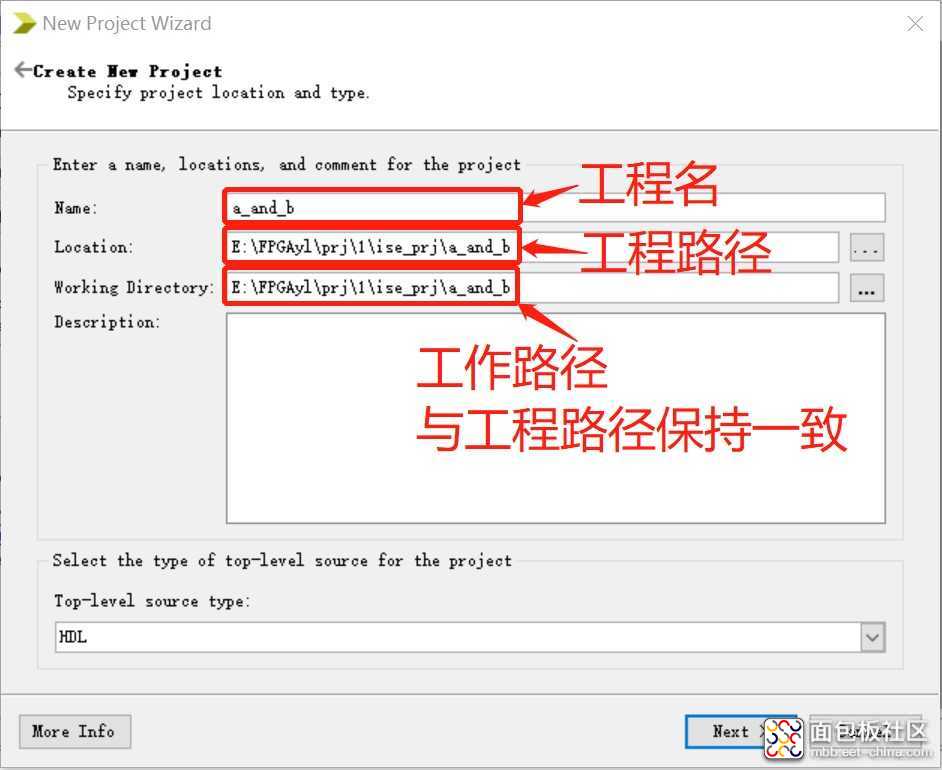

点击左上角的File àNew Project弹出如图3所示的界面,在此界面对应的栏目中填充工程名及工程路径,工作路径会与工程路径默认一致,切记工程路径不可存有中文字符。

图3 ISE工程建立

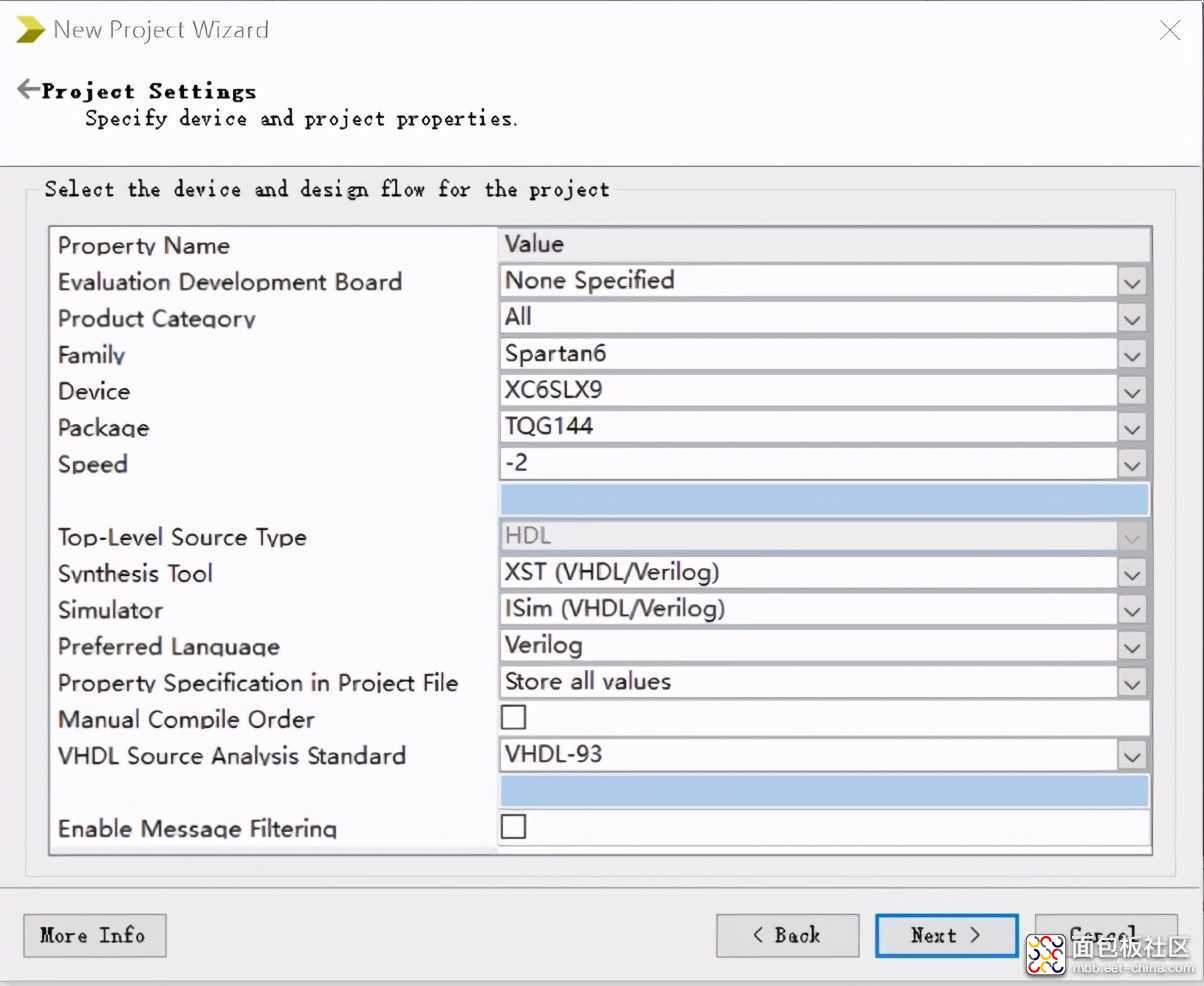

点击Next进入到图4所示的界面,在此我们根据实际的芯片填写相应的栏目,之后点击Next进入到概述界面,点击Finish结束工程的建立。

图4 ISE工程芯片选择

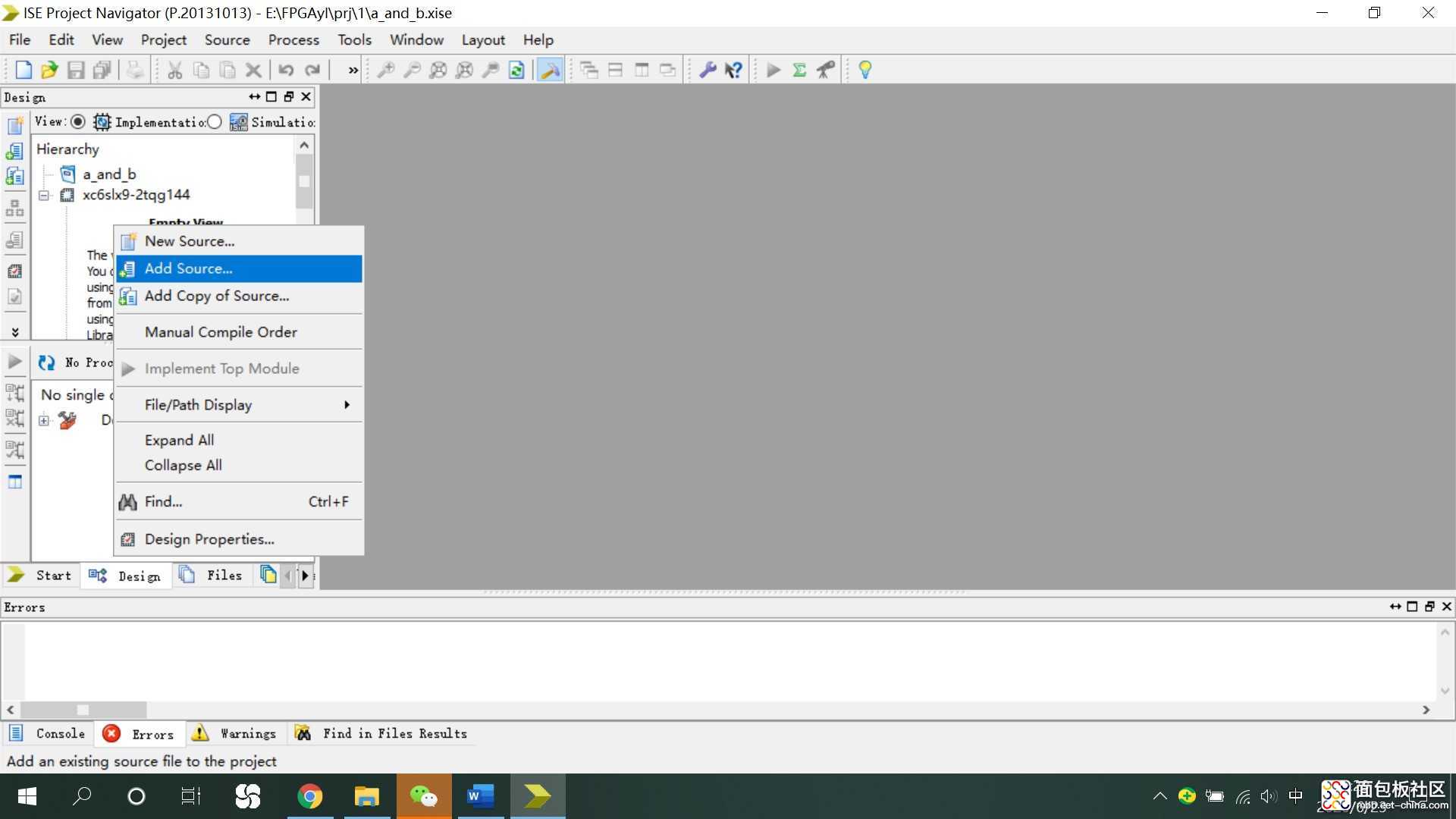

在工程端添加写好的v文件。在工程端右键空白处出现图5所示的菜单栏,点击Add Source...添加写好的v文件。

图5 添加v文件

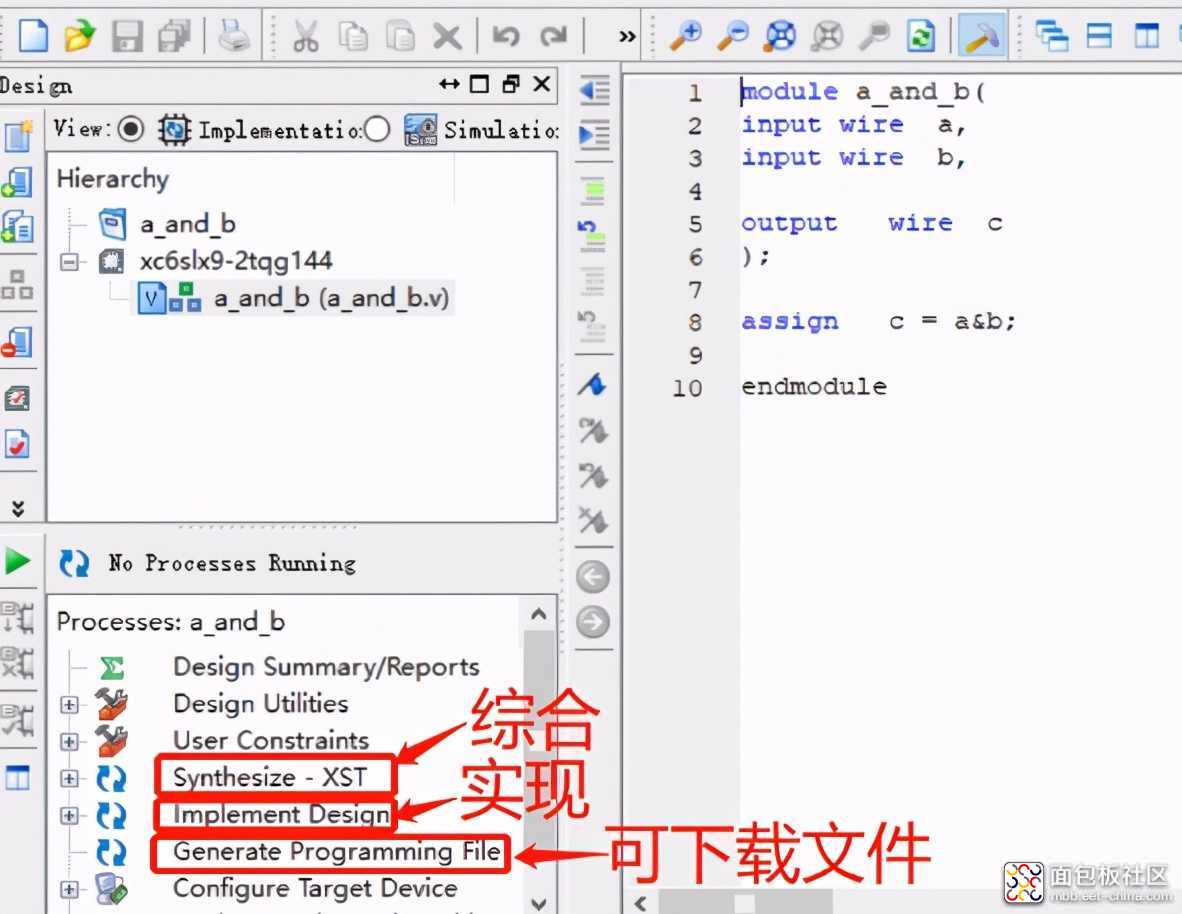

添加完v文件,执行过程栏中有三个可供执行的项,如图6所示,Synthesize(综合)可分析v文件是否存在语法问题及生成对应的电路,Implement Design(实现)可生成网表文件,Generate Programming File(生成可下载文件)可生成供FPGA下载的文件。

图6 ISE工程执行选项

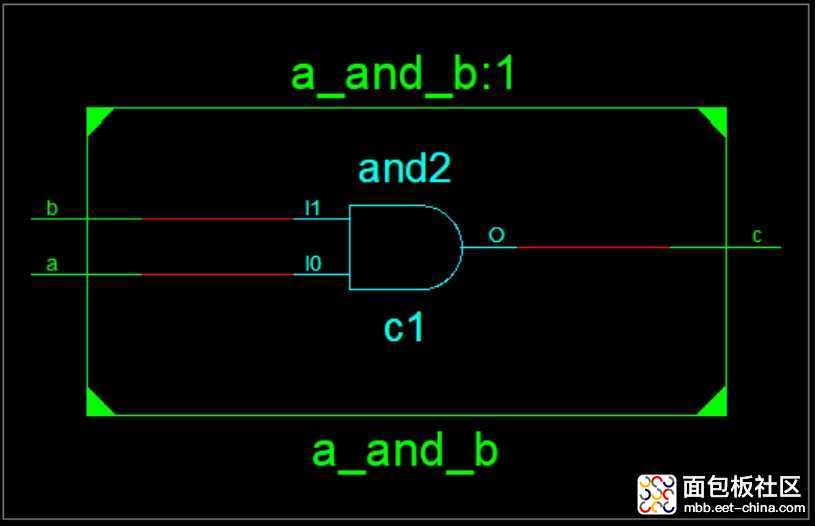

双击Synthesize,当前面出现绿色的对号表面执行结束,点击Synthesize前面的加号打开相应的隐藏菜单,双击View RTL Schematic可查看生成的电路图,如图6所示。

图7 RTL电路图

2.2 引脚绑定

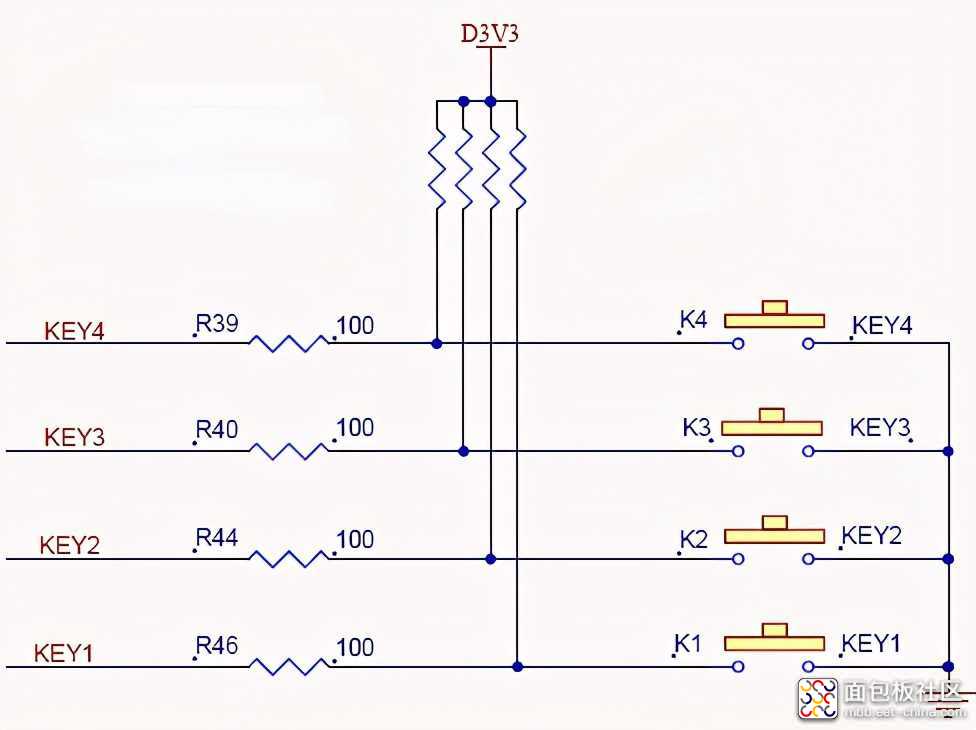

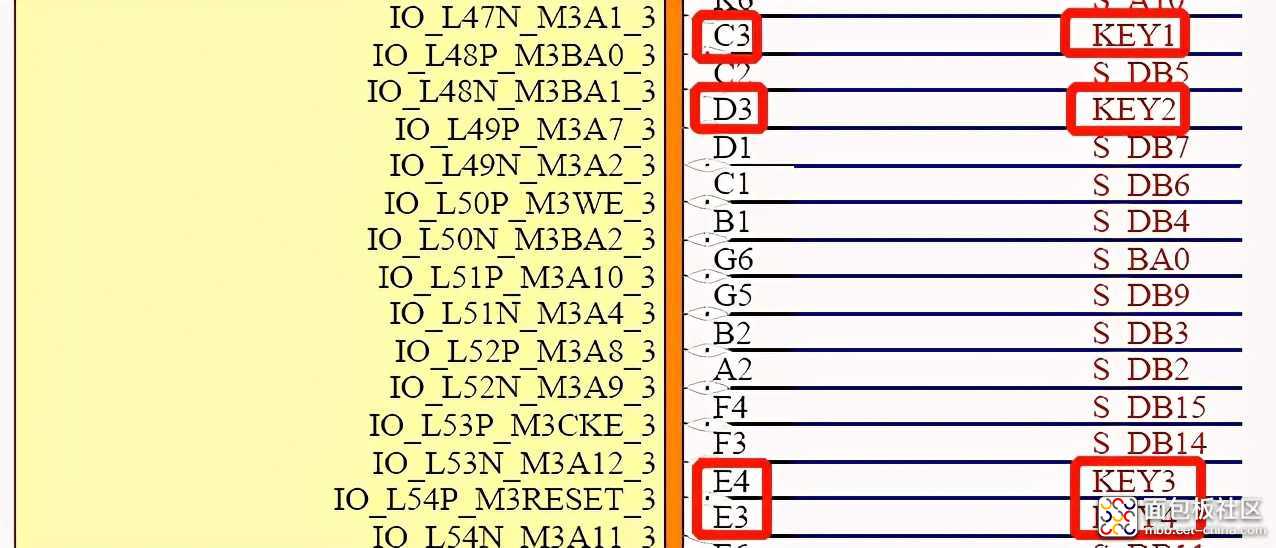

生成可下载文件之前,需要将设定的输入/输出端口与芯片的引脚相连接,具体连接芯片的哪一个引脚,需要查看开发板的手册。由图8(1)可以看出,示例板卡上面的按键在原理图上取名为KEY1、KEY2、KEY3和KEY4,接下来我们需要找到KEY1~KEY4与芯片上的哪个引脚相连。由图8(2)可以看出四个按键分别连接到芯片的C3、D3、E4和E3引脚,因此我们需要将代码里面的两个按键连接到芯片上此四个引脚中的两个,在此,我们选择KEY1和KEY2按键,即a绑定到C3,b绑定到D3。同理,查找原理图可以找到四个LED灯对应的芯片引脚为P4、N5、P5和M6,我们选择LED0对应的P4。

(1)按键原理图

(2)按键与芯片连接端口

图8 示例开发板部分原理图

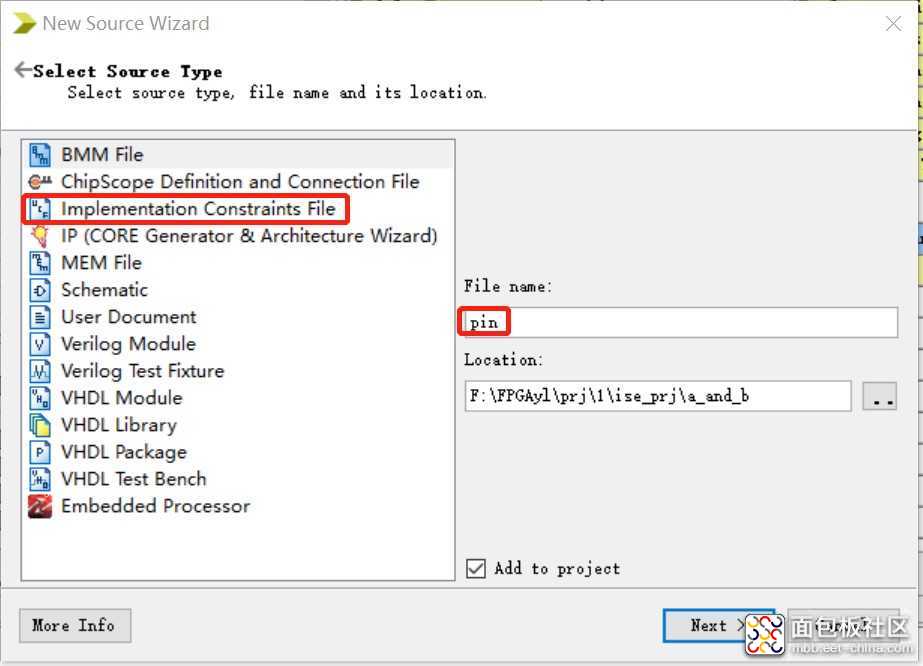

找到对应的引脚号后,右键工程中的工程名,弹出下拉菜单,选择New Source弹出如图9所示的菜单,在此选择Implementation Constraints File(约束文件),在File name中填写文件名,选择文件路径,点击Next,之后点击Finish完成约束文件的建立。

图9 约束文件建立

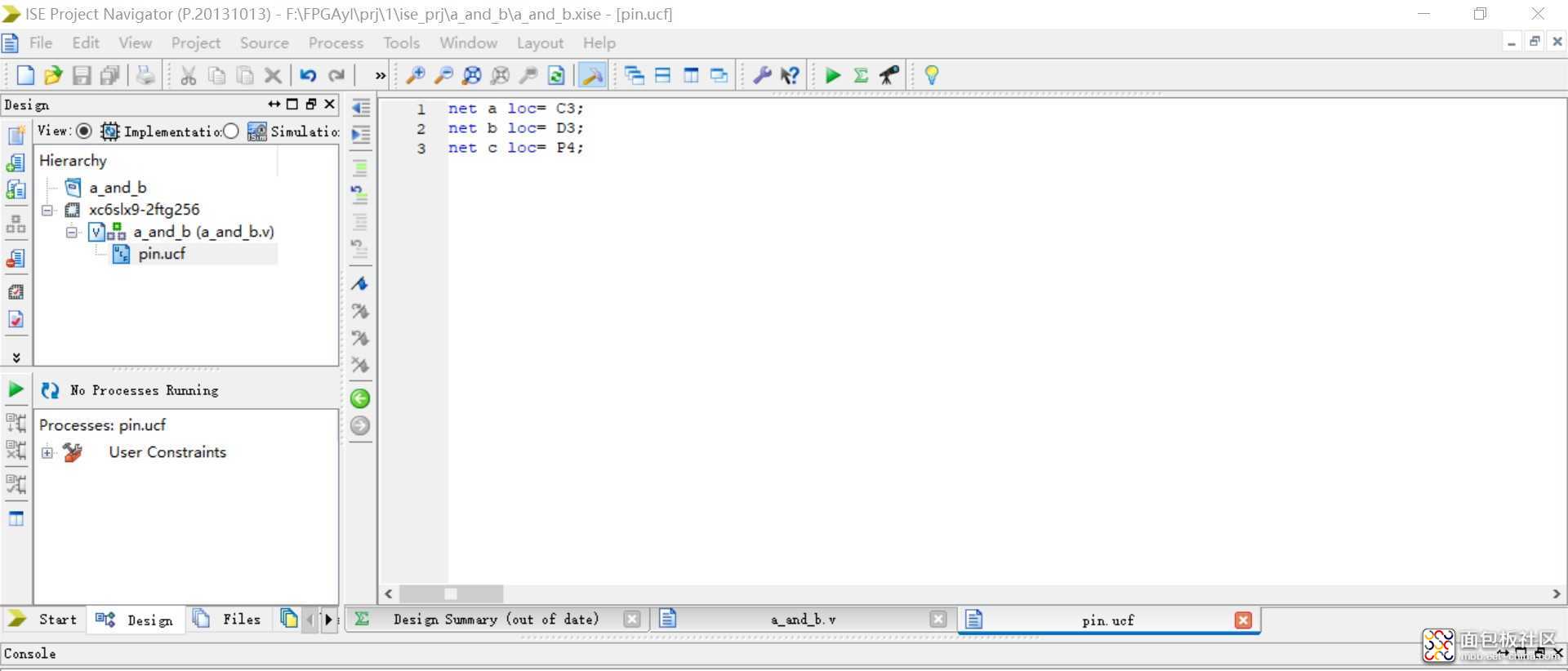

约束文件建立成功后,会生成一个ucf文件,此文件被包含在工程文件之下。按照格式添加文件,具体格式为:net 端口名 loc = 引脚名;,后面以分号隔开,本工程写好的引脚约束文件如图10所示,其中net和loc都为关键字。注意:ucf文件写好后一定记得保存。

图10 约束文件的书写

2.3 可下载文件生成及下载

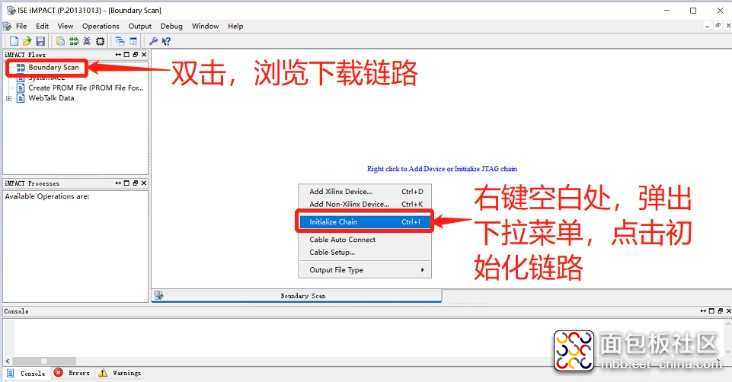

双击Generate Programming File生成可下载文件后,双击Configure Target File弹出如图11所示的下载界面,在下载界面中,双击Boundry Scan打开下载链路,在右侧界面空白处右键点击弹出下拉菜单,点击Initialize Chain选项,检查板卡是否连接正确。

图11 ISE下载界面

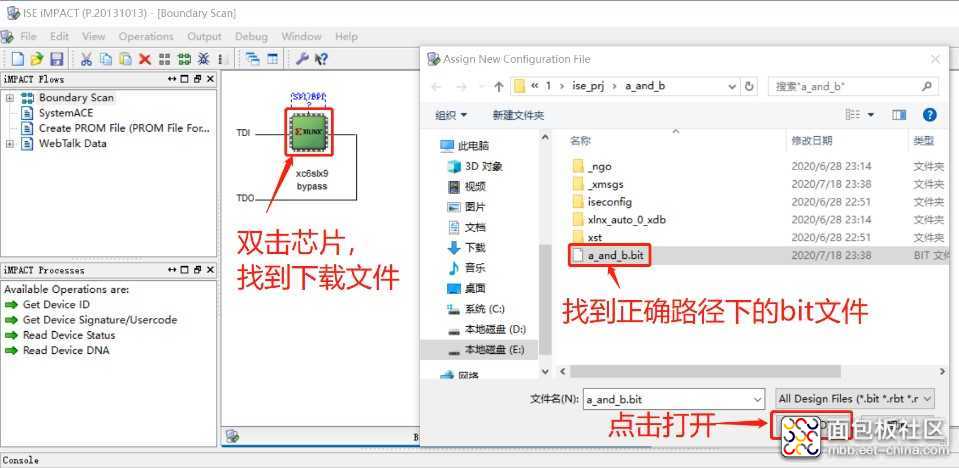

如图12所示,双击芯片样式的图片,弹出选择bit文件的页面,找到正确路径下的bit文件,之后点击打开,添加完毕后,右键芯片图样可弹出下来菜单,选择Program即可下载相应的程序。

图12 bit文件下载

下载完成后,按下绑定的按键,查看LED灯的亮灭是否符合要求,若是不符合,则需要查看问题出在哪里,比如引脚绑定是否正确等。

/5

/5