此教程使用的是http://www.oreganosystems.at/网站提供的开源8051内核。Altera自带的8051内核并不是免费的。

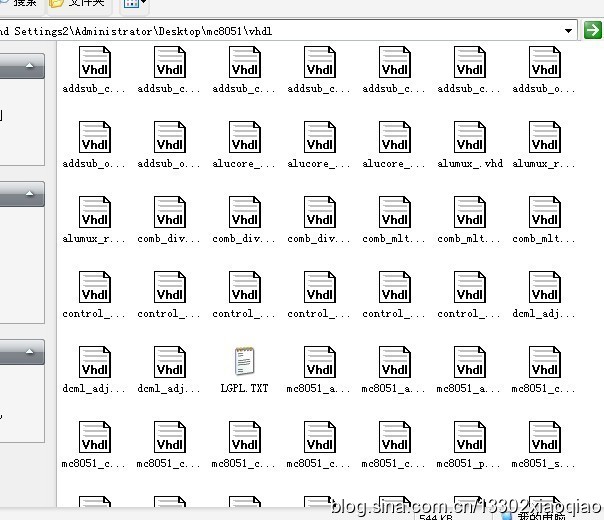

打开后的文件有上面这些文件夹。其中就一个最重要的就是8051核的源码,全部放在vhdl这个文件夹里面。那个pdf文档是这个IP核的使用教程,是官方标配的使用文档,也是纯英文的,对于英语四级没过的我下定决心花了大力气看最后只是一场空。。这问文档写的是用Synplify Pro这个综合软件综合的,虽然据说用这个软件进行综合可以节约FPGA的很多逻辑单元,但是对于我们这些初学者来讲,真的又麻烦又不适用,我们还是直接用QuartusII 来进行综合好了。

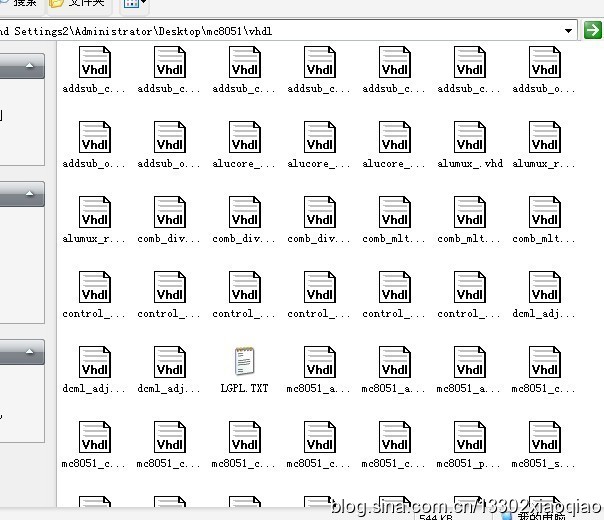

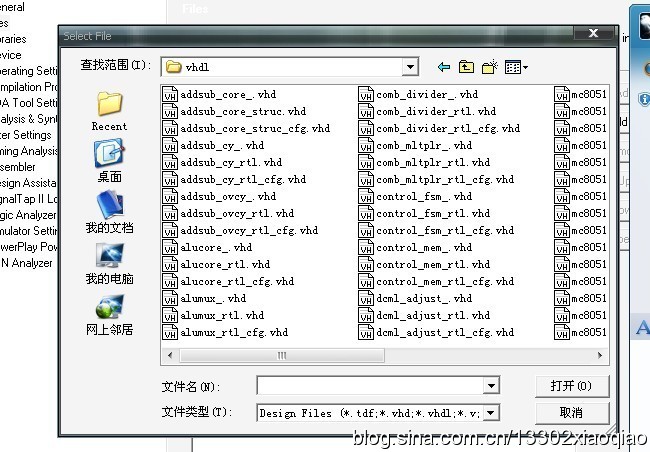

51IP核的源码全部在都在vhdl 这个文件夹中,打开是一大堆的源文件。

对于这么多的文件该怎么用,该如何使用,这是本文的重点。

首先用QuartusII建立一个工程,这这里先提醒下,文件目录最好不要包含中文,空格,不然会有些无法理解的错误。

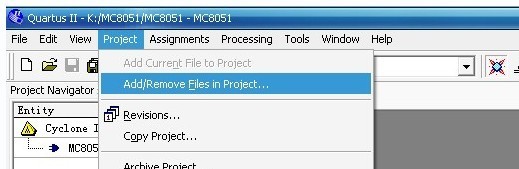

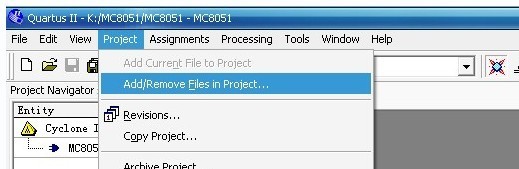

然后将 vhdl 整个文件夹复制到工程目录下(个人习惯,等下添加进工程里面的时候方便点)。下面是添加8051核文件的步骤。

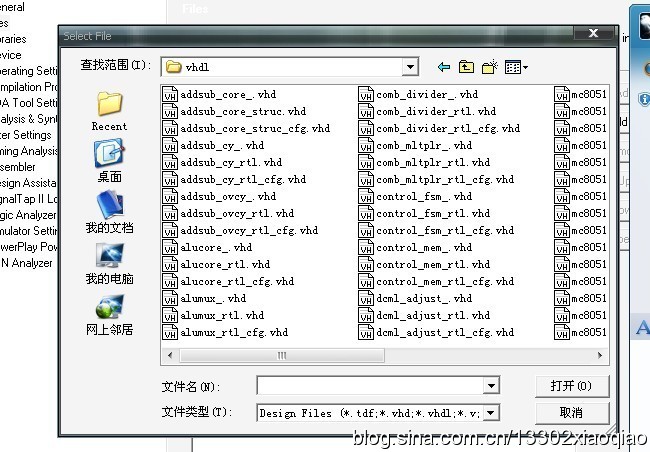

选择文件添加进工程。这里注意下

后面拖着_cfg 的这种文件不要添加进工程里面,还有就是含有_top_的文件也不要添加到里面。

然后双击打开mc8051_p.vhd 这个文件。把下面这些模块的例化语句全部删掉,这点非常重要!!

component mc8051_top

port (clk : in std_logic;

reset : in std_logic;

int0_i : in std_logic_vector(C_IMPL_N_EXT-1 downto 0);

int1_i : in std_logic_vector(C_IMPL_N_EXT-1 downto 0);

all_t0_i : in std_logic_vector(C_IMPL_N_TMR-1 downto 0);

all_t1_i : in std_logic_vector(C_IMPL_N_TMR-1 downto 0);

all_rxd_i : in std_logic_vector(C_IMPL_N_SIU-1 downto 0);

p0_i : in std_logic_vector(7 downto 0);

p1_i : in std_logic_vector(7 downto 0);

p2_i : in std_logic_vector(7 downto 0);

p3_i : in std_logic_vector(7 downto 0);

p0_o : out std_logic_vector(7 downto 0);

p1_o : out std_logic_vector(7 downto 0);

p2_o : out std_logic_vector(7 downto 0);

p3_o : out std_logic_vector(7 downto 0);

all_rxd_o : out std_logic_vector(C_IMPL_N_SIU-1 downto 0);

all_txd_o : out std_logic_vector(C_IMPL_N_SIU-1 downto 0);

all_rxdwr_o : out std_logic_vector(C_IMPL_N_SIU-1 downto 0));

end component;

-----------------------------------------------------------------------------

-- START: Component declarations for simulation models

-----------------------------------------------------------------------------

component mc8051_ram

port (clk : in std_logic;

reset : in std_logic;

ram_data_i : in std_logic_vector(7 downto 0);

ram_data_o : out std_logic_vector(7 downto 0);

ram_adr_i : in std_logic_vector(6 downto 0);

ram_wr_i : in std_logic;

ram_en_i : in std_logic);

end component;

component mc8051_ramx

port (clk : in std_logic;

reset : in std_logic;

ram_data_i : in std_logic_vector(7 downto 0);

ram_data_o : out std_logic_vector(7 downto 0);

ram_adr_i : in std_logic_vector(15 downto 0);

ram_wr_i : in std_logic);

end component;

component mc8051_rom

port (clk : in std_logic;

reset : in std_logic;

rom_data_o : out std_logic_vector(7 downto 0);

rom_adr_i : in std_logic_vector(15 downto 0));

end component;

-----------------------------------------------------------------------------

-- END: Component declarations for simulation models

-----------------------------------------------------------------------------

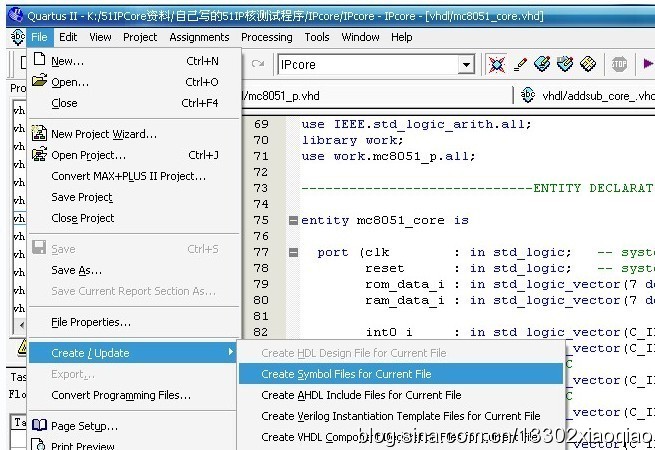

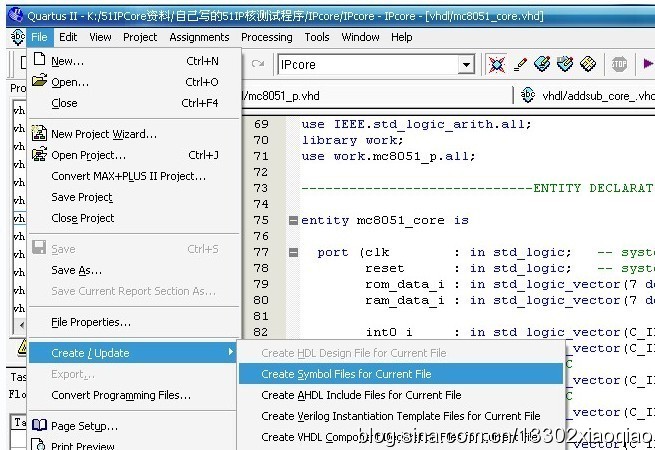

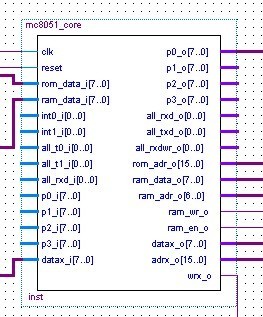

然后双击打开mc8051_core.vhd 这个文件。

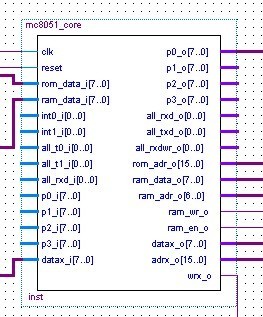

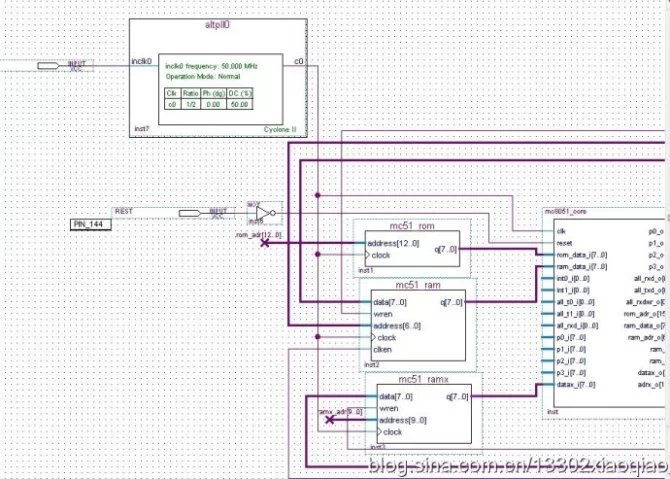

这样就可以生成mc8051核的原理图模块了。

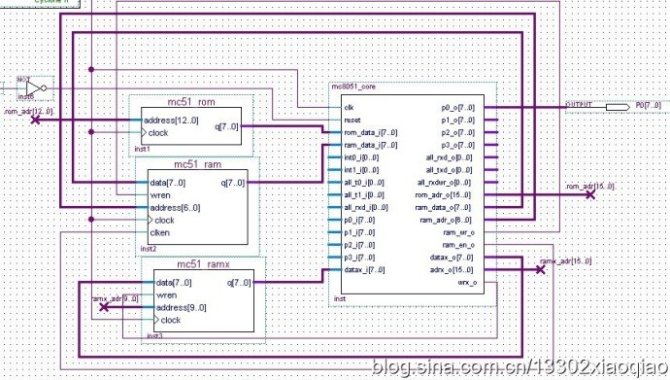

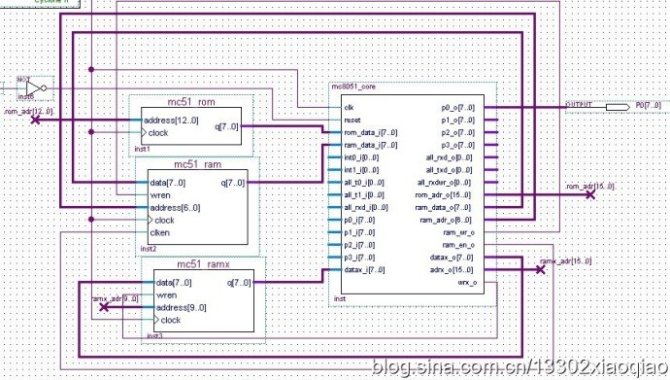

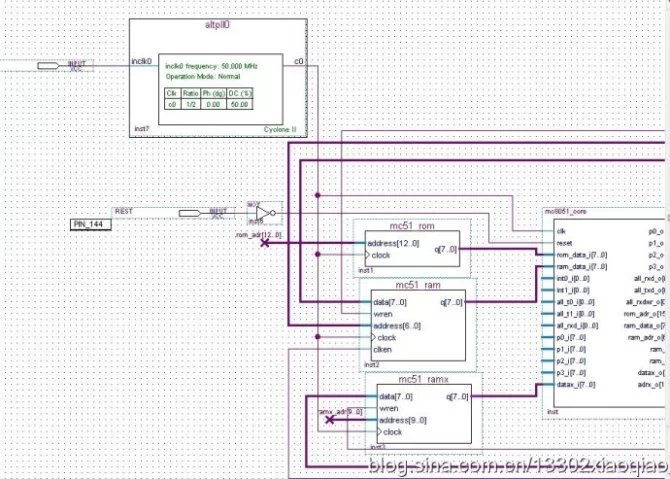

当然光有这个核,它还不是完整的51核,还需要给它添加ram和rom

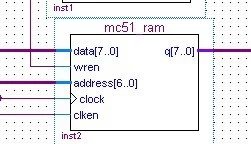

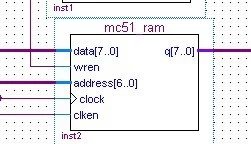

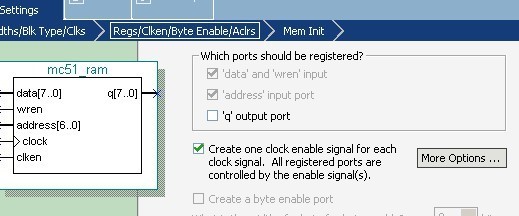

Ram是必须的,ramx是扩展的,rom也是必须的,是用来放所需运行的51单片机程序的,大小可以根据需要定制。但是推荐ram的大小用固定的以下配置。

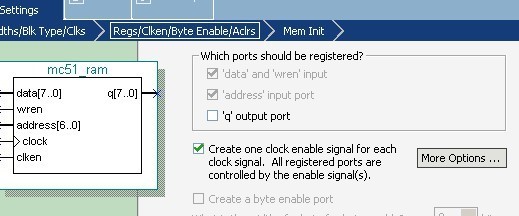

三个存储单元都有一点需要注意,就是不能寄存输出。

就是在ram和rom配置的时候都要把 ‘q‘output port 前面的勾去掉!这点也很重要。

rom配置的时候需要加入.hex文件,就是keilc51 编译好的平时下载到单片机实验板上的那个程序文件,初始的时候可以随便添加一个就可以了,待程序写好后,就重新把它添加要rom里面,注意,如果改变了rom的程序文件,那么要重新完整编译一次下载到板子上才是更新后的程序噢。

然后就按照固定的格式将他们连接起来就可以了。可以发现,有些线是断开的通过标号来连接的,跟protel里的网络标号差不多。一般的数据宽度不匹配的时候就用这种方式来连接,如果直接连接,编译会报错的。

这里面我添加了锁相环,这个最好加上,因为我在测试的时候发现同样的时钟频率下,加了锁相环才能工作,不加就不工作。

Ok 编译下载就成功了。不过从编译报告来看,这个东西的确占逻辑单元比较多,我的板子是EP2C8Q208C8的芯片,用了一半的逻辑单元去。。。电脑CPU差,编译时间又挺漫长的。。

嗯,总结一下嵌入51核要注意的点

1、添加文件进工程时,有些是必要的,有些是不能加的。

2、有个文件要进行一下修改

3、配置ram和rom的时候,不要寄存器输出。

转载:http ://blog.sina.com.cn/s/blog_52e8baa40100t52i.html

/2

/2

Datasheet

8051 IP Core: Brief Datasheet

ADPCM IP Core: Datasheet

8051 IP Core

Source Files and User Guide

8051 IP Core: Source Files

8051 IP Core: User Guide

8051 IP Core on an Altera Cyclone Nios Board

Source Files and User Guide

8051 IP Core: Source Files – Cyclone Nios Board Implementation

8051 IP Core: User Guide – Cyclone Nios Board Implementation

8051 IP Core Boot Loader Demo Design

Source Code and User Guide

8051 IP Core: Source Files – Boot Loader Demo Design

8051 IP Core: User Guide – Boot Loader Demo Design