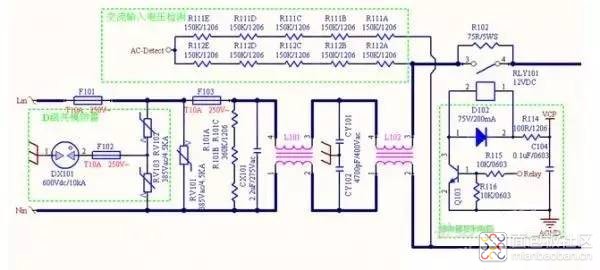

分享点一:熟透电路方可从容进行PCB设计之EMI电路

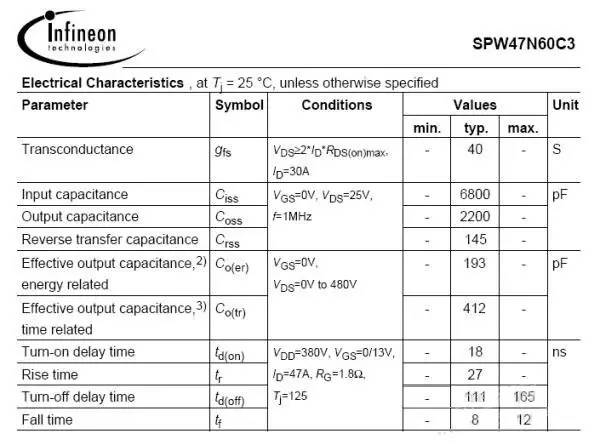

上面的电路对EMC的影响可想而知,输入端的滤波器都在这里;防雷击的压敏;防止冲击电流的电阻R102(配合继电器减小损耗);关键的虑差模X电容以及和电感配合滤波的Y电容;还有对安规布板影响的保险丝;这里的每一个器件都至关重要,要细细品味每一个器件的功能与作用。设计电路时就要考虑的EMC严酷等级从容设计,比如设置几级滤波,Y电容数量的个数以及位置。压敏大小数量选择,都与我们对EMC的需求密切相关,欢迎大家一起讨论看似简单其实每个元器件蕴含深刻道理的EMI电路。

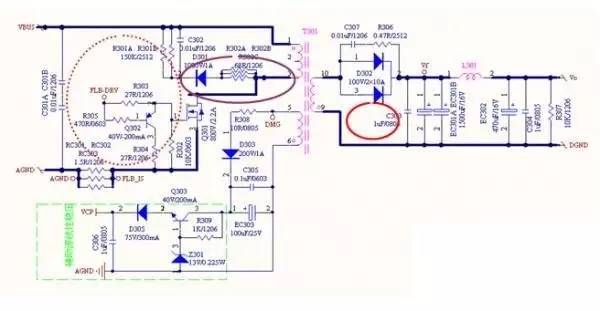

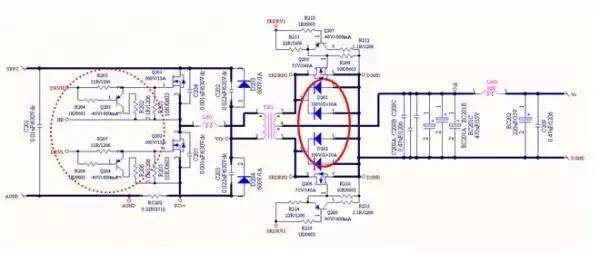

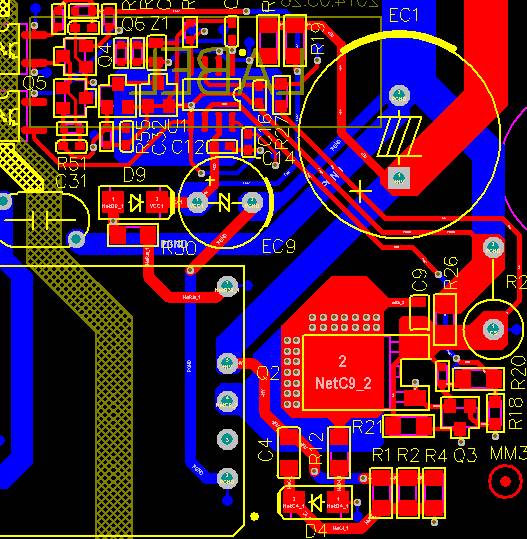

分享点二:电路与EMC(最熟悉的反激主拓扑,看看电路中哪些关键地方蕴含了EMC的机理)

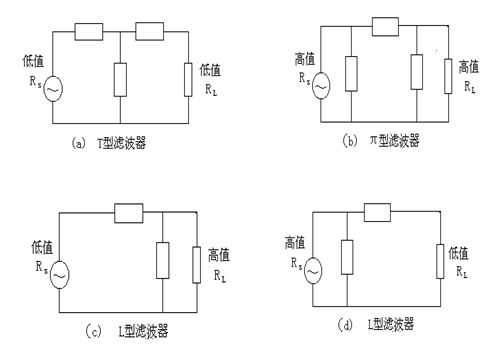

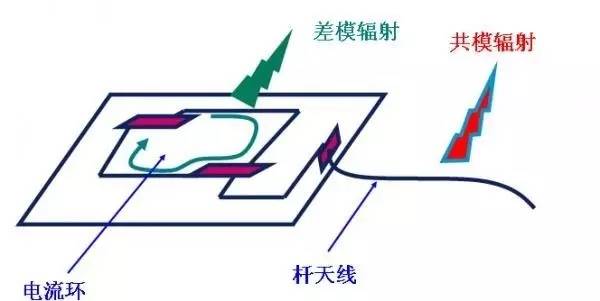

上图的电路中打圈几部分:对EMC影响非常重要(注意绿色部分不是的),比如辐射大家都知道电磁场辐射是空间的,但基本的原理是磁通量的变化,磁通量涉及到磁场有效截面积,也就是电路中对应的环路。电流可以产生磁场,产生的是稳定的磁场,不能向电场转化;但变化的电流产生变化的磁场,变化的磁场是可以产生电场(其实这就是有名的麦克斯韦方程我用通俗语言来说),变化的电场同理可产生磁场。所以一定要关注那些有开关状态的地方,那就是EMC源头之一,这里就是EMC源头之一(这里说之一当然后续还会讲到其它方面); 比如电路中虚线环路,是开关管开通和关断的环路,不仅设计电路时开关速度可以调节对EMC影响,布板走线环路面积也有着重要的影响!另二个环路是吸收环路和整流环路,先提前了解下,后面再讲!

分享点三:PCB设计与EMC的关联

1.PCB环路对EMC的影响非常重要,比如反激主功率环路,如果太大的话辐射会很差。

2.滤波器走线效果,滤波器是用来滤去干扰的,但若是PCB走线不好的话,滤波器就可能失去应该有的效果。

3.结构部分,散热器设计接地不好会影响,屏蔽版的接地等;

4.敏感部分与干扰源头过近,比如EMI电路与开关管很近,必然会导致EMC很差,需要有清晰的隔离区域。

5.RC吸收回路的走线。

6.Y电容接地与走线,还有Y电容的位置也很关键等等!

等等。先想到这说这些,后续会具体讨论,先起个引子。

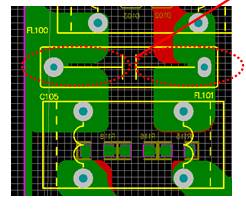

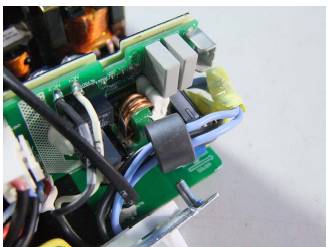

下面举一个小例子:

如上图中虚线框,X电容引脚走线做了内缩的处理,大家可以学习下,如何让电容引脚走线外挂(采用挤电流走线)。这样X电容的滤波效果才能够达到最佳状态。

分享点四:PCB设计之准备事项:(准备充分了,方可设计步步稳健,避免设计推翻重来)

分享点五:PCB设计之安规考虑其它因素

1.明白自己产品做什么认证,属于什么产品种类,比如医疗,通信,电力,TV等各不相同,但也有很多相通的地方。

2.安规中与PCB布板紧密的地方,了解绝缘的特点,哪些地方是基本绝缘,哪些地方是加强绝缘,不同标准绝缘距离是不一样的。最好是会查标准,并且会计算电气距离,爬电距离。

3.产品的安规器件重点注意,比如变压器磁性与原副边关系;

4.散热器与周边距离问题,散热器接的地不一样绝缘情况也不一样,接大地还是冷地,热地绝缘也布一样。

5.保险的距离特别注意,要求最严格地方。保险丝前后距离布一致。

6.Y电容与漏电流,接触电流关系。

等等,后续会详细说明距离该怎么留,如何做好安规要求。

分享点六:PCB设计之电源布局

1.首先衡量PCB尺寸与器件数量,做到疏密有致,要不然一块密,一块稀疏很难看。

2.将电路模块化,以核心器件为中心,关键器件优先放的原则一次放置器件。

3.器件呈垂直或水平防置,一是美观,二是方便插件作业,特殊情况可以考虑倾斜。

4.布局时需要考虑到走线,摆放到最合理位置方便后续走线。

5.布局时尽可能减小环路面积,四大环路后面会详解到。

做到上述几点,当然要灵活运用,比较合理的布局很快就会诞生。

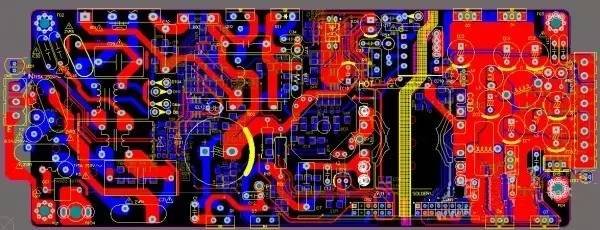

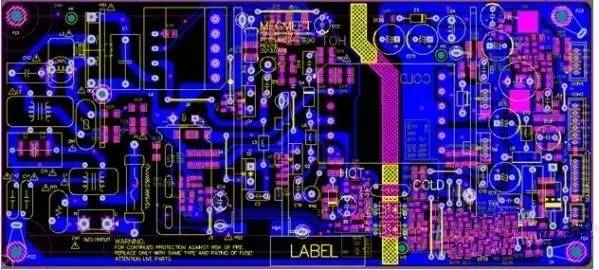

下面是我画的第一块处女PCB板,好多年前的事情,当时非常的艰苦完成的,中间可能有小问题,不过大体布局还是值得学习的:

此图功率密度还是比较高,其中LLC的控制部分,辅助源部分以及BUCK电路驱动(大功率多路输出)部分在小板上,就没拿出来,看看主功率方面的布局特点吧:

1.输入输出端子是固定死的,不能动,板子是长方形的,主功率流向如何去选择?

这里采用由下至上,由左及右的方式来布局,散热是依靠外壳。

2.EMI电路还是清晰的流向,这点很重要,要不混乱了不美观也对EMC不好。

3.大电容的位置尽量考虑到了PFC环路以及LLC主功率环路;

4.副边的电流比较大,为了走电流,以及整流管散热,采用了这样的布局,整流管在上,BUCK电路MOS管在下,散热分散效果好;大功率的顶层一般走负,底层走正。

每个板子有自己的特点,当然也有自己的难处,如何合理解决是关键,大家从中能理解布局合理选取的含义吗?

分享点七:PCB实例赏析

可以根据之前谈论的PCB布局要点,检视此板,是否做的很到位,我认为是做到比较好的地方了,当然瑕疵总会有,也可以提出来,单面板如此紧凑能做到这样已实属不易了,可以借此板学习讨论!后面还会针对此板讲解学习,大家先欣赏下。

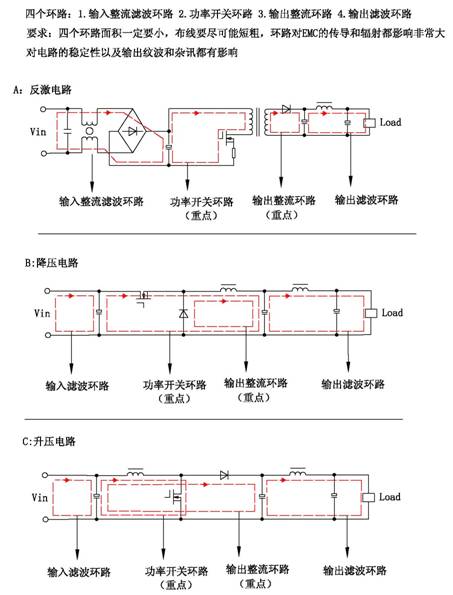

分享点八:PCB设计之四大环路认识:(PCB布局的基本要求就是四大环路面积小)

补充一下,吸收环路(RCD吸收以及MOS管的RC吸收,整流管的RC吸收)也很重要,也是产生高频辐射的环路,对上图有任何疑问,都欢迎讨论,不怕任何质疑,只要是针对问题的质疑,一起讨论学习才能更大的进步!

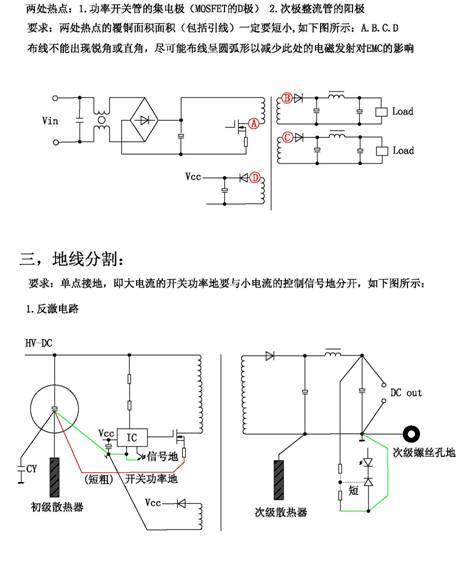

分享点九:PCB设计之热点(浮动电位点)及地线:

注意事项:

1.针对热点,一定要特别注意(高频开关点),是高频辐射点,布局走线对EMC影响很大。

2.热点构成的环路小,走线短,并且走线不是越粗越好,而是够走电流够用就好。

3.地线要单点接地。主功率地和信号地分开,采样地单独走。

4.散热器的地需要接主功率地。

分享点十:EMC整改心得体会

均为个人理解,或许与传统资料教材有差异,请自己斟酌,反正我觉得很多通用的教材结果没我自己总结的使用,自夸了。想说的很多,可能有些乱,都是实践出来的!

一.EMC产生以及测试时测得的结果如何去理解:简单来说就是如何对症下药,很多情况拿到第一轮测试结果,怎么将结果和电源去对照分析;主题思路如下:

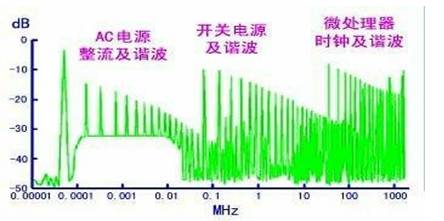

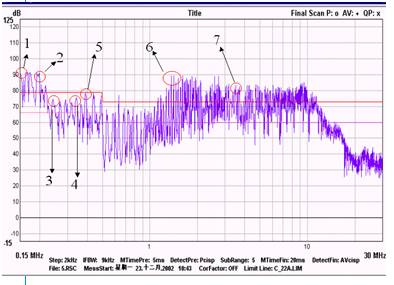

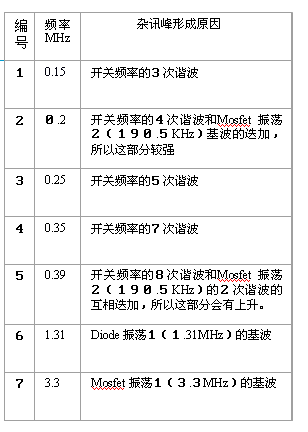

1.针对传导,测试范围标准15K-30M,常见的EN55022是150K起。传导的源头是怎么产生的呢?针对低频,主要是开关频率以及其倍频(后续有图解),这种从源头是无法解决的,开关频率是无法消除的,当然你可以改变开关频率,那也只是将测试结果移动了,并没有真正意义上消除。只能通过滤波器来解决,一般来说对于低频采用R10K这种高磁通材质有很好的效果,磁环大小跟你功率有关系,一般达到10MH感量,甚至更大到20MH,配合Y电容一般能很好解决,低频不是难点;真正的难点是高频,个人认为,高频的起因就复杂多了,有开关导致,有变压器可能,也有电感的可能,也就就是一切存在开关状态的地方都可能存在(怎么判断具体位置,后续讲解),这里需要一番摸索;找到源头未必源头能解决,可能有改善,还是的配合滤波器。针对高频,采用低磁通材质,如镍锌环,感量一般都是UH级别的,配合合适Y电容(比较复杂的电源,建议布板时多留几个Y电容位置,方便整改);

2.一些配合手段,很多教材都提到增大X电容判断差模还是共模,有一定意义可能现实帮助不大,设计时一般我们X电容都会放到合适的值。并且增大X电容就能解决差模问题,也是瞎扯,所以很多教材都是提供一定意义指导,个人觉得没什么用。我觉得比较好的手段有几个:1.对照接地和不解地总结差异,不接地可能更差,原因是系统构造的传导途径少了;也可能有改善,说明是通过地回路传导到端口。具体解决措施,针对电路接地的点Y电容进行调节以及加磁珠。2.在输入端口套磁环,若套低U环有改善,调节第一级滤波电感。3复杂的系统注意EMI电路的屏蔽措施。若措施都没什么效果,反省PCB设计,这方面在PCB设计中会讲到。

3.针对辐射:必须找出源头去解决,观测第一次测试结果,若是30M附近超出,跟接地相关,系统上找接地,并且要判断测试时是否接地良好,有时候输入线都有影响。2.40M-100M以内,一般是MOS管开通关断引起,有时后为了现场不好直接判断是开通还是关断,可针对性整改观测结果去验证(当然这都得花钱,后续会讲解如何用示波器去判断,这可是密招)。3 100M以上多为二极管引起,整改二极管吸收电容,大功率的有的可能是同步整流,更改MOS管吸收环路,记住有时候调整C时还得配合R整改。

要说的太多,后续针对具体实例去补充吧,先手打这么多,反正我打的够辛苦,能引起共鸣很难,毕竟每个人的整改经历差很多,就当给新人朋友一些启示吧,后续会举例说明!

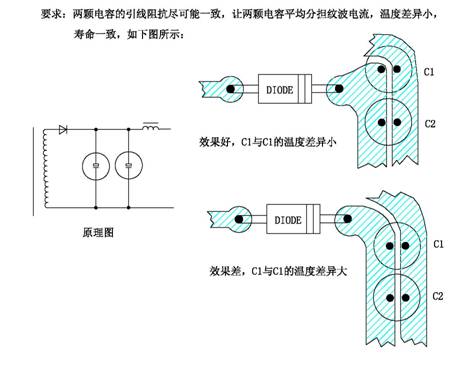

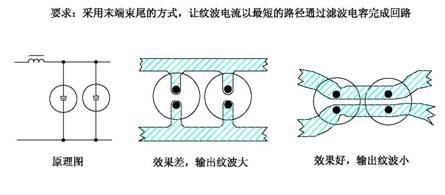

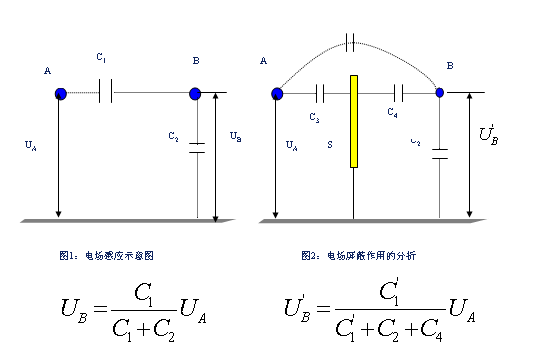

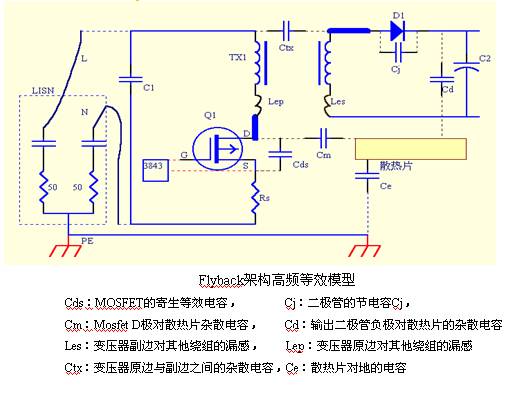

分享点十一:布板走线之滤波电容走线

滤波电容的走线对滤波效果有至关重要的作用,走的不好,可能失去其应有的滤波效果。

图一是副边整流滤波走法,使二个电容效果分摊,避免第二个电容在整流回路中失效。

图二:为输出滤波电容走线,一定不要外挂(也就是被旁路掉),走的不好输出纹波很差。

分享点十二:LLC电路的布板与EMC

LLC电路大家最熟悉不过了,虚线圆圈是驱动电路,在电路设计时紧靠MOS管放置,也就是说IC提供的驱动只需要引二根线拉到驱动电路,驱动电路离MOS管近,避免被干扰(同时走线时也要注意驱动干扰到敏感信号,既是敏感信号也是干扰源);一旦驱动被干扰电源可想而知。

同理同步整流的MOS管驱动也要离同步整流管近,设计原理图时像此图这样放就能很好理解,假如你将这电路给PCB工程师布板,他就很直观如何布局走线,你若是画得很乱,很多PCB工程师对电路理解得布透彻可能就容易布错板。

另外:原边有一个重要的环路,PFC电容与MOS管以及变压器,谐振电感,谐振电容构成的环路面积小;

副边整流滤波环路同样重要,电容的走线之前讲过,也很重要;

走线时注意高低压的距离,有些地方电压是浮动的,必须当作高压来对待,比如上管驱动以及对应的参考电压。

至于EMC方面LLC的开通是软开关,开通对EMC几乎没有影响,重点关注是关断速度的快慢对EMC影响;还有MOS管结电容并的电容对EMC影响很大,选择电容不合适,或是不加(MOS管自身也有结电容)对EMC都可能有影响,这是重点注意的地方;此图没有Y电容,在MOS管正或者负防置Y电容也能很好滤去开关干扰;

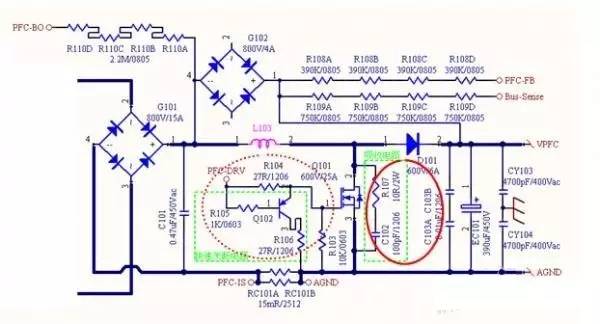

分享点十三:电路设计与布板之PFC

左边绿色方框部分是驱动电路,和之前LLC拓扑驱动一样,离MOS就近放置,原理图上就体现出来。

右边绿色虚线方框部分,是MOS管关断尖峰吸收电路,一样与MOS管构成环路要最小;

另外二大重要环路,一是MOS管开通环路(虚线红色图),另一个是MOS管关断环路(实线红色图);环路面积尽可能小;

有的产品EMC很难在源头上去处理的,可以采用磁环滤波,当然我这里说的磁环有二个层面的意思,一方面是输入输出端的滤波电感,采用不同材质磁环,不同匝数会有对应的效果,还有一方面意思是直接在输入输出线上套磁环,有时能起到妙用,但不是在所有场合都能用,起码还是能作为判断依据;

1.CS信号(采样信号):从采样电阻R25,R26拉出,注意IC的地线以采样电阻为基准,采样电阻的正负差分走线拉倒IC CS脚以及IC 的GND脚。

2.驱动信号从驱动电路拉倒IC驱动引脚,注意不要干扰到CS脚;如图走线三根线并排走,并且将地线走在驱动先和CS线中间起到一定屏蔽作用;

3.双面板最好将IC一层铺地屏蔽,铺地的网络一定要从IC GND引出,非关键信号GND可直接打过孔,关键信号地需要单点接地,直接接IC;

4.FB反馈网络信号注意查分走线并且单点接IC;

5.RCD吸收网络不要放在主回路;

6.VCC的整流滤波地需要接主功率地,二级滤波可接IC 地;

7.Y电容走线单独接,不可与主功率混淆,避免干扰;

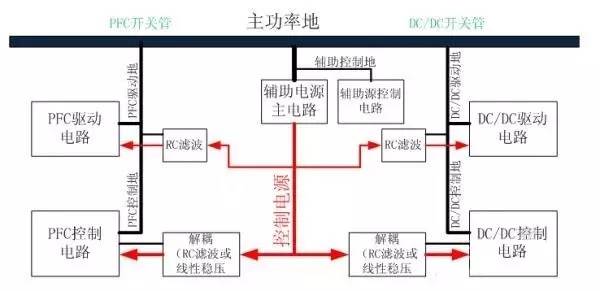

1.PFC的驱动和IC共地接PFC管,更具体点是接采样电阻的地;

2.DC-DC部分的驱动地和控制地接DC开关管部分的采样地;

3.辅助源部分控制地接辅助源MOS管采样第,MOS管地再接主功率地;

4.各自IC的供电地通过辅助源EC滤波接IC地,注意RC滤波靠近IC;

总结:注意好各自的单点接地,地线不乱,是走线最重要的地方之一!!!

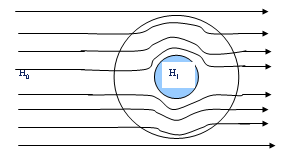

磁场屏蔽原理,磁场通过屏蔽罩会改变磁路,导致磁力线向周围扩散,中间磁场干扰达到屏蔽目的;

对器件的认识对EMC也有着重要的意义,比如MOS管,主开关MOS是很重要的EMC源头之一,还有整流管的开通以及关断也会产生高频辐射(原理是电流产生磁场,变化的电流产生电场);当然这里主要是介绍半导体开关器件,其他的电感变压器就不做说明了;

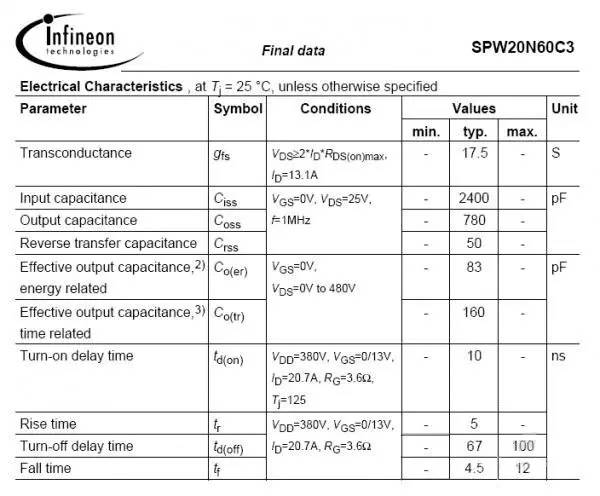

开关器件哪些参数对EMC有重要影响,我们常说快管,慢管是以什么作为参照的呢?我们都知道快管开通损耗小,为了做高效率都喜欢用,但是为了EMC顺利通过,不得不舍弃效率,降低开关速度来减弱开关辐射;

对于MOS管,开通速度是由驱动电阻与输入结电容决定的;关断速度是由输出结电容与管子内阻决定;

对于二极管,有肖特基二极管,快回复二极管,普通二极管,还有一种用的比较少的SIC二极管,开关速度SIC二极管几乎为零,等于是没有反向恢复,开关辐射最小,并且损耗也最小,唯一的缺点就是价格昂贵,故很少用;其次就是肖特基二极管,正向压降低,反向恢复时间短,依次是快回复和普通二极管;需要在损耗和EMC之间折中;一般可采取改吸收以及套磁珠等措施整改EMC;

EMC的路径,当然空间辐射是跟环路有关,环路也是路径构造成的;分析出反激高频等效模型,帮助理解EMC形成的机理;我们的测试接收设备会从L,N端接收传导,为了减小接收的干扰,就必须让干扰通过地回路流通而不从L,N端口流向接收设备;这时候我们的EMI电感以及Y电容通过阻抗匹配就可以实现;另外原边的干扰可以通过原副边Y电容,变压器杂散电容以及大地耦合到副边,形成更多的回路;当然一些结电容参数,如MOS管结电容,散热器结电容也能构成流通路径;

这些原理基础知识理解得好,对实际处理EMC工作以及布板很有用那个,如果没这种意识,可能毫无用处,因为提供不了直接方法,需要与其他知识想结合;

而且这里提的很多原理东西,在很多EMC资料中是看不到的,而且也没这么集中,需要反复体会!

这里是给大家补充一些似乎很神秘的EMC它是怎么来的,感觉不再神秘,而不只是稀里糊涂的采用滤波器解决了问题!

/4

/4