特征

引脚与双极8289兼容

性能兼容:

提供多主站系统总线控制和仲裁

提供82C88 / 8288总线的简单接口调节器

使用80C86 / 8086,80C88 / 8088处理器同步多主总线

双极驱动能力

灵活系统配置的四种操作模式

低功率运行

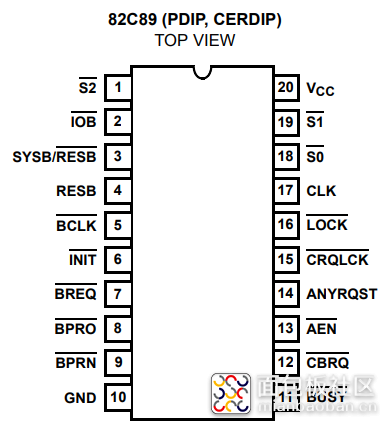

引脚图

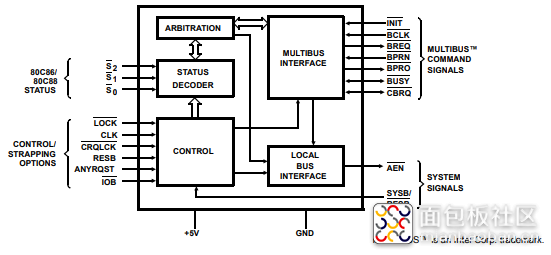

功能图

引脚说明

符号数字类型说明

VCC 20 VCC:+ 5V电源引脚。建议在引脚10和20之间使用0.1?F电容进行去耦。GND 10接地。

S0,S1,S2 1,18-19 I状态输入引脚:来自80C86,80C88或8089处理器的状态输入引脚。82C89解码这些引脚启动总线请求和放弃操作。

CLK 17 I时钟:来自82C84A或82C85时钟芯片,用于确定何时启动总线仲裁器操作。

LOCK 16 I LOCK:处理器生成的信号,当被激活(低电平)时,无论其优先级如何,都会阻止仲裁器将多主机系统总线交给任何其他总线仲裁器。

CRQLCK 15 I COMMON REQUEST LOCK:低电平有效信号,阻止仲裁器放弃多主机

系统总线到任何其他总线仲裁器通过CBRQ输入引脚请求总线。

RESB 4 I RESIDENT BUS:一种捆绑选项,用于将仲裁器配置为在具有多主站的系统中运行

系统总线和驻地总线。高速,多主系统总线被要求或投降为a

SYSB / RESB输入引脚的功能。保持低电平,SYSB / RESB输入被忽略。

ANYRQST 14 I ANY REQUEST:一个捆绑选项,允许多主系统总线降低到更低

优先级仲裁器就好像它是一个更高优先级的仲裁器(即,当一个较低优先级的仲裁器请求使用该优先级

多主系统总线,总线一旦可能就被交出)。当ANYRQST被束缚低时,

根据设计信息中的表A,总线被交出。如果ANYRQST被束缚在高位且CBRQ是

激活后,总线在当前总线周期结束时交出。捆绑CBRQ低和ANYRQST高

在每个传输周期后强制82C89仲裁器放弃多主系统总线。请注意,当

投降发生BREQ被驱动为假(高)。

IOB 2 I IO BUS:捆绑选项,用于将82C89 Arbiter配置为在具有IO总线的系统中运行

(外围总线)和多主系统总线。仲裁者请求并放弃使用多主机

系统总线作为状态线的函数,S2。允许多主系统总线放弃

处理器正在执行IO命令,并且只要处理器执行存储器就被请求

命令。假设中断周期来自外设总线,并被视为IO命令。

AEN 13 O ADDRESS ENABLE:82C89 Arbiter输出到处理器的地址锁存到82C88总线

控制器和82C84A或82C85时钟发生器。 AEN用于指示总线控制器和地址锁存器

什么时候三个状态他们的输出驱动程序。

INIT 6 I INITIALIZE:一个有效的低多主系统总线输入信号,用于复位多主站系统总线上的所有总线仲裁器。初始化后,没有仲裁器可以使用多主系统总线。

82C89总线仲裁器与82C88配合使用总线控制器将80C86,80C88处理器连接到多主站系统总线(80C86和80C88均配置)在他们的最大模式)。处理器不知道仲裁器存在并发出命令,好像它具有排他性使用系统总线。如果处理器没有使用多主系统总线,仲裁器阻止总线控制器(82C88),数据收发器和地址锁存器访问系统总线(例如所有总线驱动器)输出被强制进入高阻态。自从命令序列不是由82C88系统发出的总线将显示为“未就绪”,处理器将进入等待状态。处理器将保持等待直到总线仲裁者获得了多主系统总线的使用于是仲裁器将允许总线控制器,数据收发器和地址锁存器以访问系统。

通常,一旦发出命令和数据转移已经发生,转移确认(XACK)是返回处理器以指示“READY”访问的从设备。处理器然后完成它转移周期。因此仲裁器用于多路复用处理器(或总线主站)到多主系统总线上并避免总线主控之间的争用问题。

优先解决技术

由于多主机上可以有许多总线主控器系统总线,一些解决总线之间优先级的方法必须提供同时请求总线的主人。82C89总线仲裁器提供了几种解析技术。所有技术都基于a的优先级概念给定时间,一位公交车主人将优先于其余所有人。有使用并行优先级解决的规定技术,串行优先级解析技术和旋转优先技术。

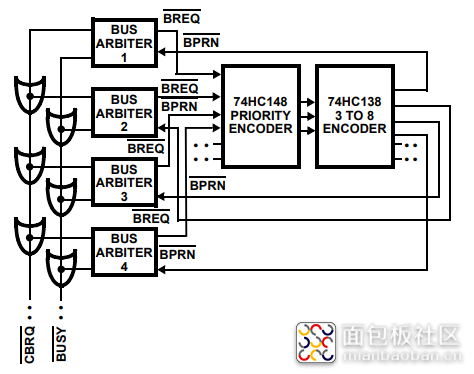

并行优先级解析

并行优先级解析技术使用单独的总线请求行多主系统上每个仲裁器的BREQ总线,每条BREQ线路都进入优先级编码器它生成最高优先级BREQ的二进制地址活跃的线。二进制地址由a解码

解码器选择相应的BPRN(Bus Priority In)行返回最高优先级请求仲裁者。该仲裁器接收优先级(BPRN为真)然后允许其关联总线主机尽快进入多主系统总线变得可用(即,公共汽车不再繁忙)。当一个总线仲裁器优先于另一个仲裁器,它不能马上抓住公交车,一定要等到目前的公交车交易完成。完成交易后目前的公共汽车乘客认识到它不再具有优先权并通过释放BUSY交出公共汽车。BUSY是一个活跃的低“或”连接信号线,连接到每个总线仲裁器系统总线。当BUSY变为无效(高)时,仲裁器目前有公交优先(BPRN为真)然后抓住了总线并将BUSY拉低以使其他仲裁器脱离总线。注意全部多主机系统总线事务同步到公交车时钟(BCLK)。这允许并行优先级解析电路或任何其他优先解决方案解决。

并行优先解决技术图

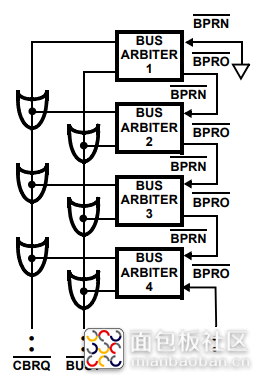

串行优先级解析

串行优先级解析技术无需使用通过菊花链进行优先编码器 - 解码器的安排总线仲裁在一起,连接优先级较高的总线仲裁者的BPRO(Bus Priority Out)输出到BPRN下一个优先级较低 见下图。

使用哪种优先级解析技术每个都有优点和缺点上述技术。旋转优先级解决技术需要大量的外部逻辑来实现串行技术不使用外部逻辑但可以在此之前只容纳有限数量的巴士仲裁员菊花链传播延迟超过了多主机系统总线时钟(BCLK)。并行优先级解决技术通常是另一方之间的妥协两种技巧。它允许许多仲裁者出现在总线虽然不需要太多的逻辑来实现。

82C89操作模式

82C89有两种类型的处理器

提供支持:输入/输出处理器(即NMOS8089 IOP)和80C86,80C88。因此,有两个82C89总线仲裁器的基本操作模式。一,IOB(I / O外设总线)模式,允许处理器访问I / O外设总线和多主系统总线。该第二,RESB(驻地总线模式)允许处理器通过Resident Bus和a进行通信多主系统总线。 I / O外设总线是一种总线该总线上的所有设备(包括内存)都被视为I / O.设备并由I / O命令寻址。所有记忆命令被定向到另一个总线,即多主机

系统总线。驻留总线可以发出内存和I / O.命令,但它是多主机系统总线的独立总线。区别在于居民巴士只有一个主人,提供完整的可用性和存在致力于那一位大师。IOB捆绑选项配置82C89总线仲裁器进入IOB模式,捆绑选项RESB配置它进入RESB模式。在这一点上可能会注意到,如果两者都有捆绑选项是假的,仲裁器接口处理器只能到多主系统总线。这两个选项都是真的,仲裁器接口处理器到多主系统总线,驻留总线和一个I / O总线。在IOB模式中,处理器通信并控制a外围总线上的外围设备主机。当I / O.处理器需要与系统内存进行通信

所以通过系统内存总线。处理器系统配置。

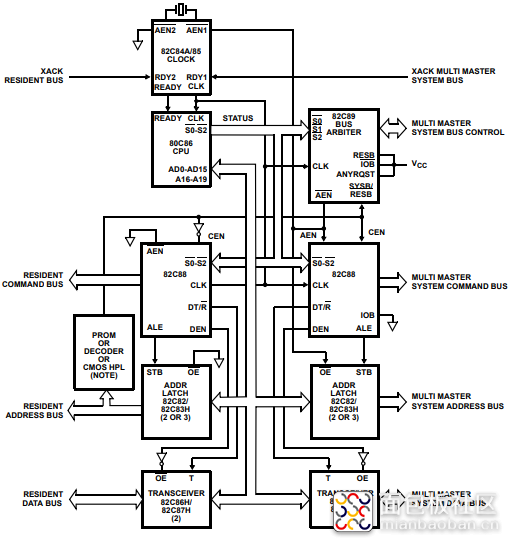

80C86和80C88处理器可以与a通信驻留总线和多主系统总线。两辆公共汽车控制器只需要一个总线仲裁器一个配置如图6所示。在这样的系统中配置处理器可以访问内存和两种总线的外围设备。内存映射技术是用于选择要访问的总线。该仲裁器上的SYSB / RESB输入用于示仲裁器至于是否要访问系统总线。该连接到SYSB / RESB的信号也可以启用或禁用来自其中一个总线控制器的命令。总结一下82C89具有的模式,以及对其状态的响应线路输入。

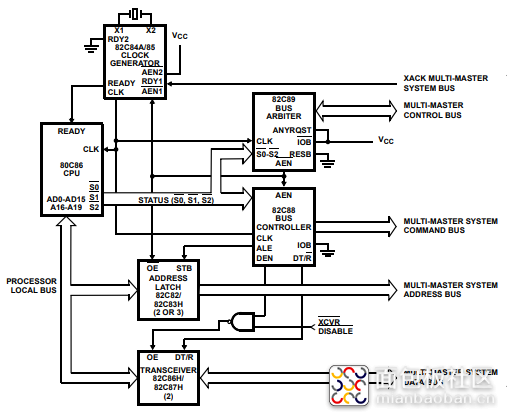

典型的中等复杂度CPU系统图

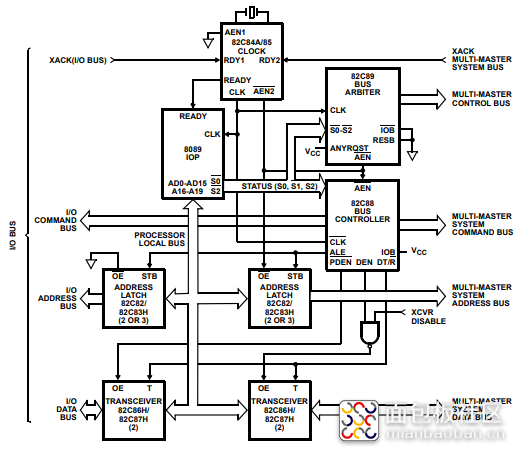

典型的中等复杂度IOB系统

系统中显示的82C89总线仲裁 - 驻留总线配置图

/4

/4