电阻的应用

datasheet:stm32f10x系列

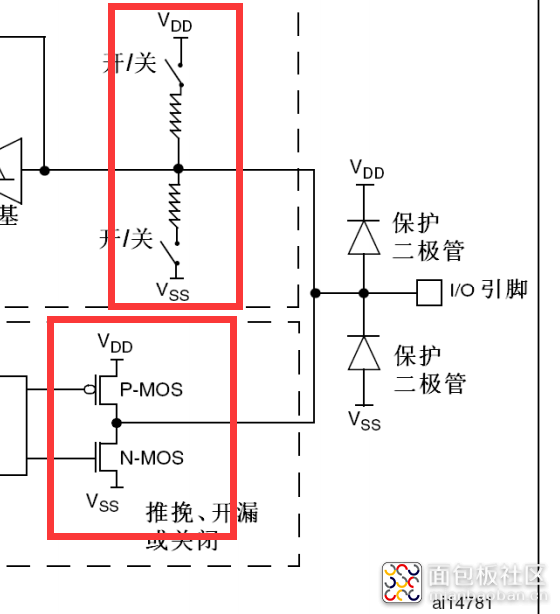

6、上下拉电阻

(1) 上下拉电阻一般在单片机的一些输出引脚上,或者信号线·上见到的多。首先来看下MCU外设gpio里面的一些原理图,以STM32的系列数据手册里面图片为例。VDD为高电位,VSS为GND,参考零电位。先见下上红框,接在VDD的电阻叫上拉电阻,接在VSS的电阻叫下拉电阻,由此可以看到的就是上下拉电阻的位置还受到开/关的控制,这个是软件控制。下红框,就是所谓的推挽电路,还有别的叫法就是图腾柱电路,在电力电子方面还有半桥的叫法, 没有PMOS的NMOS就是开漏电路,。这里PMOS就是电流从高电位VDD下来,流到I/O引脚。这里NMOS就是电流从I/O引脚往MCU,经过NMOS流回来的过程。没有PMOS的电路,就是开漏电路,反正单纯从名称上我是领悟不了先辈们的去理解整个电路形象化。两个保护二极管就是防止I/O口的电压大的模过大(正电路>VDD,负电压<VSS),倒流进电路,损伤电路内部,经验上再高点电压这个引脚就废了,严重整个IC都报废。在这个IC里内部的上下拉电阻,有强弱的叫法。我查过类似的文章,其实没有见到很权威的叫法,因为到底是强还弱和自身的电路匹配有关,没有明确的规定多大的电阻是强,多小是弱。如果能明确的把电路把电位准确的拉低和拉到就是合适的上下拉电阻。我曾经见过一个软件工程师,电路IO输入是拉低电路,内部程序是配置默认上拉,那么内部电路上拉电阻和IO口的下拉电阻形成一个分压电路,那IO口检测到电位就很有意思了。

(2)信号和网络的上下拉的,有IIC的上拉,SPI的上拉,485的A上拉B下拉,我以前就犯了一个错误,以为就是差分电路的信号(A-B就可以),我把A接了下拉,B接了上拉,结果整个电路就是经常出错,后来我给A接了一个上拉电阻,问题就解决了。

总结:对于一些初次使用的信号线路,测试过程中可以考虑加上一个NC上拉电阻作为备用,如果更加保守可以加上下拉电路,等待电路设计通过验证再加入主电路里,这是一个不断迭代优化的过程。

/5

/5