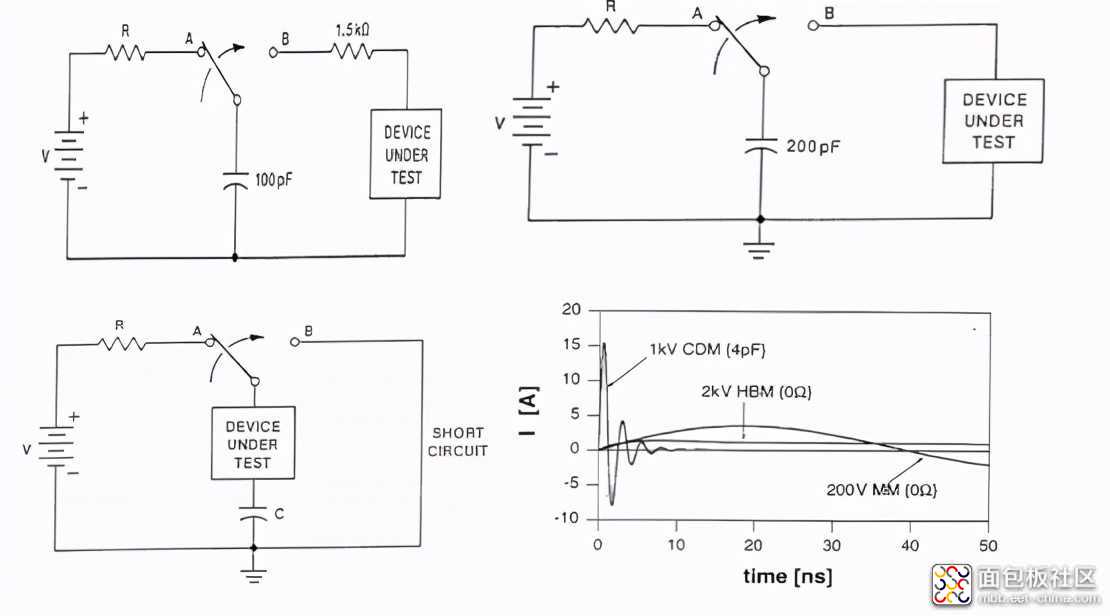

按ESD产生的原因及放电方式不同,ESD模式主要有人体放电模式HBM、机器放电模式MM、元件充电模式CDM这几种。相比于HBM、MM模式下电荷由外部经Pin由IC进入内部再由Pin输出,CDM模式中静电电荷由IC内部经Pin向外部泄放。HBM等效模型中人体电容为100pF、人体放电电阻为1.5KΩ;MM等效模型中等效电容为200pF;CDM等效模型中的等效电容无确定值。

ESD失效给芯片带来的损伤主要有热损伤和电介质损伤两种机制。热损伤的根本原因为短时间的瞬态大电流,由于半导体有较差的温度传导性质其散热性差,ESD电流能使得硅层和互连金属温度快速上升。电介质损伤主要针对MOS管的栅氧层损坏,由于栅氧层很薄(约为特征尺寸的1/50),栅氧所能承受的电压通常小于6V。电介质损伤一般由CDM失效导致。

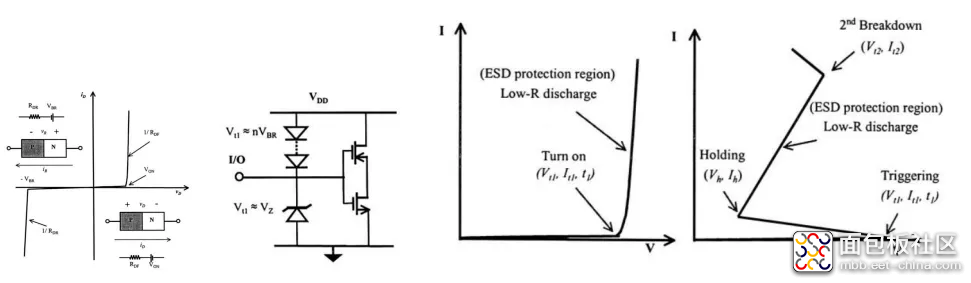

IC ESD的防护针对两个方面内容:①处理大ESD电流和②防止过大的电压。策略则是:①在所需要保护的电路/器件旁加入低阻抗并联通路以泄放ESD大电流,②利用钳位电路防止器件两端电压太大。

一.ESD防护器件

IC里可以通过加入相应的ESD防护器件和电路泄放ESD,防止内部电路失效。加入ESD防护器件和电路的首要原则是不能影响IC内部电路正常工作。

1)Diode

利用二极管反偏击穿特性,反偏二极管可以作为ESD保护器件。但是虽然正向二极管导通后电流可以达到很大,但是其开启电压太低所以不能作为Pin与电源间的负向ESD保护器件,可用二极管级联的方式增加开启电压 。通常的做法是Pin处二极管以反接的方式接到电源和地上,当对地打正的ESD时通过对地的二极管反偏击穿放电(但是阈值电压比较高),当对地打负的ESD时通过对地的二极管正偏放电(阈值电压低);当对电源打正的ESD时通过对电源的二极管正偏放电(但阈值电压低),当对电源打负的ESD时通过对电源的二极管反偏击穿放电(但是阈值电压比较高)。

2)BJT

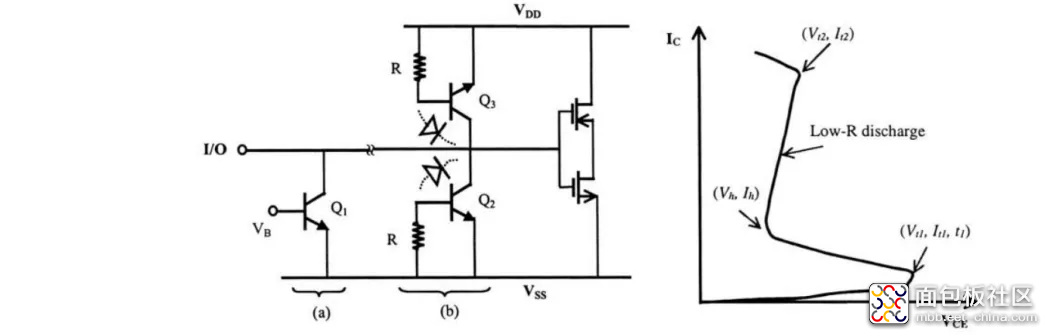

利用BJT集电结反偏击穿能产生的snapback I-V关系。以NPN为例,基极和接地之间加入电阻。该BJT接法为共射结构,其 时的 击穿电压定义为open-base breakdown voltage,为 ,其与发射结击穿电压 相关。正向ESD使得集电结反偏,电压超过第一崩溃点阈值 (由 决定)则集电结击穿。雪崩击穿产生的空穴进入基极,基极电流满足 关系,击穿电流方向 为集电极-->基极。在基极发射极外加电阻的情况下,基极电压大于发射极,发射结正偏,当 大于发射结开启电压后,BJT进入电流放大区,集电极电压下降,BJT进入低阻抗区,保持电压即为发射结开启电压。当电流继续增大到二次崩溃点 ,热量功率 大于器件能承受的极限值使得器件永久性失效。反向ESD,发射极电流方向为发射极向内,基极电流方向为基极向外,由于外加电阻的作用,发射结正偏,BJT工作在电流放大区。

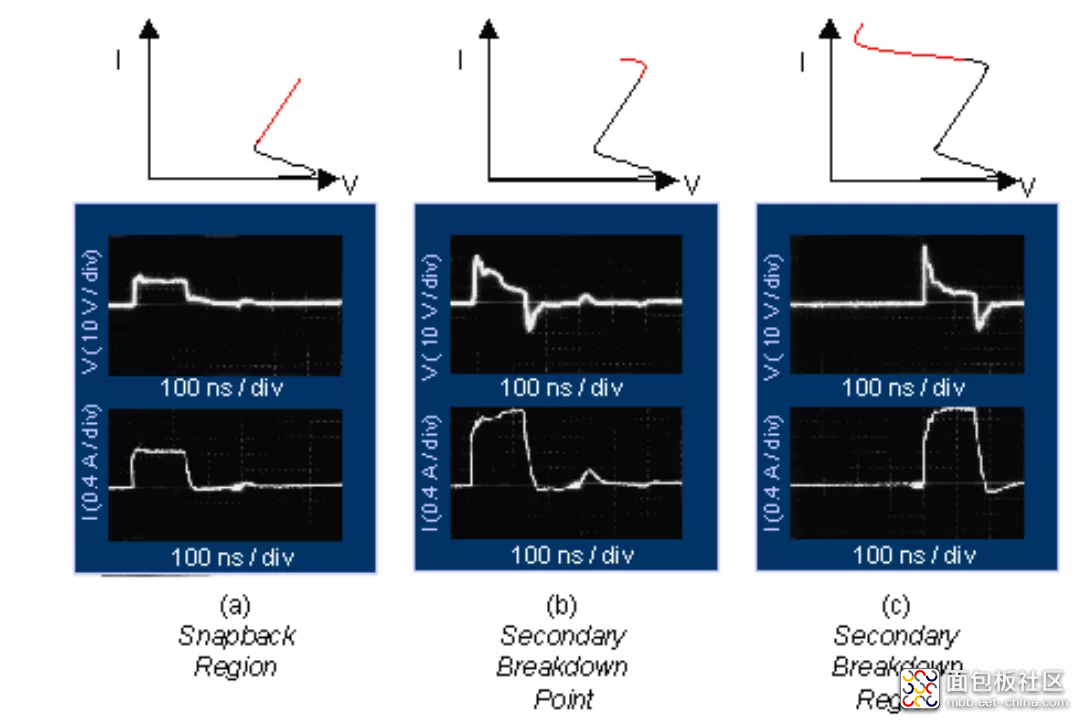

测试器件snapback常用的方法是使用传输线脉冲(TLP)的方法,利用传输线阻抗匹配和反射原理产生特定宽度(ns级别)特定高度的电压pulse,可以很好的模拟ESD事件。利用其他仪器测量出元件的第一崩溃点电压,以此作为充电电压的参考值。开始测量时,逐步增加充电电压,在示波器上可观测元件的电压/电流值。到了二次崩溃点时,会有电流突升而电压突降的波形产生。

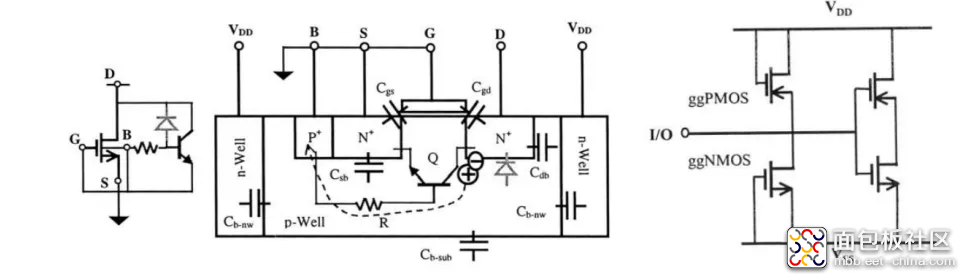

3)MOSFET

版图上可以看出制造NMOS时就对应有寄生NPN BJT产生,而且寄生NPN中,基极(NMOS衬底)面积很大,在基区到基极路径上会有寄生电阻R。如果将NMOS的源端和衬底连在一起,寄生BJT的连接关系和2)中ESD防护电路完全一致。同理,PMOS管也存在寄生PNP BJT。因此MOS管利用寄生BJT也可以作为ESD防护器件,为了保证正常工作时MOS不导通且无漏电,NMOS栅端会接地、PMOS栅端会接电源,被形象地称为GGNMOS、GGPMOS。寄生 时的 击穿电压为 ,其与漏衬击穿电压 相关,一次崩溃点电压与 相关。

一次崩溃点电压、保持电压、二次崩溃点电压等参数都与寄生BJT相关,无法用仿真仿真MOSFET的snapback I-V曲线。此外,由于寄生PNP的ESD放电效率小于寄生NPN,因此GGPMOS尺寸会比GGNMOS要大。

二.ESD防护策略

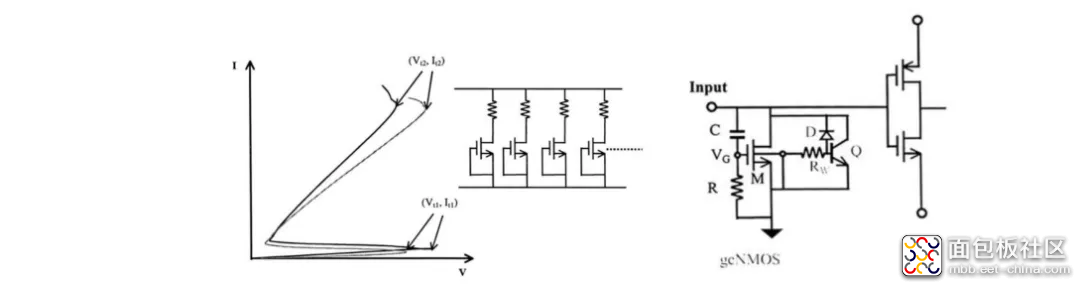

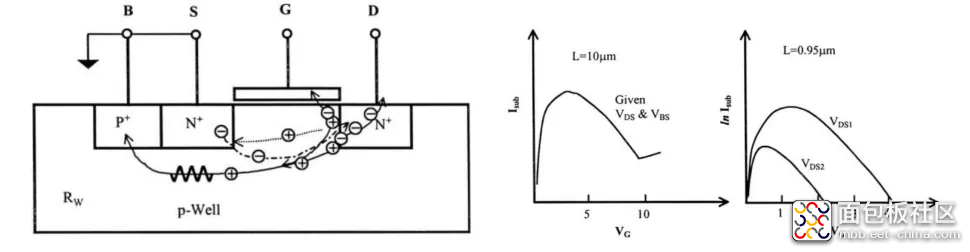

1)多Finger MOS----GC-MOS

ESD保护器件通常比较大,多finger MOS器件在ESD到来时,由于各段finger寄生不同,各段的第一崩溃点电压也会有所差异。如果器件的 ,极有可能发生ESD事件到来后只有部分finger对ESD起作用,直至器件烧毁一些finger仍未导通。为了防止该现象的出现,设计时会使得 。

GC-MOS结构就是其中的一种方法。当有正的ESD发生时,由于电容的耦合作用栅电压 被提升,产生了额外的衬底电流,此时由衬底端流出的电流 变大(原来只有寄生BJT的基极电流)。由于电流变大,寄生电阻 上压降变大,寄生BJT在更小的反向电流小即可进入放大区,第一崩溃点电压变小。而 与 的关系呈现为抛物线,通过R、C(需把GCMOS的栅端寄生电容考虑进去)设计正向ESD到来时 为合适的电压,即可实现 。 太大容易发生Latch up, 太大容易发生栅氧损坏,因此设计存在折中考虑。

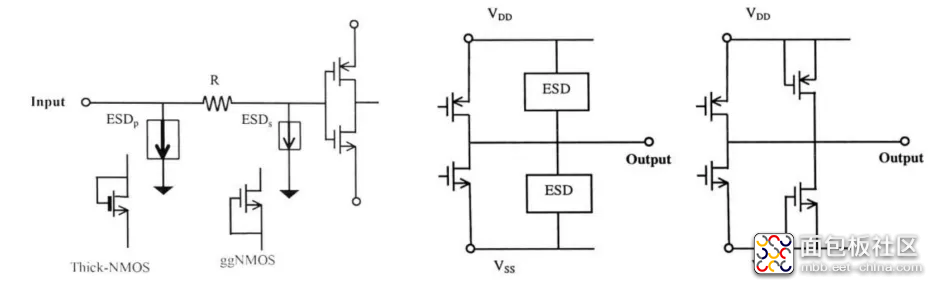

2)输入Pin的二级保护

输入Pin与MOS管栅端相连,而栅压耐压较小极易被ESD打坏,因此针对输入Pin ESD防护的策略上,有必要时会使用两级ESD防护,中间隔以电阻。第一级防护器件起主要ESD泄放作用,次级防护器件起辅助作用,其trigger触发阈值比第一级要大,而次级器件的阻抗需要比第一级高。

3)输出Pin的自保护

不像输入Pin接到MOS的栅端,输出Pin与MOS的漏端相连,因此输出Pin出现ESD损伤主要是烧坏金属的热损伤和输出MOS的寄生BJT的breakdown。输出MOS常常尺寸较大,因此只要流过输出器件的ESD电流不过大,具有ESD自保护的特性。设计ESD防护时,防护器件在ESD发生时要处于低阻抗以使得绝大部分ESD电流由防护器件流出。

4)Power Clamp

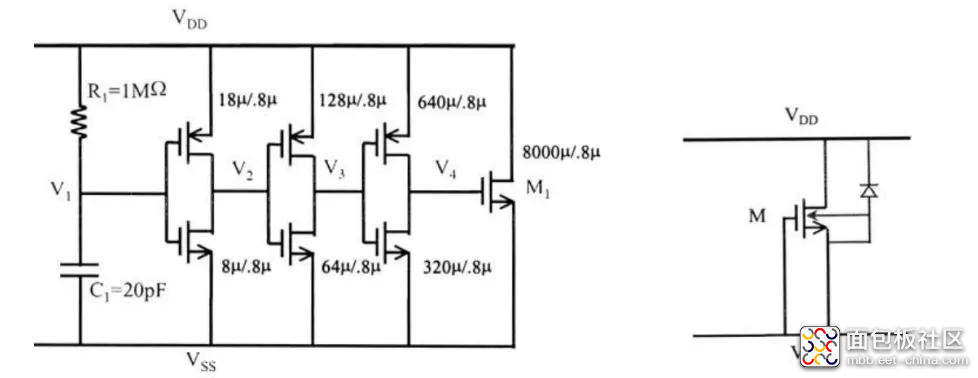

电源钳位电路主要放置在电源线和地线之间,保证在ESD到来时有低阻抗静电泄放通路,从而钳位电源总线为一个较低的电压值。最常使用的Power Clamp为NMOS Switch结构:用于放电NMOS的栅端有简单的控制逻辑控制。当有ESD正脉冲时,由于大电阻的作用,第一级反相器输出为正,再通过两级反向器整形和增大驱动能力,最终使得NMOS栅端为高,打开NMOS用于ESD电荷泄放。该电路泄放ESD能力可以通过仿真获得。

此外,也常用GGNMOS作为Power Clamp,在高压应用下,常以多个GGNMOS串联的方式作为Power Clamp。GGNMOS作为Power Clamp需要首先保证自己在ESD泄放时不被损坏,为了提高其承受ESD的能力,器件不会使用最小尺寸。电源线所接为PMOS的源端和衬底,ESD到来时GGNMOS通常会之于内部电路导通后慢慢崩溃导通,因此其不能有效地来保护IC内部电路。

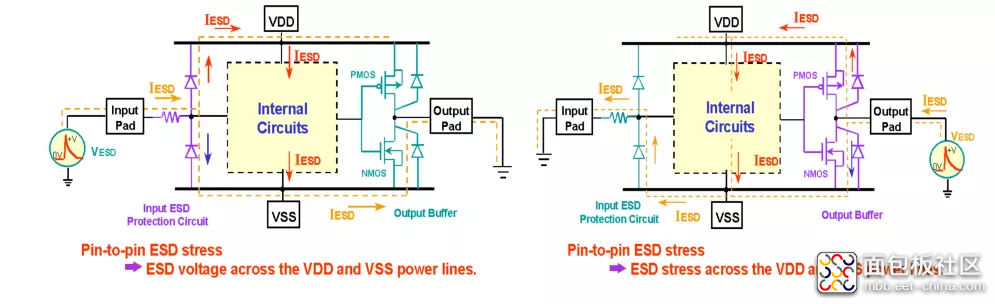

5)芯片全局防护

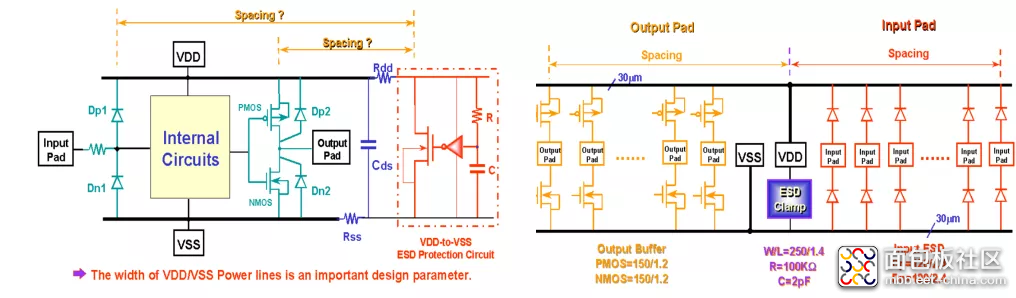

在多电源多地的IC中,通常电源和地之间会加有Power Clamp,但不一定遍历电源和地的组合。此外,输入输出Pin与各电源和地间不可能全部都有ESD防护器件,即使有防护器件也可能只是只有单向(正向或负向)ESD防护作用。而ESD事件可能是任意pin与pin之间、pin与任意电源之间、pin与任意地之间发生的,所以为了防护所有情况下ESD事件的发生,整个ESD泄放路径上要保证足够低的阻抗。整个ESD泄放路径上必然会包括某条电源线或某条地线,泄放路径上这些线的阻抗对于ESD泄放是否顺畅则至关重要,需要合理布局Power Clamp。

三.工艺对ESD的影响

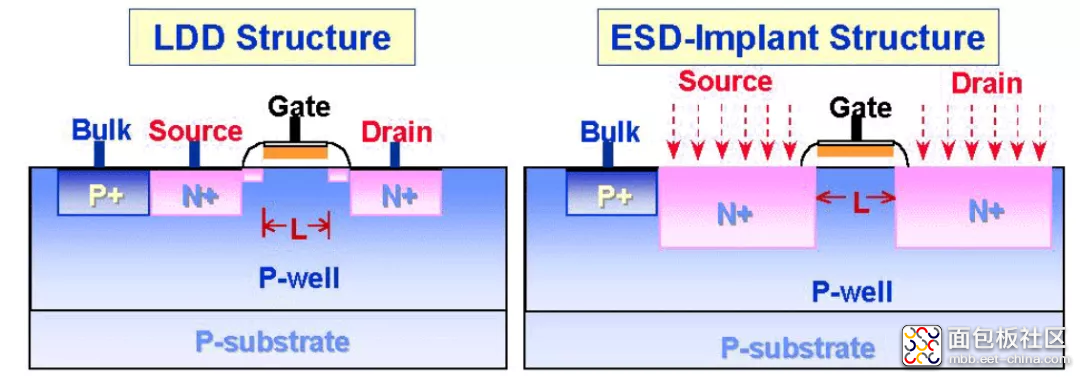

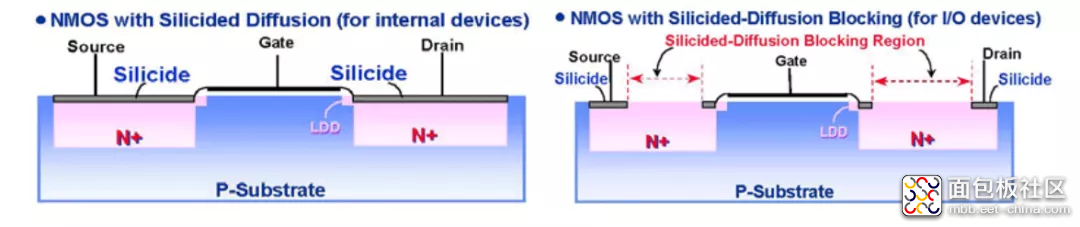

为了提高CMOS IC内部电路的运算速度、集成度以及器件可靠性,IC制程不断发展,但是这些制程的发展降低了IC ESD防护能力。随着MOS特征尺寸的缩小,MOS的栅氧厚度越来越薄,栅氧介质层越来越容易被ESD损坏。扩散层Silicided制程降低了MOS元件源漏区离散串联电阻、Polycide制程降低了MOS栅端离散串联电阻,Silicided+Polycide统称为Salicide。为了克服因热载流子效应所造成的I-V特性长时间漂移问题,LDD(Lightly-Doped Drain)轻掺杂漏制程用来降低MOS漏端在通道下的电场强度分布。而LDD深度很浅,等效在源漏极两端形成两个尖端,ESD时极易发生尖端放电现象,导致MOS器件被损坏。

为了克服LDD结构带来ESD防护能力的下降,制程中会有两种器件:一种为供内部电路使用的LDD结构器件,另一种是不具有LDD结构供I/O电路使用的器件。

为了提高器件ESD防护能力,Silicided-duffusion Blocking技术用于Silicided-duffusion的去除。

/1

/1