首先看一下MOSFET开关过程是什么样的?

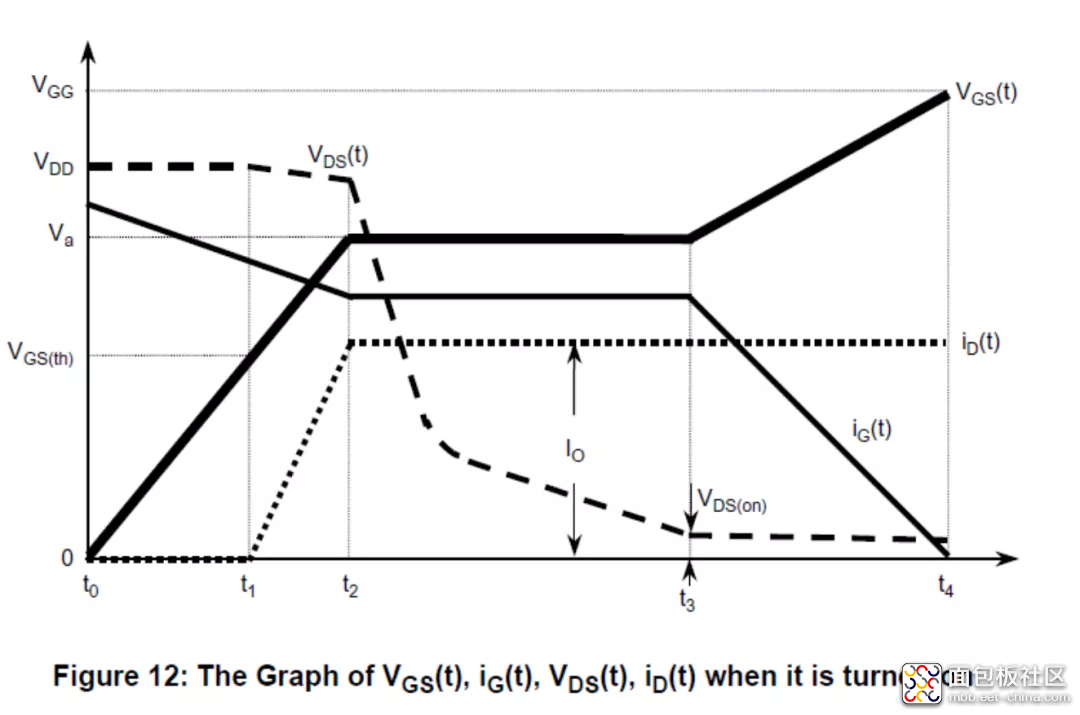

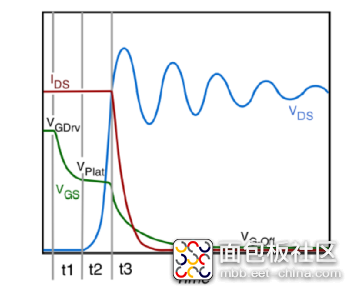

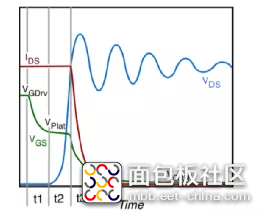

MOSFET开通过程如下,当Vgs>Vgsth时,漏极电流Id开始上升,Vgs达到密勒平台时,VDS开始下降(此时Vgs对Cgd充电),VDS下降近0时,Vgs继续上升至稳态,在这过程中Vds会缓慢下降(因为MOS的Rdson与Vgs相关)。

关断过程与开通过程类似,在Vgs下降至密勒平台电压,Vds开始上升(Vgs对Cgd放电),密勒平台结束后,Id随Vgs的下降而下降,直至Vgs<vgsth,MOS截止。

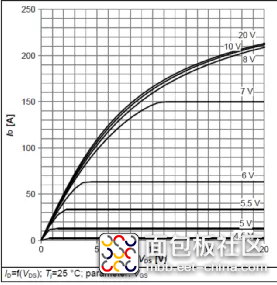

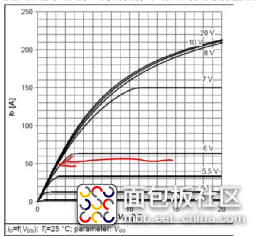

虽然开通关断过程比较清晰,在仔细深究的话还是有些不容易理解的地方,下图是MOSFET的输出特性曲线,MOSFET的每一个工作状态都可以反应在下图中,所以下图对开关过程的分析时很有帮助的。

1.密勒平台的电压由谁决定?

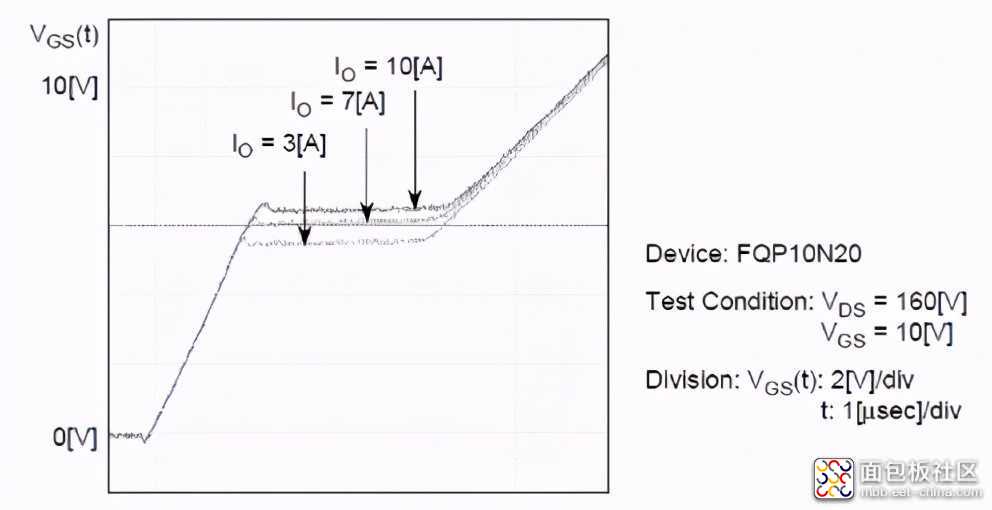

显然在开通或关断的密勒平台期间,Vds处在瞬态过程,Id处在稳态,即MOS在饱和区和可变电阻区之间切换,从MOS的输出特性曲线可以看到,不同的Vgs对应不同的输出特性曲线,所以密勒平台的电压是由稳态漏极电流的大小决定的,下图是很好的验证。

2.密勒平台期间为什么Vds处在瞬态过程,Id处在稳态?

当Vgs电压达到弥勒平台电压时,Id<gfs*vgs,式中gfs是跨导,显然此时Id已经是外电路允许的最大值,所以处在稳态。在开通过程中,Vgs=Vgs_miller时,因为Id进入稳态,所以Vgs再想增加,工作点只能在输出特性曲线中沿着箭头方向走,即Vds不断下降,关断过程与之相反。

3.实际开关过程中为什么不一定会出现密勒平台?

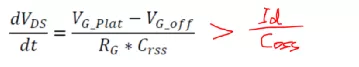

在软开关的场合,一般不会出现密勒平台。ZVS开通时,驱动开通前Vds已经降到零,所以没有密勒平台这一过程;虽然MOSFET均能实现ZVS off,但是这也并非绝对,如下图左,如果Cgd较大,或者Vgs回路阻抗较大,密勒平台持续时间较长,就没有ZVS off;但是如果Cgd较小,或者Vgs回路阻抗很小,Id还没来得及给Coss充电(低压下Coss较大,需要较大的充电电荷),Vgs就已经下降到Vgs_miller以下了,产生这一现象的条件是:

这时Id依然会随着Vgs的减小而减小,这样关断过程中,Vds与Id交结部分产生的损耗就很小,达到近似ZVS off的效果。

|

|

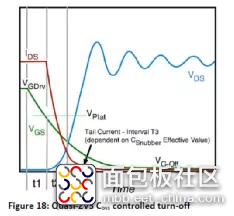

4.但是一味的提高关断速度就好吗?

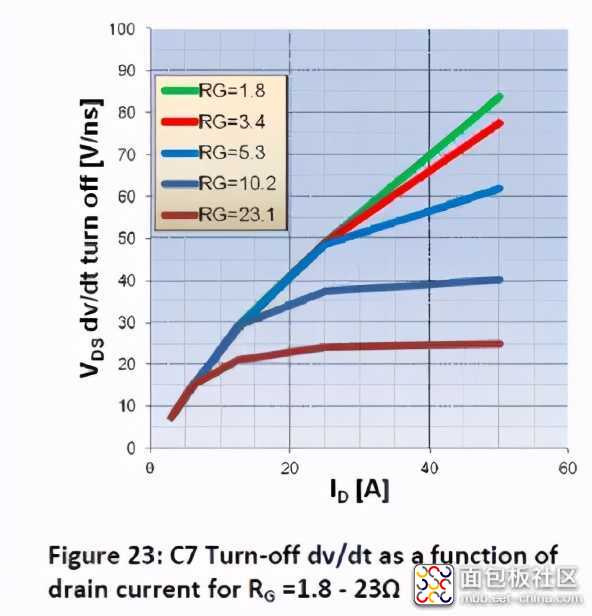

除去对EMI部分的影响,从下图中可以看出,当驱动电阻Rg较小时,关断时的dv/dt随着漏极电流的增大而增大,即dv/dt不受Vgs的控制,而受外电路的控制,这对于一些短路等故障条件是不利的,容易使MOS的dv/dt应力超限值。如果增加Rg,则能够降低关断速度,即关断速度受Vgs的限制,这样即便短路时漏极电流很大,MOS的dv/dt应力也很小。

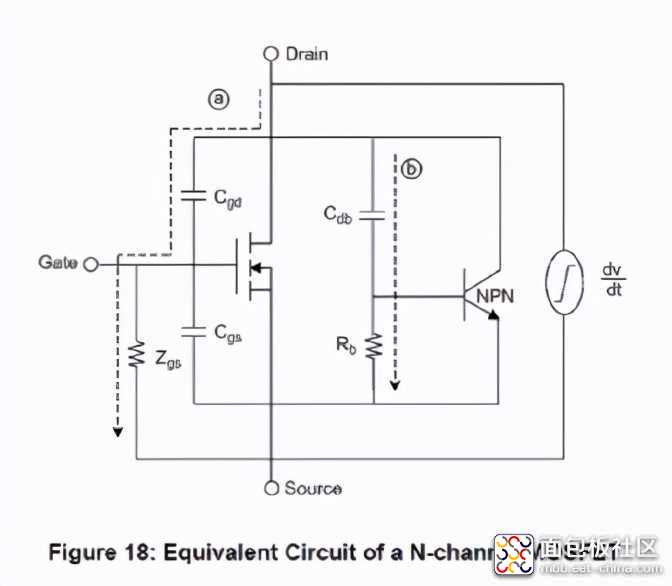

如果MOS的dv/dt超过一定限值,可能会触发MOSFET的寄生NPN三极管,即Rb两端的压降大于NPN的导通压降,使NPN导通,NPN工作之后,器件的击穿电压就变为原来的50%~60%,所以会产生击穿的风险。

内容转载自 网络,仅供学习交流使用,如有侵权,请联系删除。

/5

/5