良率是什么?准确的说,就是总共的芯片(可以是一片wafer,可以是一个批次,可以是一个产品,或者是一段时间内有多少芯片等等)。在这些芯片测试完成后,有哪些芯片是通过测试的,两者相除就是良率,为了聊起来方便,我们就拿晶圆级测试(CP)来做例子。

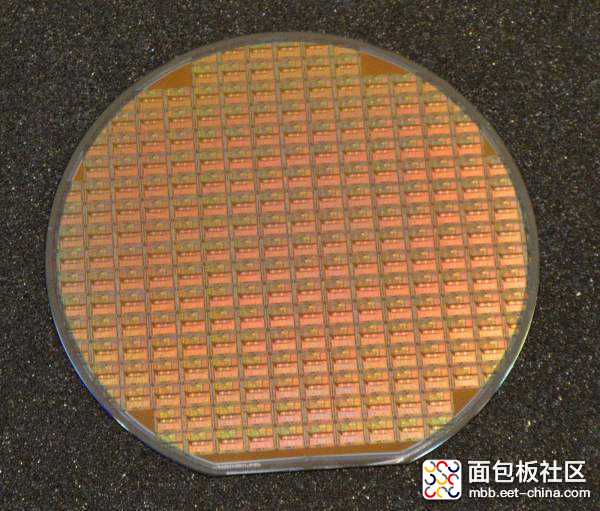

下面是一片foundry寄给测试厂的wafer,现在要进行CP测试了。

这里你也可能会问?难道foundry生产的wafer良率是0的话,难道fabless也要吃下?当然不是,每个foundry都有赔付标准,当一片wafer的良率如果低于某个值或者某条规则规定的值,而且是认定foundry的原因导致低良的话,fabless是可以找foundry索赔的。至于具体是多少,有哪些rule,这些涉及到商业机密,我们这里就不聊了。大家只需要知道有这么过程就好了。

这里还要说一下,不同产品的良率肯定是不一样的,设计越复杂,测试项越多,良率肯定越低。一个负责任的foundry都会针对产品做良率持续提升,直到这个达到这款产品应该有的良率(具体是多少请看第四part)。

至于FT测试呢,也有良率的问题,计算方法都一样,这里就不再多说了,理解一下就可以。与CP不同的是,如果FT低良,要首先判断是芯片本身的问题(foundry的问题)还是封装问题导致的低良(封装厂的问题)。至于判断方法嘛,这些东西太工程了,违反了我们普及半导体知识的目的,如果感兴趣,可以留言,我看看需不需要再写一期。

测试厂引发的良率问题

在这里还有一个问题,就是因为测试引起的低良问题。比如这颗芯片本身是没有问题的,但是如果probe card的制作不好,或者在测试的时候probe card的探针与芯片的引脚接触不稳定,又或者测试程序设置的时钟不合适等等。如果因为这些问题引起的低良问题,我们可以把它称作测试问题。这些问题会比较麻烦,如果有比较明显的测试map(稍后再聊这个概念),一眼就能看出来,但是如果没有特定测试图形,只能不断的去换probe card,换测试程序来验证了。

良率的重要性

良率这个概念影响了整个半导体产业链。对于fabless而言,良率直接影响了成本,良率高,成本低(因为同样的钱得到的芯片多了),良率低,成本高(相同的钱得到的芯片少了)。对于foundry而言,良率是它的根本,如果foundry生产出来了wafer良率低,没有人会在你这里下单。对于测试厂而言,测试问题带来的低良越少,就越能带来更多的客户。所以良率问题是整个半导体产业链的核心问题(很多问题都会围绕良率来展开)。比如有一些大的fabless公司,即使一片wafer的良率达到60%(假设整片wafer有100颗芯片,60颗能用),它也能在这片wafer上赚钱,因为价格高,我只卖40颗芯片,就能赚回整片wafer成本,另外20颗芯片就是纯利润。但是如果是一些小型fabless,由于芯片卖不出价格,价格低,自己又没有筹码和foundry谈一片wafer的价格,所以必须要卖出80颗芯片才能赚回整片wafer的成本。如果这片wafer良率低于80%,就是赔钱。

关于foundry什么因素造成低良,在这里就不介绍了,因为只有foundry才会研究这些。如果有人想了解,大家可以留言,我再开一篇文章~

良率是多少合适呢?

那一个产品的良率到底是多少的时候才是合适的呢?比如foundry说90%就是应该有的良率,但是fabless说95%才是应该有的良率。那遇到这种情况该怎么办呢?

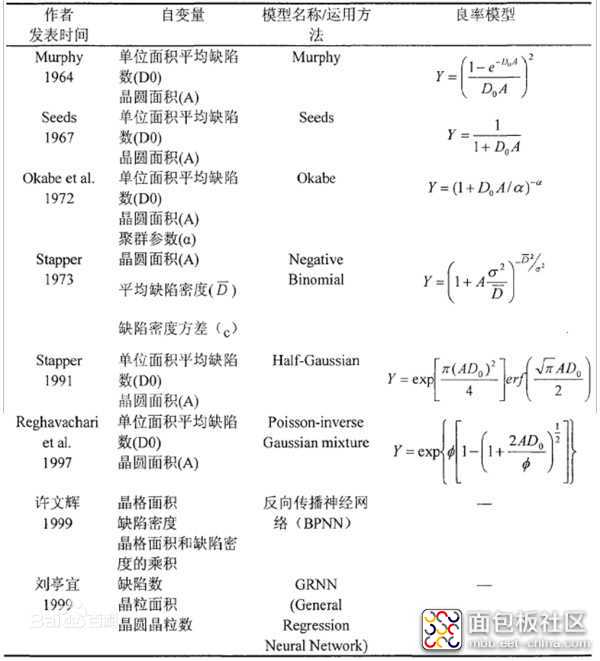

在业界,每个foundry或者比较大型的fabless都有自己的良率计算公式,根据fabless设计的芯片的复杂程度(比如用了多少nm的工艺,多少层掩膜版,有多少层是非常容易造成defect的,一颗芯片的大小等等)给出一个数学公式,比如下图

CP Map

伴随良率,经常会出现一个CP map的概念。在CP端有一个测试结果图形的问题(俗称CP map,这个问题比较专业,了解一下就可以),在测试的时候,测试厂会把测试结果好的芯片和测试差的芯片标记出来,这样就会有一个图形,如下图。

就到这里吧~后面聊一下关于产品质量的问题。

来源:公众号“半导体产业园”

/2

/2