简单谈谈TSMC的先进封装以及先进工艺

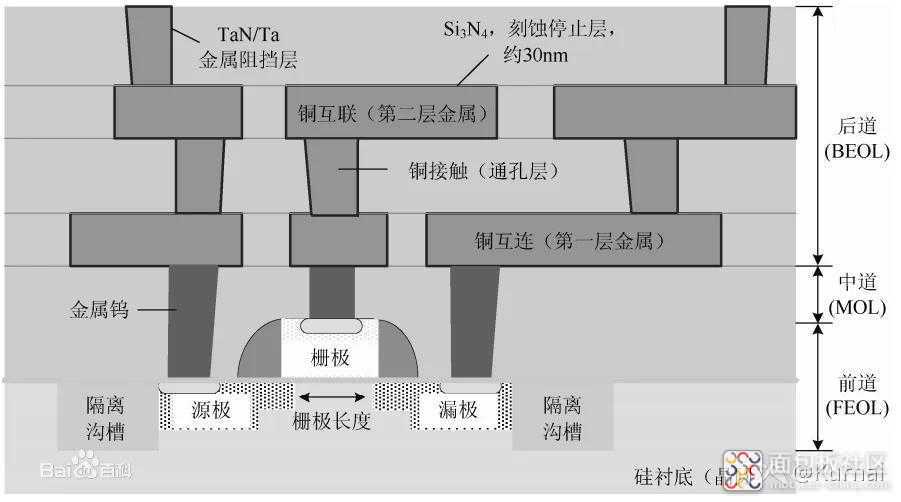

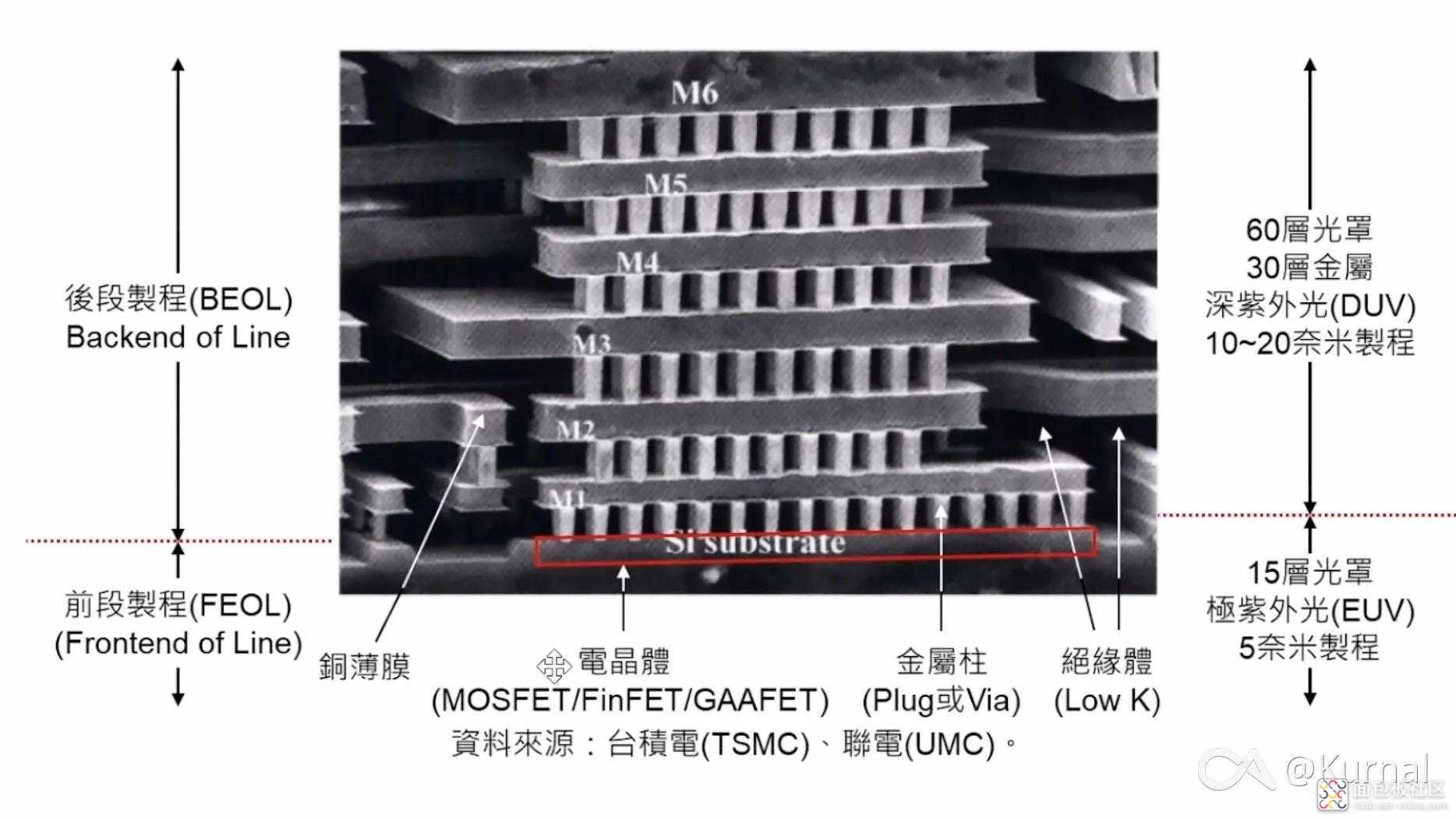

一个芯片,基本分3层,feol,beol,mol

Feol是前道工序,mol是中间工序,beol是后道工序

Feol涵盖了芯片有源部分的加工,就是芯片底端的晶体管,晶体管作为电器开关,使用三个电极进行操作:栅极(G),源极(S)和漏极(D)。SD之间的倒电通道中的电流的开/关,就是用栅极电压控制。常见的mos/fin/GAA之流就是这一阶段的

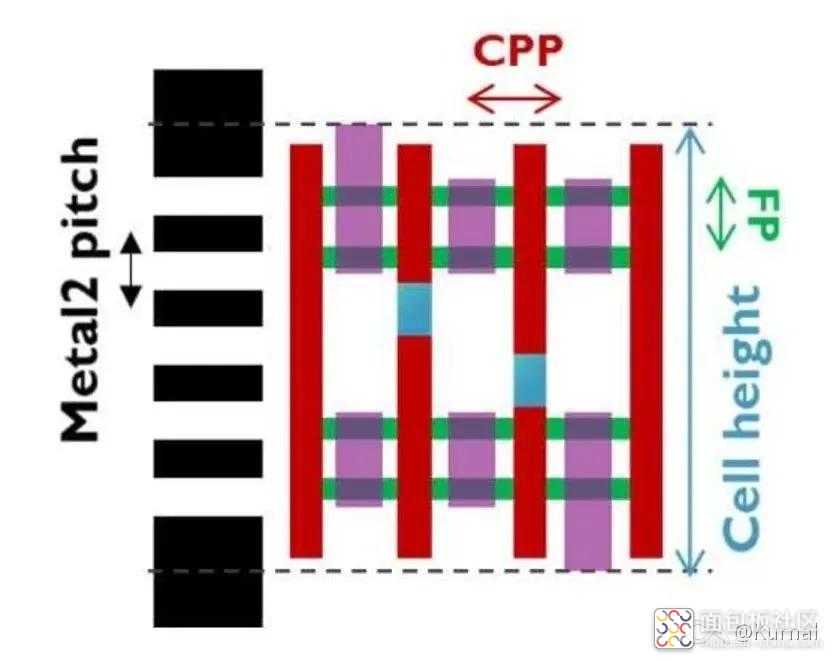

在一个32nm的mpu芯片中,栅极层的周期(CPP)

在130nm左右,但是,与逻辑电路不同,存储器的栅极由密集的线条组成(线宽与线间距达到1:1),它代表了整个器件中最小的周期。同时,在逻辑器件中,第一层金属层(Metal 1)具有和存储器件等间距的密集线条,即(m1的线宽和线之间的间距相等,但是逻辑器件密集图形的周期(pitch)一般要远大于同一技术的存储器件

Beol是加工的最后阶段,指的是芯片顶端的互连层,负责分配时钟和其他信号,提供power/gnd 并将电信号从晶体管传输到另外的晶体管,beol有不同的金属层,局部(Mx数字),中间线,半全局线和全局线组成,总层数10-15,Mx 层基本在3-6层之间,每层都包括了金属线和介电材料,广告上的晶体管大多数就是这种

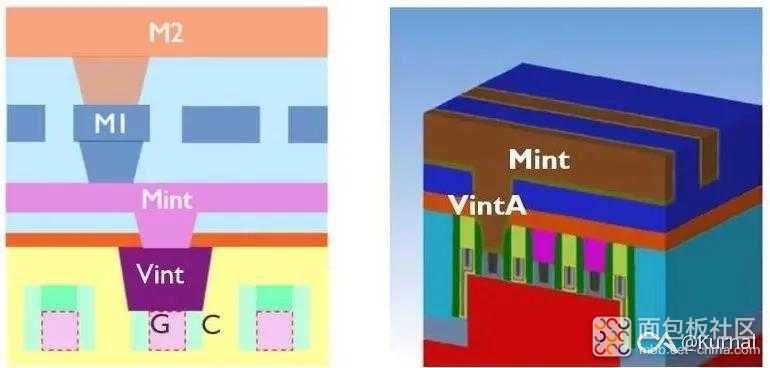

Mol就是feol和beol的互联层,由微小的金属结构组成,作为晶体管的源极栅极漏极的触点。最新点的就sagc,bpr之类

Track指的是走线轨道,信号线必须走在track上,常用的std cell库有7T/9T/12T,就是在std cell的高度范围内能走9条线,比如在7nm finfet中,track高度为6Trace的标准单元中,每个器件都有2个fin,接触间距小至57nm

之前的mol只能做单层接触,现在拓展到mint,vint之类的接触层了,

随着晶体管尺寸的缩小,可用于制造触点的面积也越来越小了,随之而来的的就会有寄生电阻的出现。通常是比如cell库没设计好啦(后端人紫菜)opc设计出问题啦(fab紫菜)等等

谈一谈封装

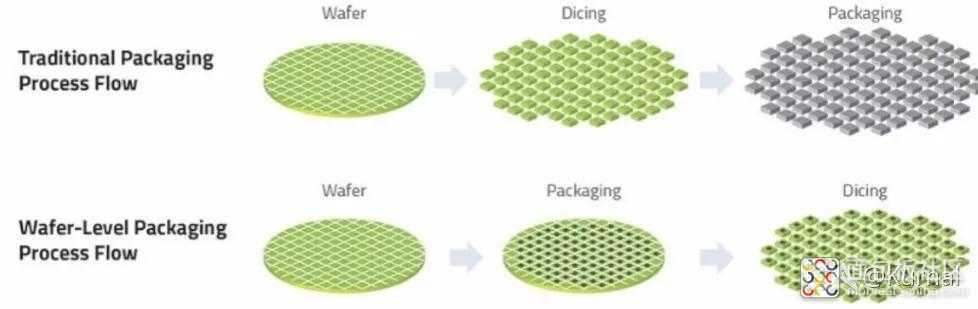

以前呢,封装得先割开后再布置导线最后用塑胶壳封装起来,现在可以先把整片晶圆用化学的方式把整片晶圆或者很多晶片一起封装,让他长出导线(RDL),再进行切割,叫做wafer level(晶圆级)(WL)

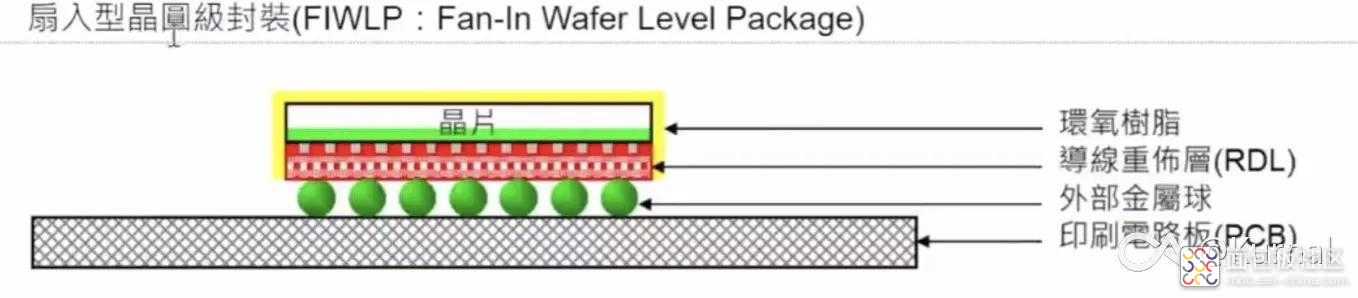

必须先封装再切割,导致了金属球较少,一共有两种封装, FIWLP(扇入晶圆级封装)

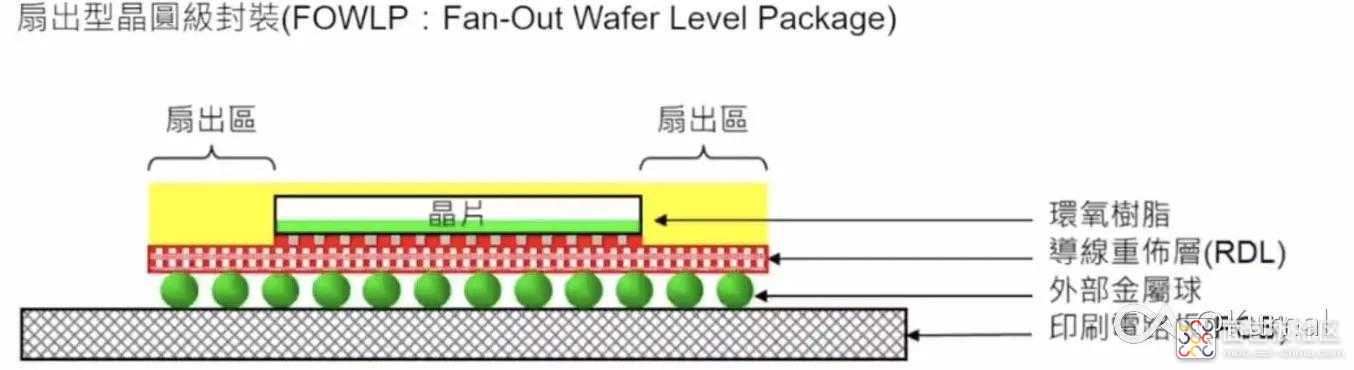

也有FOWLP(扇入晶圆级封装)

也就是其需要的RDL比较大,可以塞下更多的金属球与pcb互联,就只能先把晶圆切开再长出RDL再让其一起封装,所以也属于WL

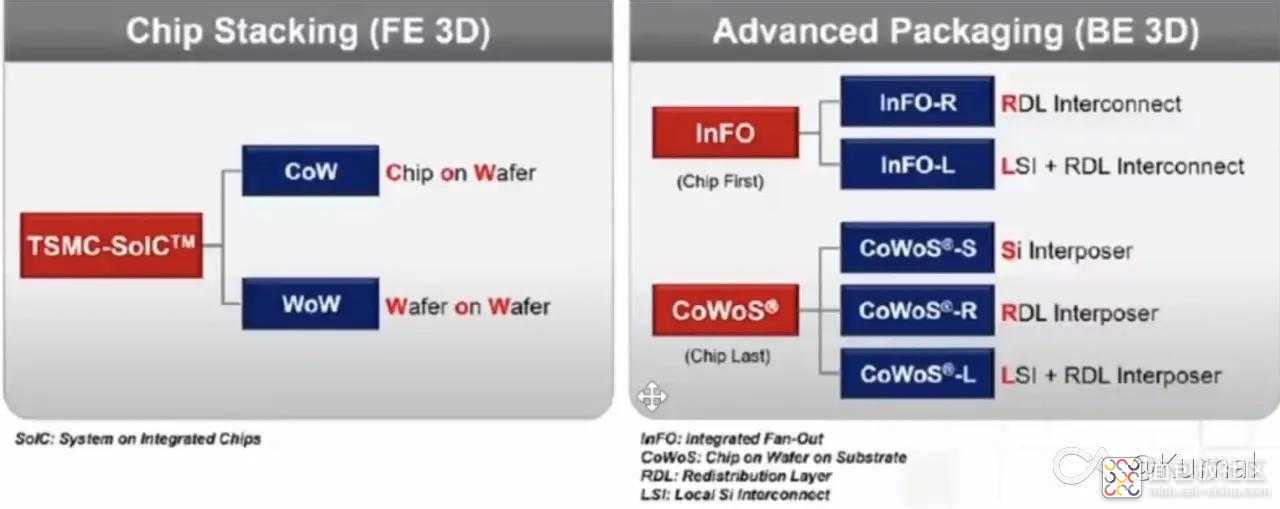

比如tsmc的chip stacking(FEol 3D)的SoiC,分为Chip on Wafer与Wafer on Wafer

Tsmc的先进封装(advanced Packaging(BEol 3D) 有inFO与CoWoS两条路线

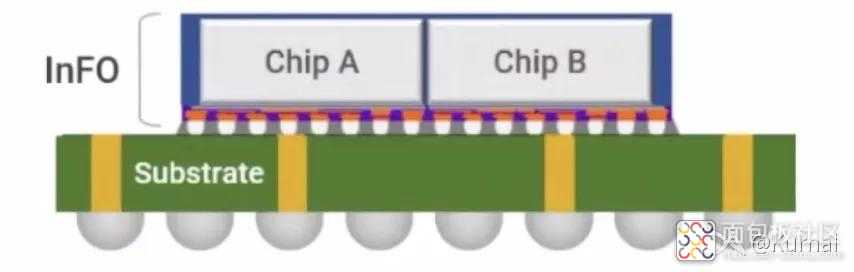

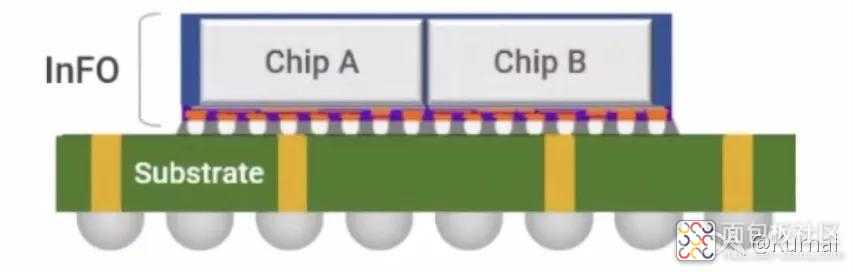

先谈谈inFO吧,inFO是整合扇出型,可以把两片chip封装在一个树脂里,用导线连接到substrate

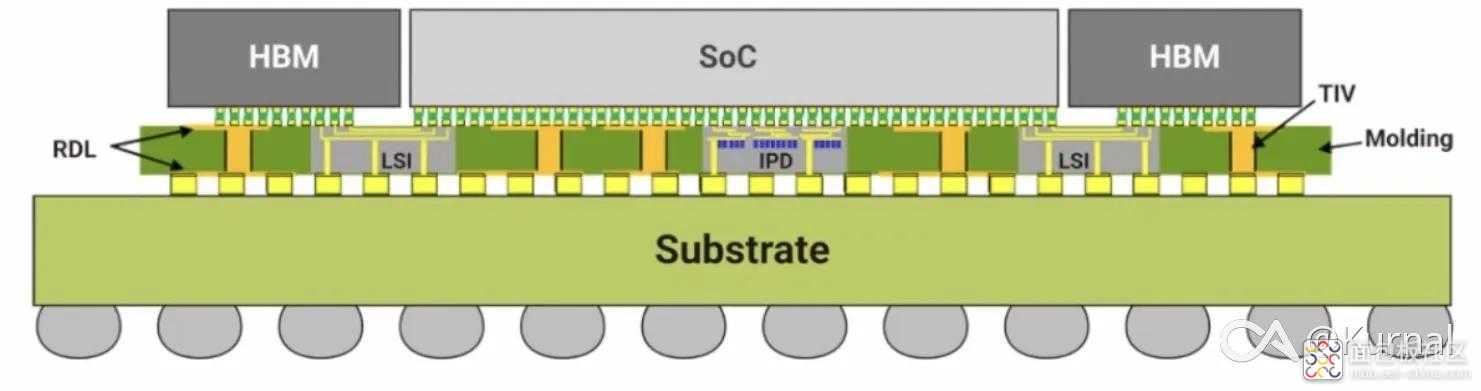

inFO分为(inFO R(RDL)inFO L(LSI+RDL)

再详细点呢还有inFO PoP,inFO oS

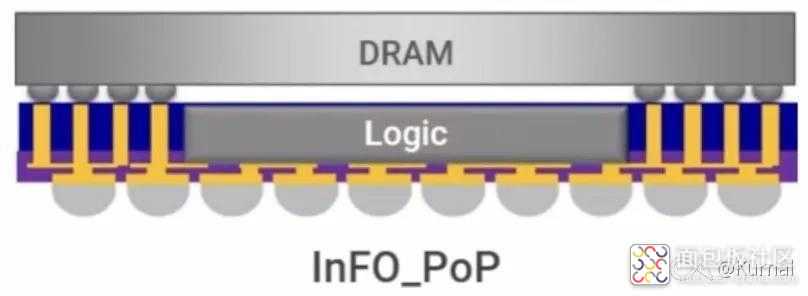

inFO PoP就是处理器朝下,用化学做出导线重布层(RDL),RDL预留了很多金属导线,记忆体在处理器上面,用微凸块那些预留的金属导线

inFO oS就是两块及以上的芯片,在si中介板中重新布置导线,再连接到SUB上

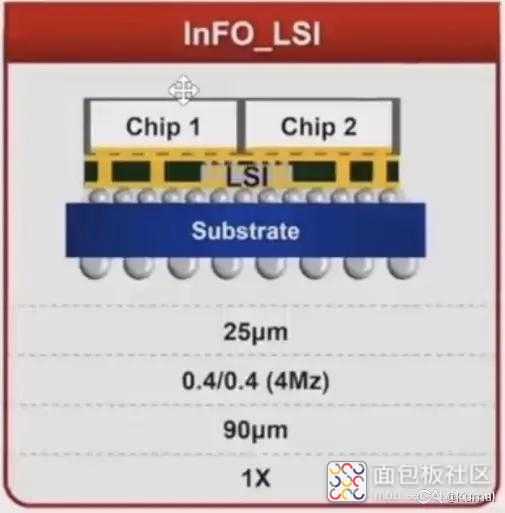

InFO R 就是多chip封装到一个sub上,InFO L就是在chip下还有一片SI中介板,里面有很多Si穿孔,上面与chip传输用LSI,然后经过Si中介板传到SUBs

R(RDL:导线重布层的连接方式)

I(LSI:区域Si互联)

之前苹果用的都是info r,更小的体积

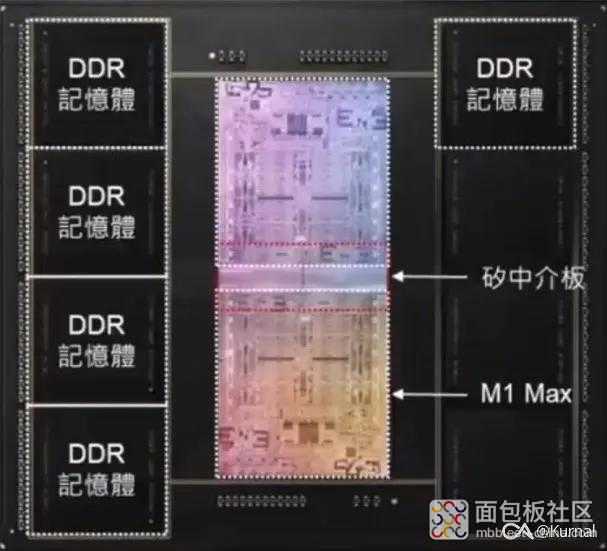

M1u的UltraFusion就是用了inFO L,中间用一块小的Si中介板(LSI)把他们连接起来(1+1),再用RDL把他们整个封装起来(=2)

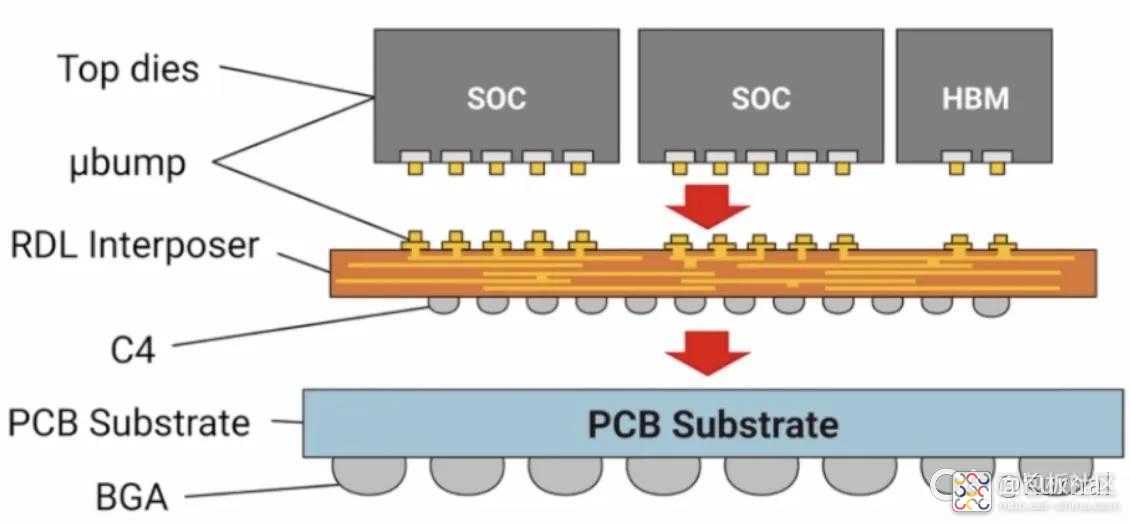

CoWoS就是Chip on Wafer on Substrate(晶片堆叠晶圆堆叠基板)

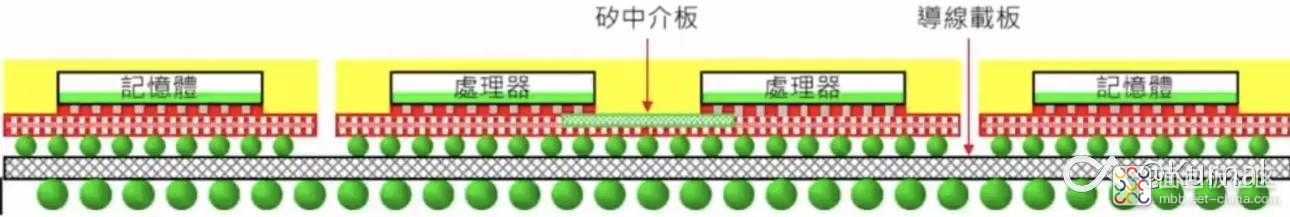

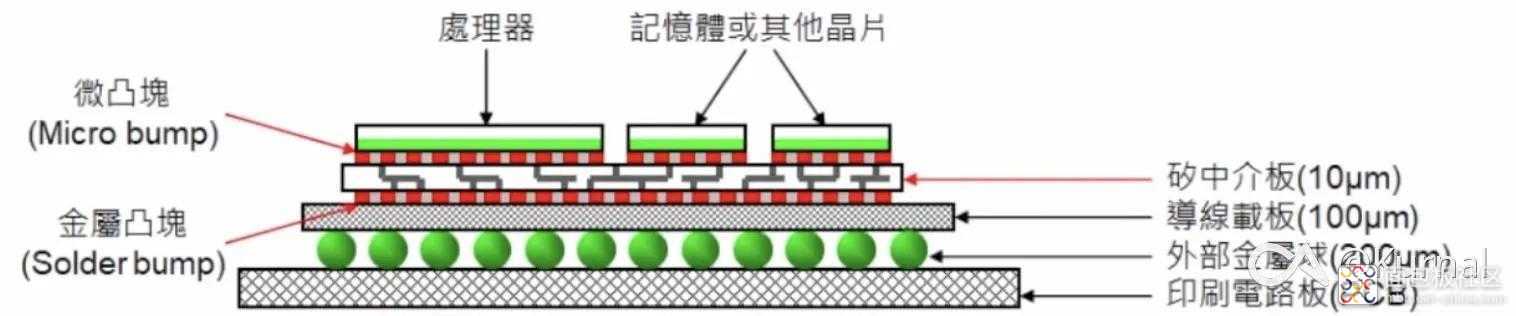

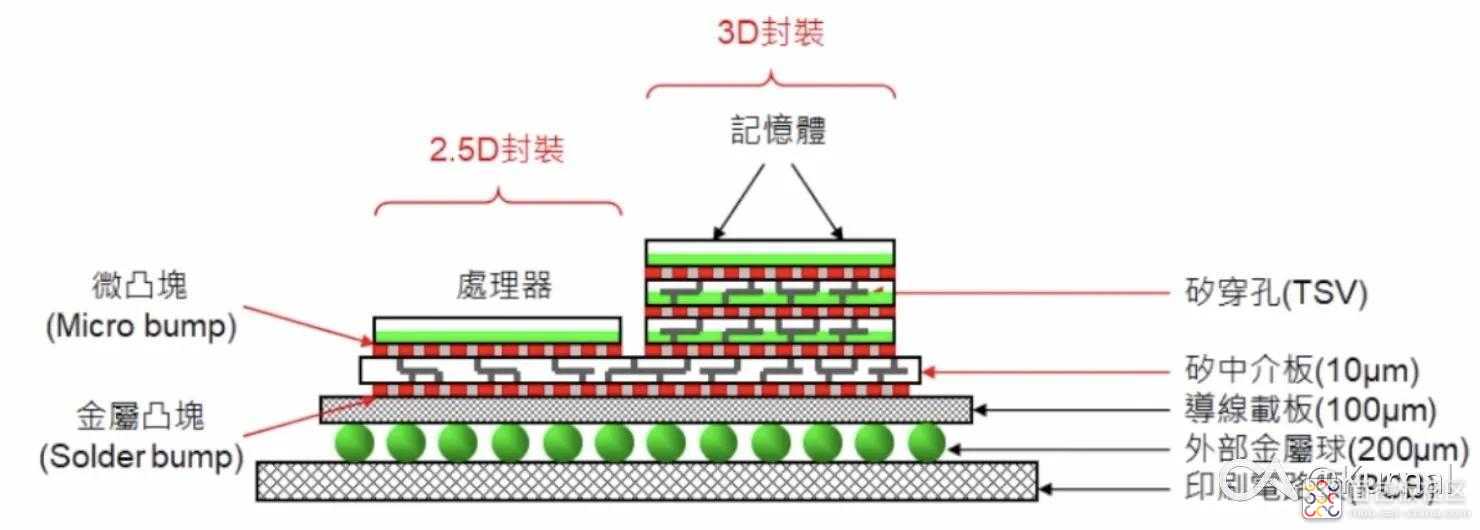

CoWoS分为2.5D与3D,就是多颗IC经过Si穿孔的Si中介板,到导线载板再到pcb上。

就比如mpu他只能单片封装,chip用微凸块(micro dump)硅中介板,硅中介板用金属凸块(Solder dump)链接RDL(CoWoS),算是2.5D封装。但是比如hbm的技术的记忆体,可以多块堆叠,叫(CoCoCoCoCoCo...CoWoS)(不是)算是3D封装,就是在CHIP中进行硅穿孔(TSV),把chip堆叠起来的封装,对,就是R9 Nano之类的

基本上分三类,CoWoS S,CoWoS R,CoWoS L

CoWoS R就是多块SOIC与单块HBM用微凸块连接到到RDL的Si中介板,Si中介板在用金属凸块连接到SUB

CoWoS L 就是单块SOIC与多块HBM封装在一起,但是,在一整个导线重布层中,HBM有专门的电源线(tiv)与信号线(LSI),信号线用LSI与soc通讯(顺便穿过Si中介板,找到金属凸块连接到sub板上

来源:Kurnal

/4

/4