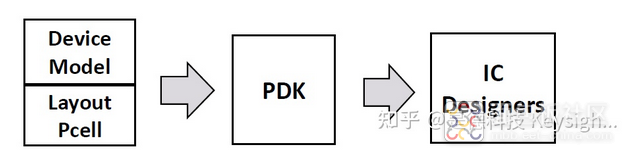

半导体器件模型是连接代工厂和IC设计公司之间的桥梁。如图1所示,IC设计工程师在电路设计软件中调用的器件,包含了器件模型和版图的信息。只有精准的器件模型才可以保证精准的电路仿真结果。

图1

器件模型有很多种类型,包括查表法,集约模型 (Compact Model),宏模型 (Macro Model) 等。半导体器件模型多是集约模型和宏模型。

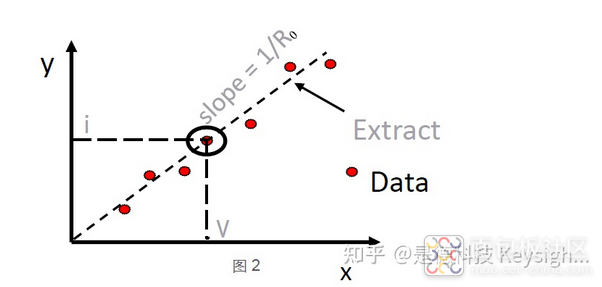

举个最简单的电阻模型的例子。假设有一组测量的电流电压 (V,I) 的数据,符合线性关系,测试数据如图2所示,V和I之间的关系可以通过一个直线方程I=V/R来描述。通过调整R参数,在R=R0时可以得到与数据点拟合最好的结果。

这个例子说明了半导体器件建模的两个步骤:

第一步,找到合适的方程;

第二步,参数提取。

对于MOSFET, BJT, 和Diode等半导体器件的建模也是一样的概念,只是描述这些器件特性的方程更为复杂。实际工业应用中,半导体器件大多已有标准可用的方程,如BSIM3和 BSIM4等,只需要进行参数提取即可。

图2. 半导体器件建模参数提取

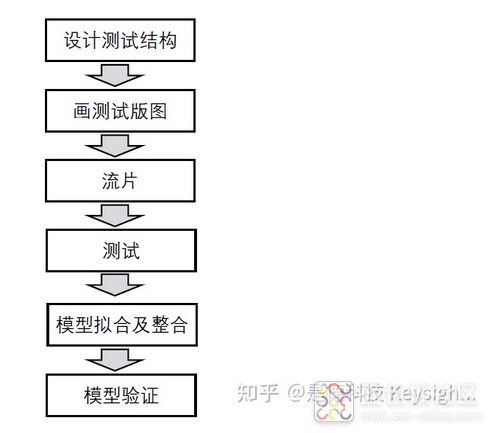

半导体器件建模的基本流程

要建立半导体器件模型,首先要有测试数据,并且是足够多的测试数据,要能够包含足够多的尺寸、能够反应工艺条件的平均和边界的水平。

所以,为了做半导体模型,工程师会需要设计专门单独器件的测试结构,去流片并进行测试,然后根据测试数据,拟合曲线提取参数。得到的参数列表保存出去,即可得到可用于SPICE仿真的模型文件。最后将各类器件的模型拼成一个模型库,并进行验证后,方可将模型移交出去。

MOSFET global model -- Best Fitting model提取步骤(BSIM4为例)

首先,提模型需要有测试数据。测试时先要进行mapping的测量,即测量wafer多个die在某个固定bias下的Target(Vtlin,Vtsat,Vtgm,Idlin,Idsat等)数据,然后根据mapping测试的结果选出各个target都比较靠近中值的一个die作为golden die。然后再测量golden die的CV,IV曲线。在拿到测试数据后首先需要检查数据,包括曲线是否正确、趋势是否合理,还要检查下IV曲线的target是否与mapping测试的中值有较大偏差,有问题的数据需要重新测试。

提模型时通常会以前一版本的模型为基础进行调整,如果没有前一个版本的模型可以选用默认的模型去调。下文具体看下MOSFET global model提取的基本步骤:

第一步,将工艺物理参数(如氧化层厚度等)填入模型中去。

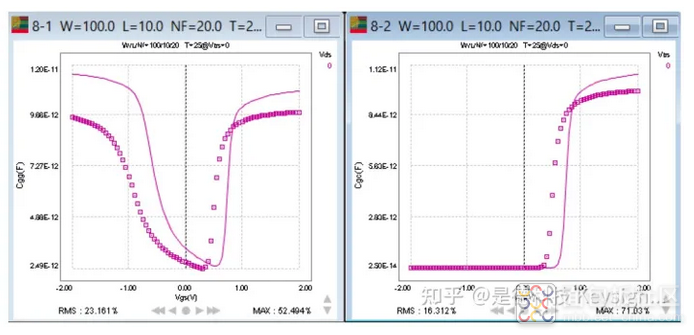

第二步,CV 的拟合:包括CGG和CGC 的拟合,如图4所示。

图4

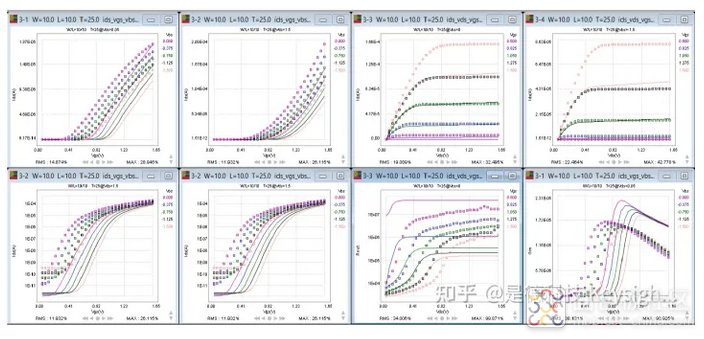

第三步,IV的拟合(图5):

图5

1. 大尺寸器件IV 曲线拟合,这一步需要拟合的曲线包括图5中所列出的曲线:

a. id_vgs_vbs (vds=0, vds=vdd), 需要同时拟合线性坐标和对数坐标的图,还需要照顾到Gm(id_vg取导数)曲线,调整vth0和迁移率相关参数进行曲线拟合。

b. id_vds_vgs (vbs=0, vbs=vbb), id_vd曲线的拟合也要照顾到Rout(id_vd曲线取dx/dy)曲线。

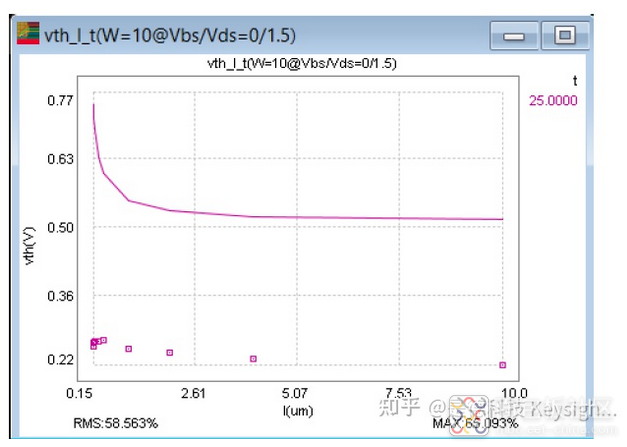

2. W=Wmax, Vtlin,Vtsat,Vtgm,Idlin,Idsat,Ioff等target对L的趋势图的拟合,可以使用IV曲线中计算出的趋势图,也可以直接使用mapping data的趋势图。如图6是一张Vtlin_L的趋势图

图6

3. 短沟道器件IV曲线拟合。这个步骤与步骤1中大尺寸曲线拟合类似,需要使用短沟道相关的参数去做拟合。

4. L=Lmax, Target对W的趋势图。与步骤2中类似,使用相关参数拟合不同target对W的趋势图。

5. 窄沟道器件IV曲线拟合。与步骤1、3类似,使用窄沟道相关参数去拟合。

6. L=Lmin, target对W的趋势图,以及W=Wmin, target对L的趋势图。参考步骤2、4。

7. 小尺寸器件的IV 曲线拟合。参考步骤1、3、5。

8. 重复步骤1-7直至所有曲线拟合精度达到要求,将最终结果保存出去,就得到了以测试数据为基础的 Best fitting model.

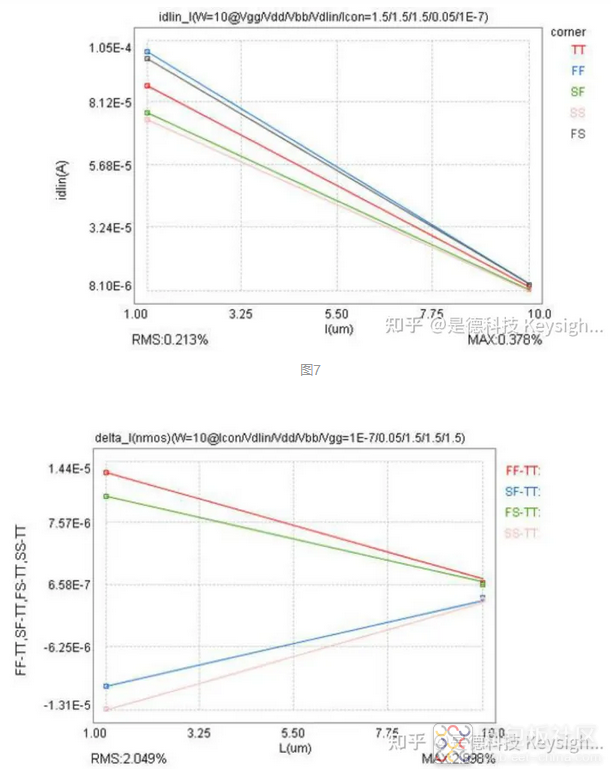

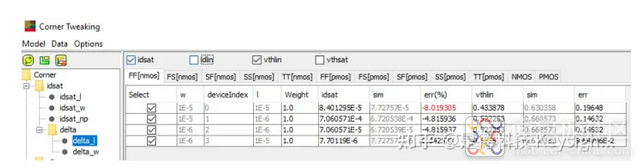

MOSFET 全局模型 - 角落调整 (MOSFET global model – Corner Tweaking)除了针对模型晶圆本身测试数据选golden die进行的拟合IV, CV以及调整趋势做retargeting之外,模型还需要有个能代表工艺波动状况的边界模型,就是我们所说的corner模型。做corner模型需要有corner spec,在foundry里corner spec通常由工艺整合工程师 (PIE)提供。Corner model可以由base模型去生成一个corner lib,可以通过手动去贴一个corner lib出来或者直接使用MBP等工具由base模型去生成corner lib。调corner模型需要看的图有corner趋势图(图7)和喇叭口的图(图8),喇叭口是代表计算之后的各个corner与TT之间的差异的图。对照corner 趋势图和喇叭口的图,并同时结合spec table(图9)去调corner 参数,使得corner 仿真值能达到spec并且保证趋势和喇叭口正确。

图8

图9

半导体器件统计模型(Statistical Model)

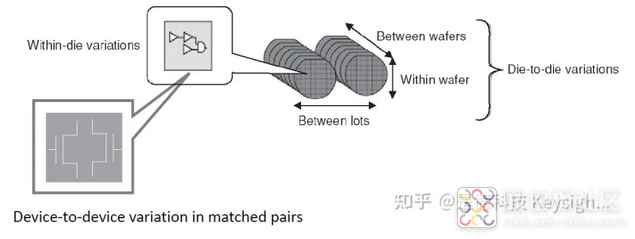

随着器件尺寸缩小,器件随工艺的波动会越来越明显,我们需要通过统计模型来描述器件随工艺的波动。工艺的波动可以分为几种,有相邻器件之间的差异,称为局部波动(local variation),局部波动也称作失配(mismatch);还有不同die,不同wafer,不同lot之间的差异,称为全局波动(global variation),总的波动(Total variation)是全局波动与局部波动之和.

Total variation = Global variation + Local variation实际做模型时,local variation是直接测量得到的,所以mismatch模型通常都是由测量结果拟合得到;total variation也是可以直接测量得到,但是global variation无法直接测量得到,但是可以通过上面公式计算得到。所以global 的统计模型可以根据测试数据去做,使仿真结果与测试数据同分布即可。

用于 CMOS 和 III-V 器件建模与表征的产品和解决方案,包括自动化测量、精确的器件模型提取、全面的模型认证、PDK 验证和综合建模服务。

MBP 是一站式硅器件建模解决方案,能够自动、灵活地进行硅器件建模。

用于行业标准 CMOS 模型的完整直流和射频建模提取套件。

本技术概览对完整的器件表征解决方案做了阐述,介绍了如何使用 B1500A 半导体器件分析仪来满足各种测量需求,包括从基本的 IV 和 CV 测量到超快速脉冲及瞬态 IV 测量。

来源:是德科技

/4

/4