- 引言

- 一、有限状态机的相关概念

- 二、经典的三段式有限状态机的Verilog代码实现(标准模板)

引言

状态机!!!非常重要!非常重要!非常重要!重要的事说三遍!

可能你还没有搞过比较大的 FPGA 工程设计,没有体会到一大堆时序状态信号、时序控制信号、时序顺序操作的费神费脑,甚至,可能是无底洞的一个时序设计,毕竟时序是设计出来的,我们需要有一个规范的时序设计套路,类似于 IC 验证需要一种方法学如 UVM 一样。后续,我会根据具体的设计来详细进行 FSM 的设计思路讲解。

一、有限状态机的相关概念

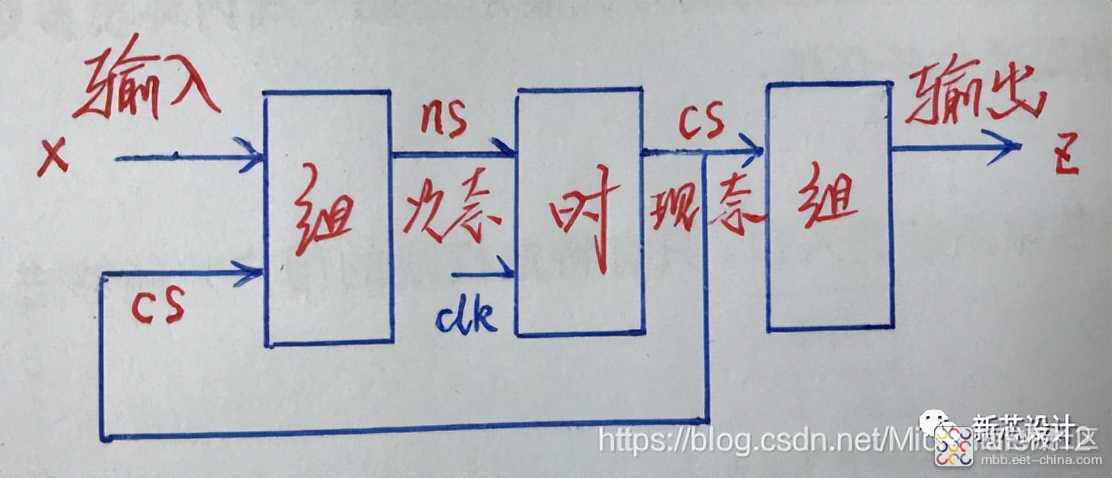

有限状态机(Finite State Machine):FSM 由状态寄存器和组合逻辑电路构成,是一个能够进行状态转移与状态输出的控制模块,是协调相关信号动作、完成特定操作的控制中心。

有限状态机主要分为两大类:第一类,若输出仅与状态有关,则称为 Moore 状态机(通常都是这个);第二类,输出与状态和输入都有关,则称为 Mealy 状态。

如下所示,这是有限状态机的架构图,需要我们非常了解。

有限状态机架构图

二、经典的三段式有限状态机的 Verilog 代码实现(标准模板)

module FSM( input clk, input rst_n, input x, // 输入序列 output reg z // 检测结果 ); // FSM中主要包含现态 CS、次态 NS、输出逻辑 OL; parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; // 状态编码,采用格雷编码方式,S0 为 IDLE reg [1:0] c_state,n_state; /*---------------次态到现态的时序逻辑------------*/ always @(posedge clk or negedge rst_n) begin if(!rst_n) c_state <= S0; else c_state <= n_state; end /*-------现态在输入情况下转换为次态的组合逻辑------*/ always @(c_state or x) begin case(c_state) S0:begin if(x) n_state<=S1; else n_state<=S0; end S1:begin if(x) n_state<=S1; else n_state<=S2; end S2:begin if(x) n_state<=S3; else n_state<=S0; end S3:begin if(x) n_state<=S1; else n_state<=S2; end default:n_state<=S0; endcase end /*--------------现态到输出的组合逻辑---------------*/ always @(c_state) begin case(c_state) // 从 S3 要变化到 S2 这一刻; S3: z=1'b1; default:z=1'b0; endcase end endmodule

复制代码

/4

/4