Sigma-Delta ADC的运作过程,就是把待测信号Vin与参考电压(±Vref)之间的差值进行不断的累积并通过反馈令这个差值趋于零。

实质上ADC就是除法器。

Dout=(Vin/Vref) * 2^n

一个分辨率为n位的ADC完成了一个以Vref为除数的除法,并且把结果用n位二进制数来表达。

那么什么是Sigma-Delta ADC?

Sigma-Delta最终实现的,与所有的ADC一样,就是完成除法。模拟集成电路中除法器是不可实现的,但是模拟电路可以非常好的实现加法和减法(用运放及模拟开关对电容进行充放电)。Sigma-Delta ADC正是用加法和减法去实现除法的一种方式。

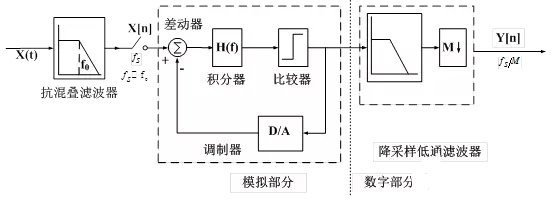

具体来说,如图2所示,Delta-Sigma ADC的工作原理是由差动器、积分器和比较器构成调制器,它们一起构成一个反馈环路。调制器以大大高于模拟输入信号带宽的速率运行,以便提供过采样。模拟输入与反馈信号(误差信号)进行差动(delta)比较。该比较产生的差动输出馈送到积分器(sigma)中。然后将积分器的输出馈送到比较器中。比较器的输出同时将反馈信号(误差信号)传送到差动器,而自身被馈送到数字滤波器中。

图2 过采样ADC结构图

这种反馈环路的目的是使反馈信号(误差信号)趋于零。比较器输出的结果就是1/0流。该流如果1密度较高,则意味着模拟输入电压较高;反之,0密度较高,则意味着模拟输入电压较低。接着将1/0流馈送到数字滤波器中,该滤波器通过降采样与抽样,将1/0流从高速率、低精度位流转换成低速率、高精度数字输出。

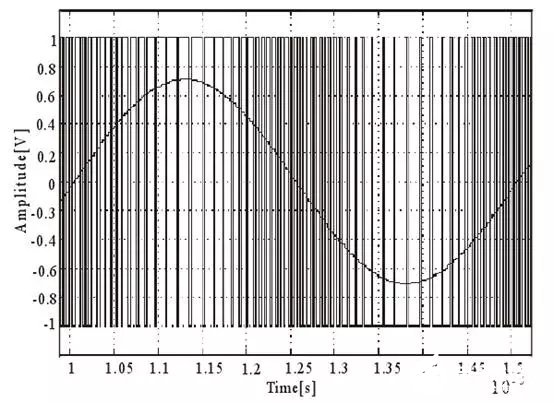

一个正弦波输入信号与比较器输出的码流所对应的波形如图3所示,输出码流随着输入信号幅值的变化而变化,当输入信号处于波峰位置时,输出码流1占大多数;当输入信号处于波谷位置时,输出码流0(图3中,以-1表示)占大多数;输入信号处于平衡位置时,输出码流1和0跳变激烈,各占50%。

]

]图3 正弦信号幅度与比较器输出的码流所对应的波形

sigma-delta ADC也有不同的结构,其特点可以如表1所示。

/2

/2