处理器

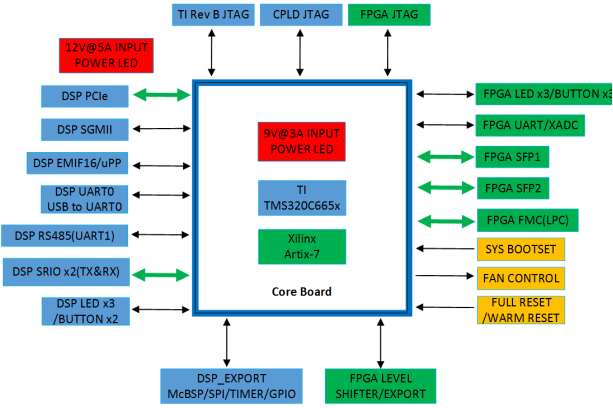

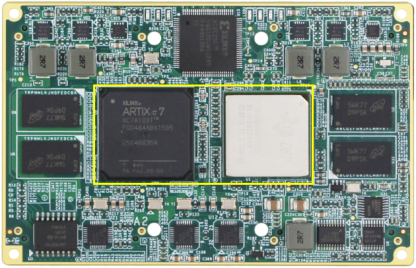

基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x + Xilinx Artix-7 FPGA处理器,TMS320C665x主频为1.0G/1.25GHz,单核运算能力高达40GMACS和20GFLOPS,FPGA XC7A100T逻辑单元101K个,DSP Slice 240个拥有多种工业接口资源,其CPU功能框图:

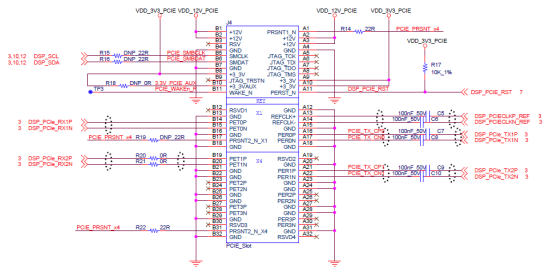

PCIe接口

开发板引出了PCIe Gen2接口(J4),2通道,编码方案为8b/10b,总共64pin,主接口区42pin,单通道理论最高传输速率达5GBaud,总传输速率为5GBaud*8/10=8Gbit/s,硬件及引脚定义如下图:

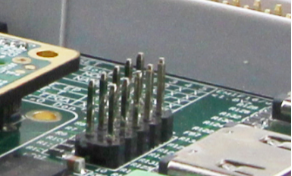

模式调试接口

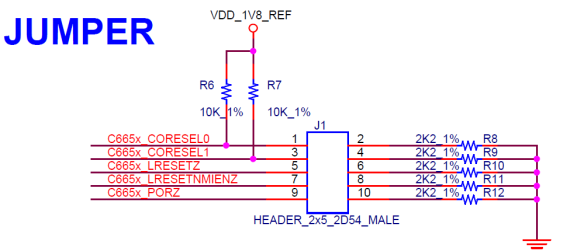

开发板J1为模式调试接口,采用2*5pin、2.54mm间距双排针连接方式,主要用于复位、NMI等调试,硬件及引脚定义如下图:

CORESEL0/CORESEL1:核心选择管脚,用于选择启动或者复位的核心。

LRESETZ:Warm Retset软复位管脚。

LRESETNMIENZ:模式选择使能管脚。

PORZ:上电复位管脚,用于上电时的复位行为。

/4

/4