简单介绍绘制时序图的相关基础概念。

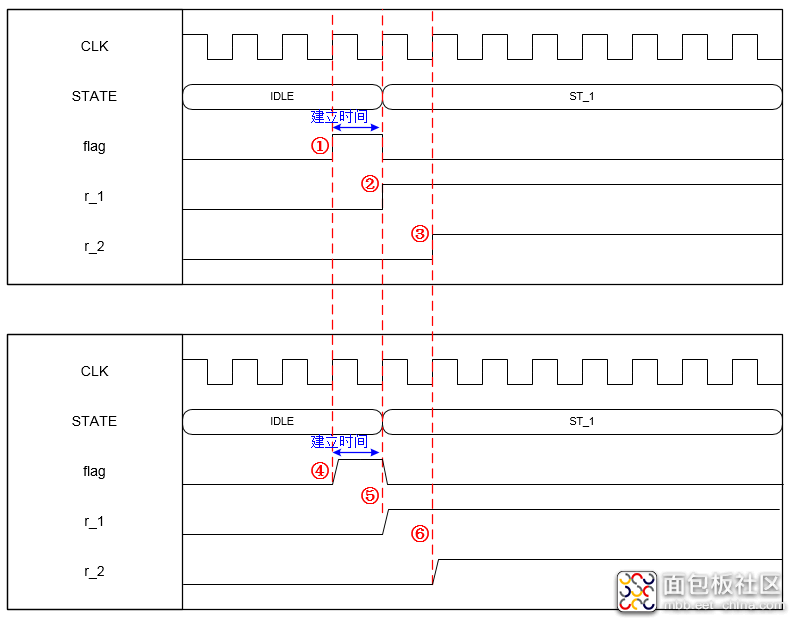

一般时序图绘制有两种方式,如下图所示。上面的是理想波形,与modelsim仿真中波形一致;下面的考虑到信号由低到高的上升时间,本质没有区别。

两种绘制时序图的方式应用都很广泛,也各有优势。Xilinx手册中使用第二种方式绘制时序图挺多的。第一种方式在实际工作中广泛使用。

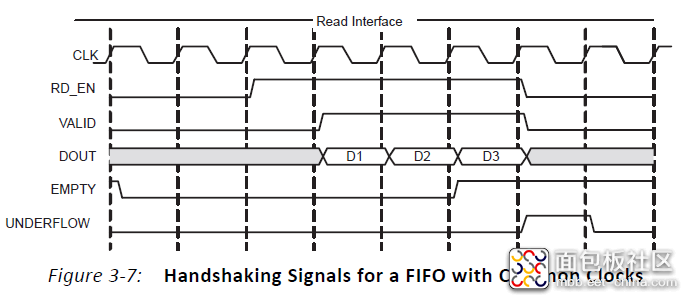

比如,下图是Xilinx FIFO手册中部分时序。

概念一:时序图中的建立时间

在图一上部分图中,flag信号在时间线1和2之间的部分,一般理解为该flag信号的建立时间(setup time)。建立时间是指时钟到达之前,数据和使能信号已经准备好的最小时间间隔。只有在时间线2时刻,clk才能采样到flag的高电平。

概念二:理解信号拉高与状态机之间的关系

在IDLE状态,如果检测到flag=1,则跳转下一状态,同时拉高标志r_1。可以看见,在状态跳转的同时r_1被拉高。但只有在时间线3/6及以后的时刻,才能采样到r_1=1。在时间线2/5时刻r_1=0。

在ST_1状态,当在时间线3/6检测到r_1=1时,拉高r_2信号。

/4

/4