CMOS工艺流程介绍

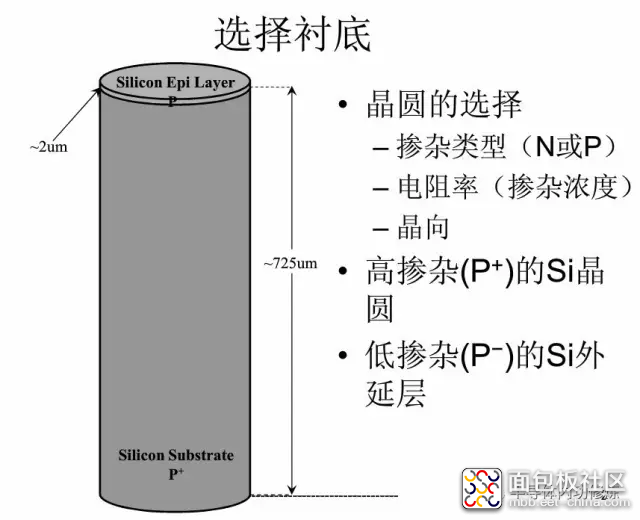

1.衬底选择:选择合适的衬底,或者外延片,本流程是带外延的衬底;

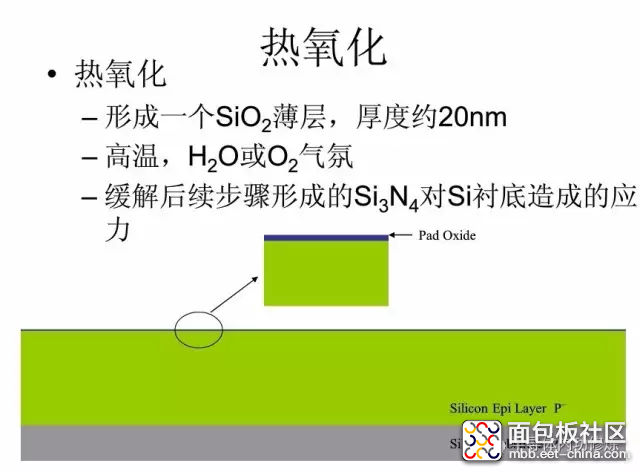

2. 开始:Pad oxide氧化,如果直接淀积氮化硅,氮化硅对衬底应力过大,容易出问题;

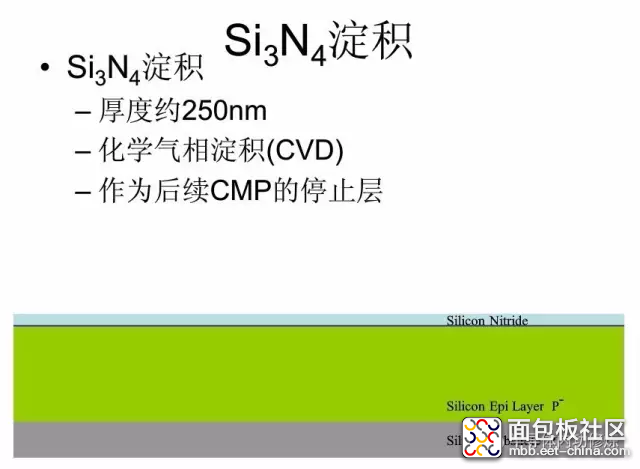

接着就淀积氮化硅。

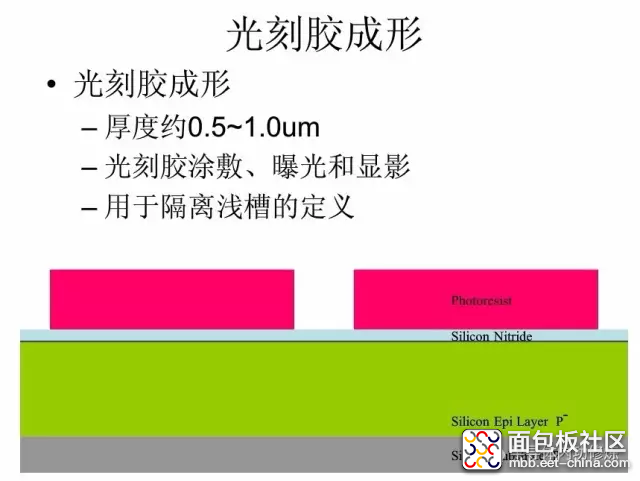

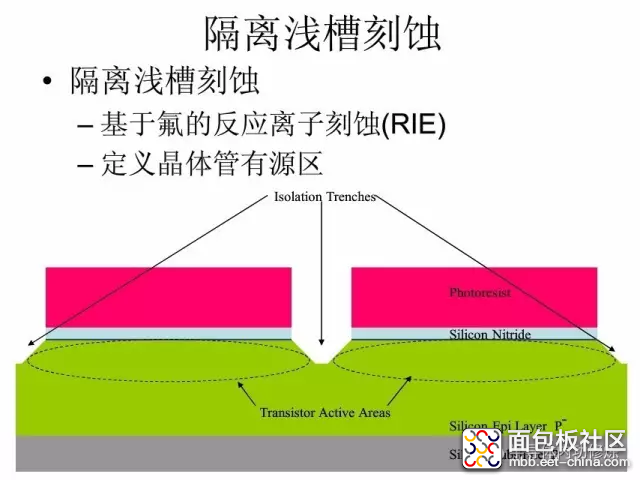

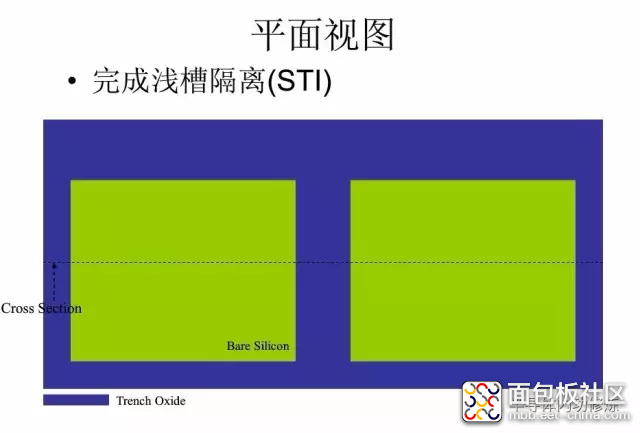

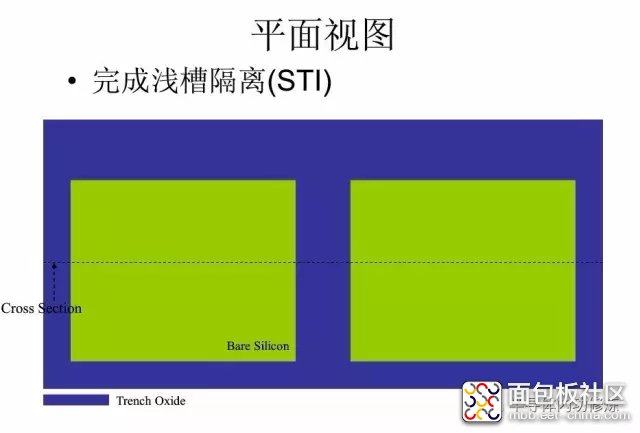

3. A-A层的光刻:STI(浅层隔离)

(1)A-A隔离区刻蚀:先将hard mask氮化硅和oxide一起刻掉;

(2)STI槽刻蚀:Si3N4的刻蚀菜单刻蚀硅速率过快,不好控制,需要分开刻蚀;

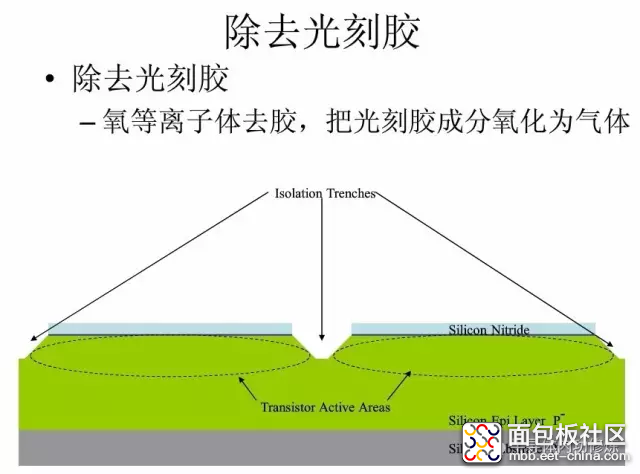

(3)刻蚀完成后去胶,为了节省空间,后面的层次去胶将会用一句话带过;

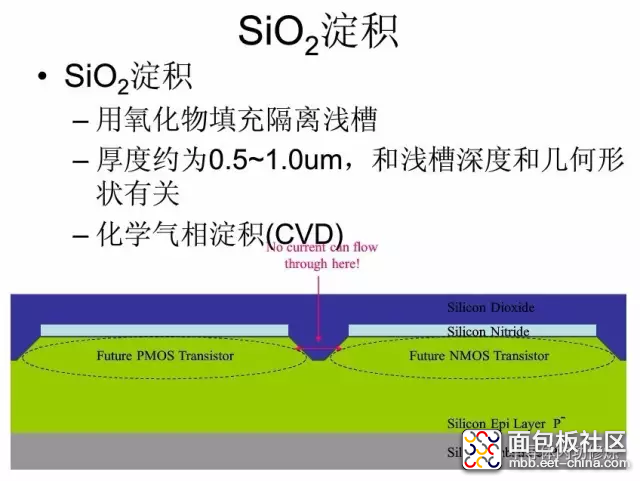

(4)STI用氧化硅填充:这里没有讲,其实刻蚀STI会对衬底造成损伤,一般要先长一层薄氧化层,然后再腐蚀掉的,这样可以消除表现损伤;

STI填充:HDP高密度等离子淀积STI槽,用其他机器填充会提前将STI槽封死,里面会出现空洞,HDP机台是一遍淀积,一遍刻蚀,可以防止提前封口;

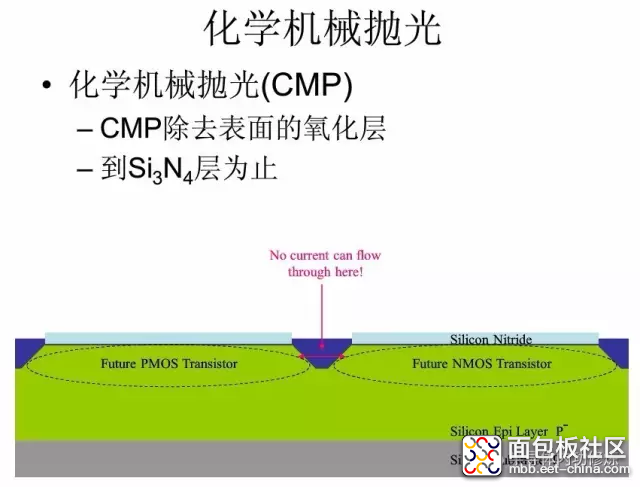

(5)简单的做法是直接CMP将二氧化硅磨平,但一般该步骤直接CMP会造成STI表面下陷,STI槽不满的情况,一般还会再加一层,将STI区域保护起来,将中间区域刻蚀掉,然后再CMP,这里简化处理。

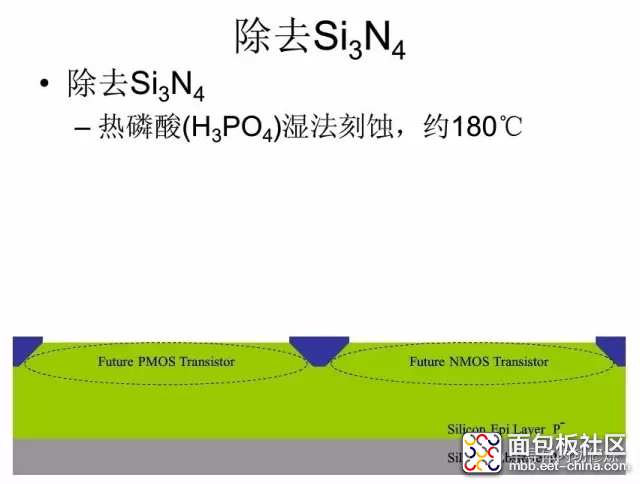

(6)热磷酸腐蚀掉氮化硅,这个不叫常规;

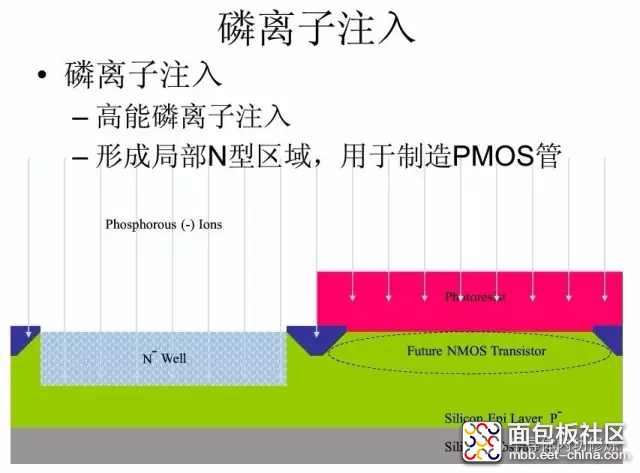

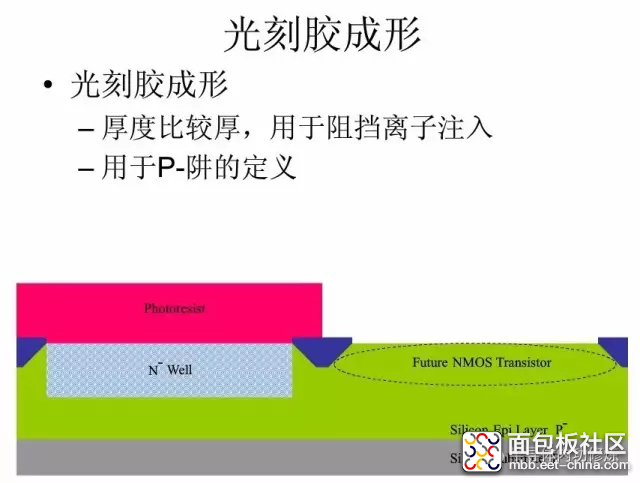

4. Nwell光刻、注入:光刻前都有一层pad oxide,这里也没有画。

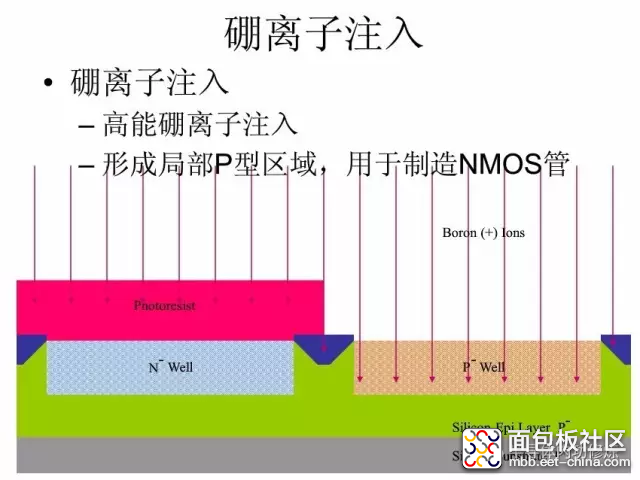

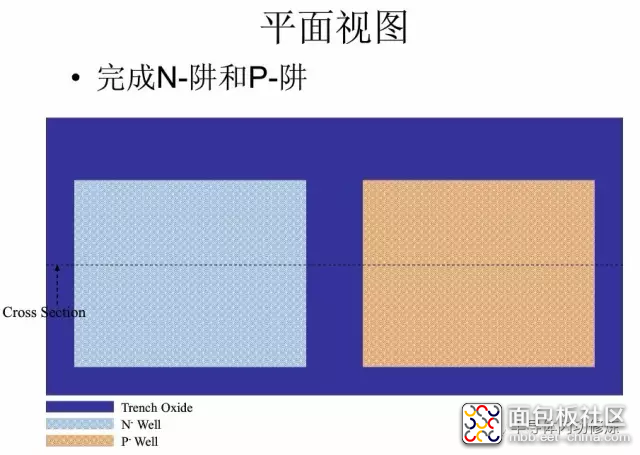

Nwell注入:一般要注一个阱,一个防传统注入,一个VT调节注入,三次注入分别对应深,中,浅,注入玩去胶,准备做Pwell注入;

5. Pwell光刻、注入:方式与Nwell类似,注入改为B注入,然后去胶,去胶后要将Nwell和Pwell一起推进,使两者有一定的结深和浓度梯度;

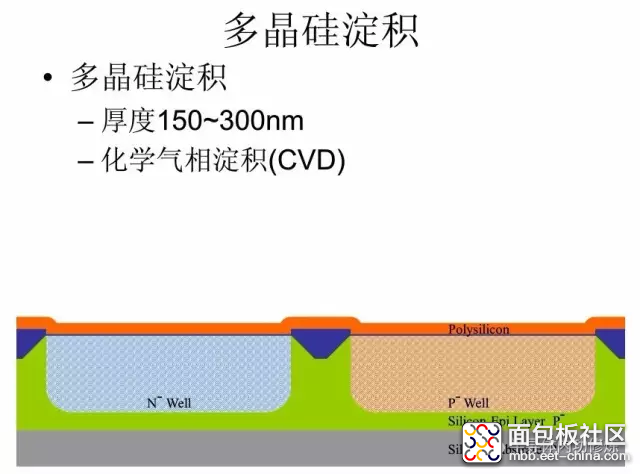

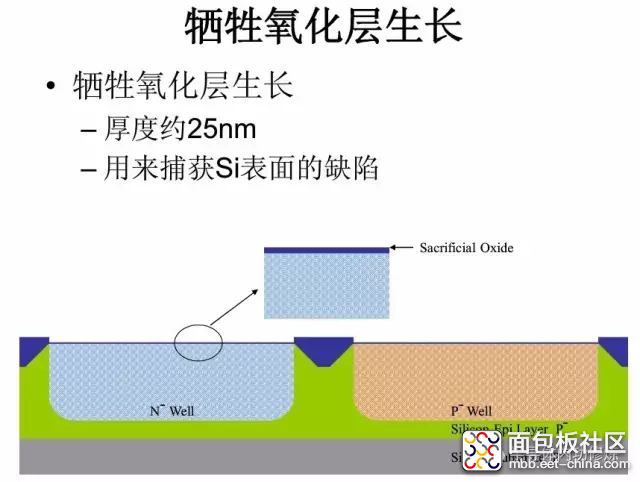

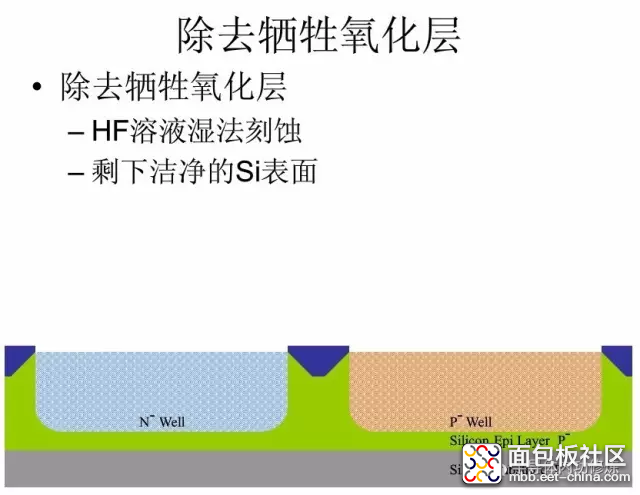

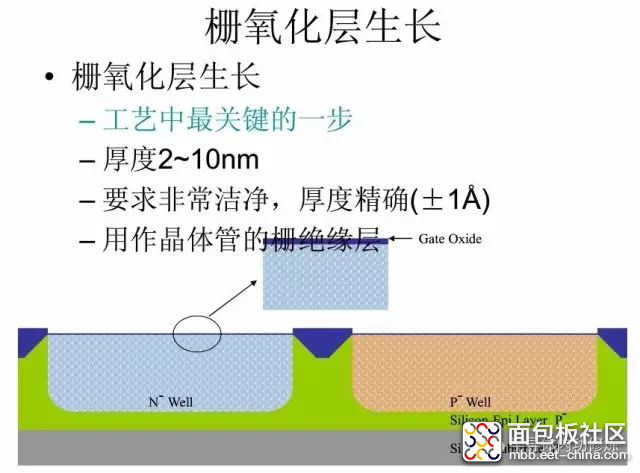

6. Gate栅的形成:腐蚀掉表现氧化层,再长一层牺牲氧化层,然后再腐蚀掉牺牲氧化层;

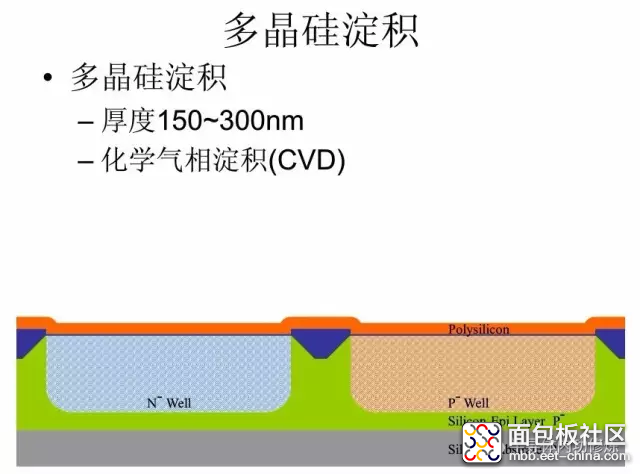

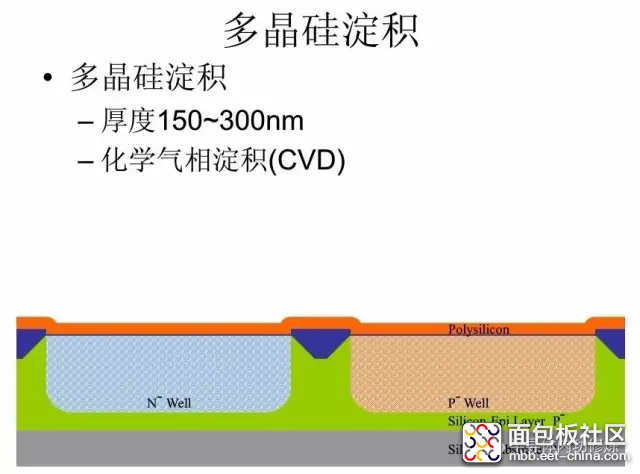

(2)POLY淀积:淀积 Insu-Poly,或者后面掺杂后再光刻

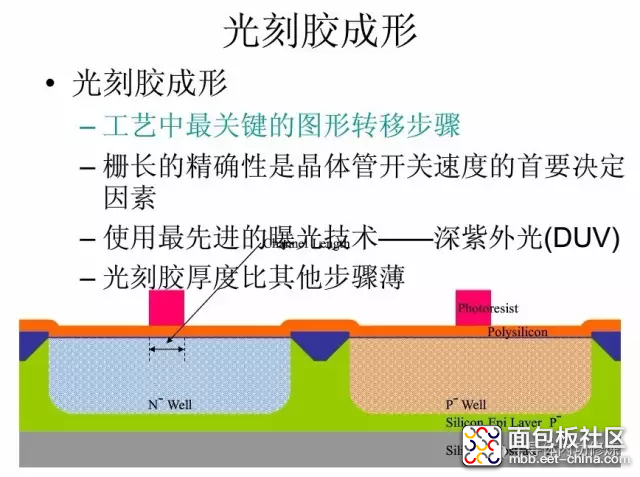

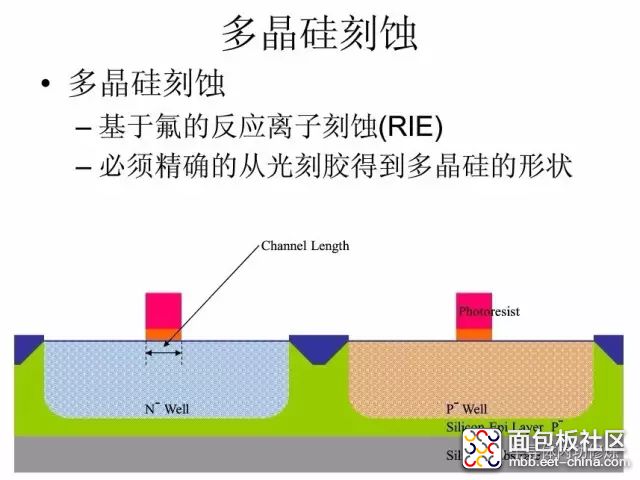

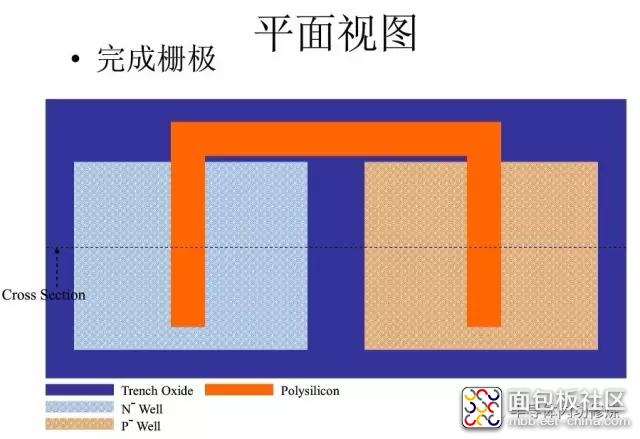

(3)POLY光刻、刻蚀:光刻Gate,并刻蚀POLY,然后去胶;

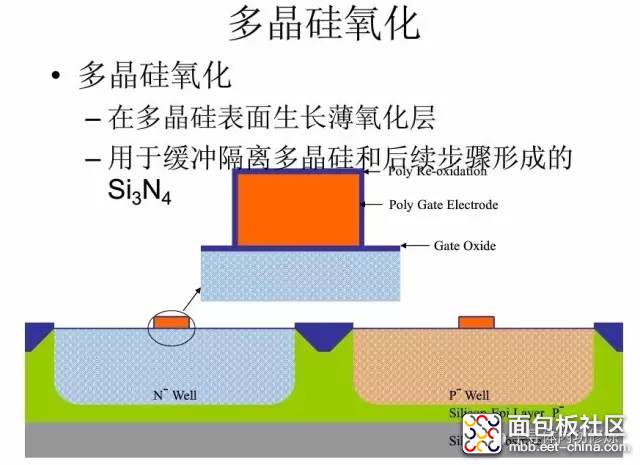

(4)POLY氧化:作为SI3N4 spacer刻蚀的停止层;

7. NLDD/PLDD的形成:

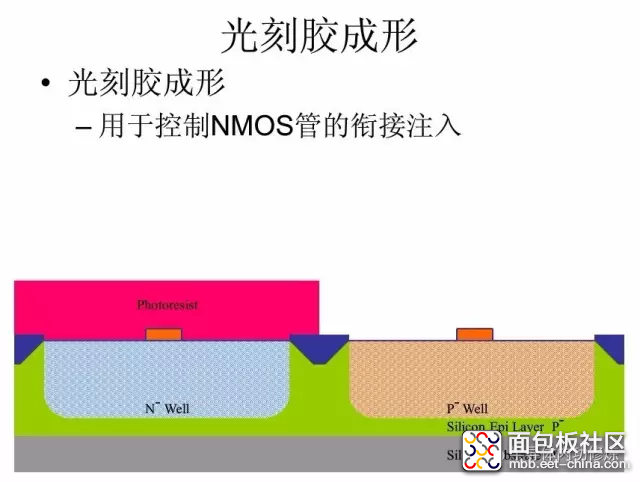

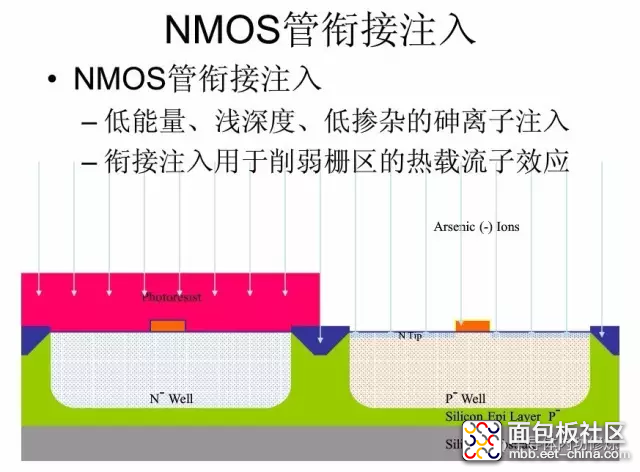

(1)NLDD光刻,注入,去胶;

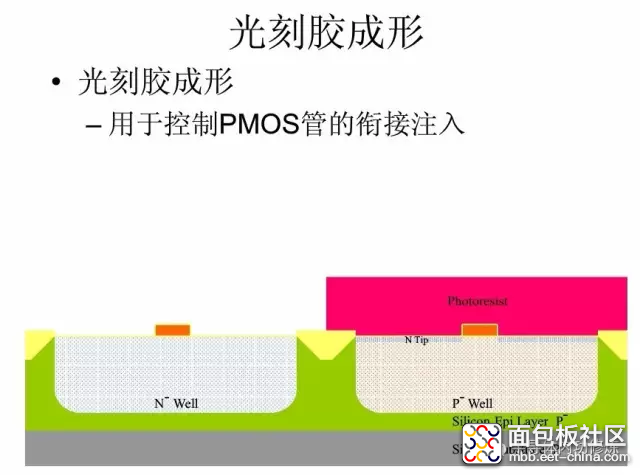

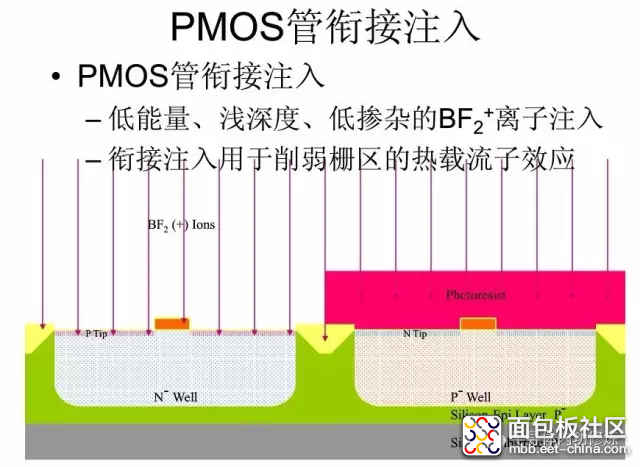

(2)PLDD光刻,注入,去胶;

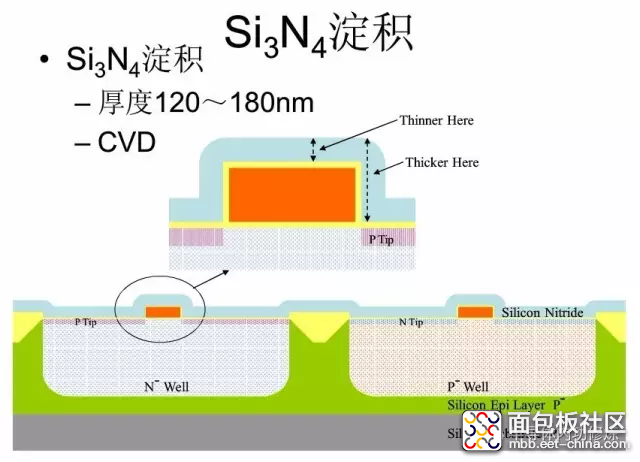

(3)Si3N4 spacer的刻蚀:氮化硅淀积及刻蚀

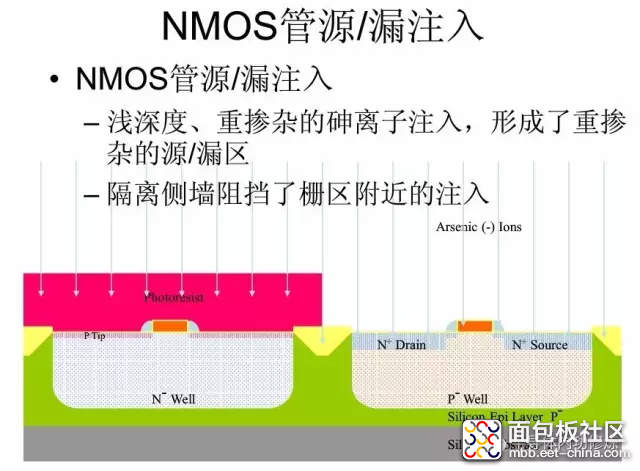

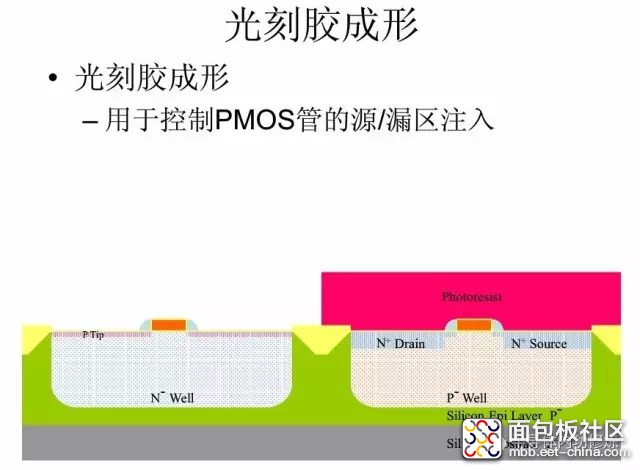

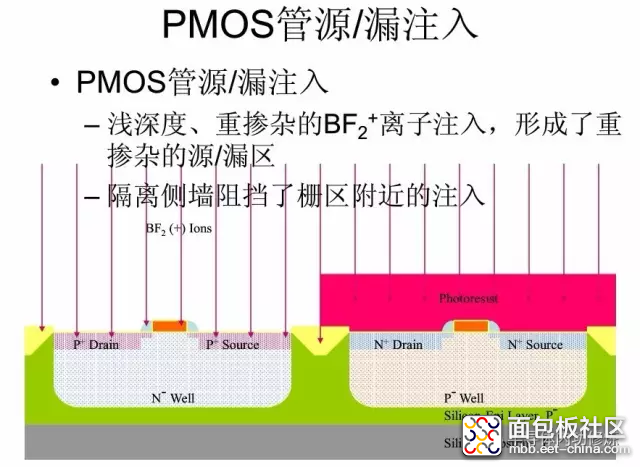

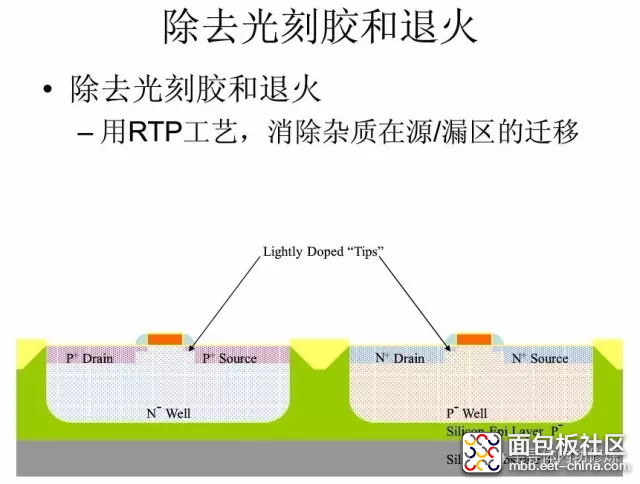

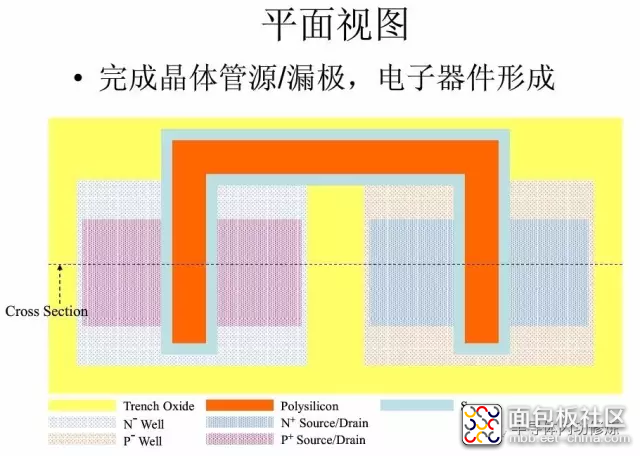

8. NSD/PSD形成:

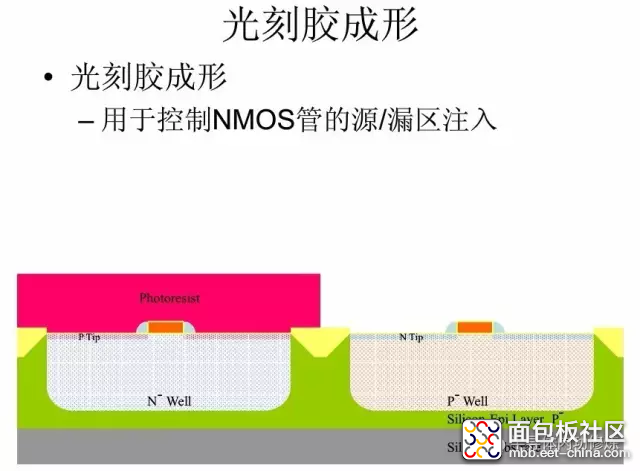

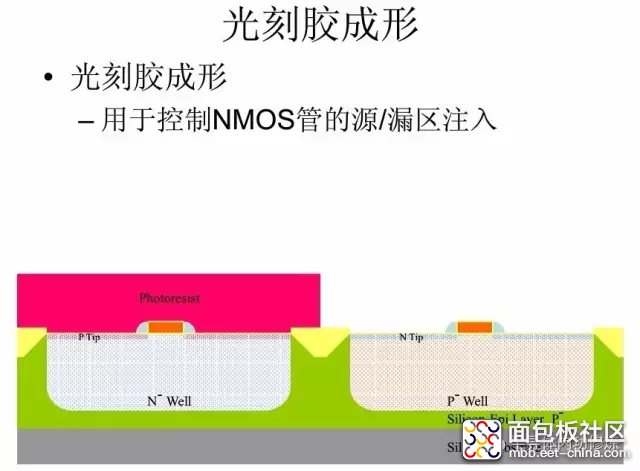

(1)NMOS的源漏注入:Si3N4 spacer挡住的区域NSD注入注不进去,因此NSD区域要离开gate一小段距离;

(2)PMOS源漏注入:做完PSD,一起做一次RTP来退回,激活离子。

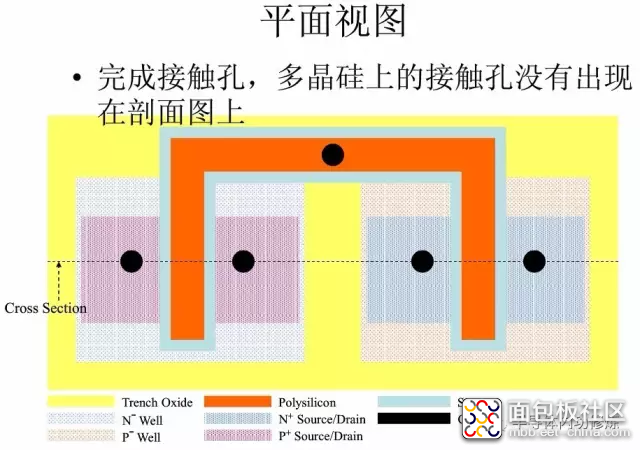

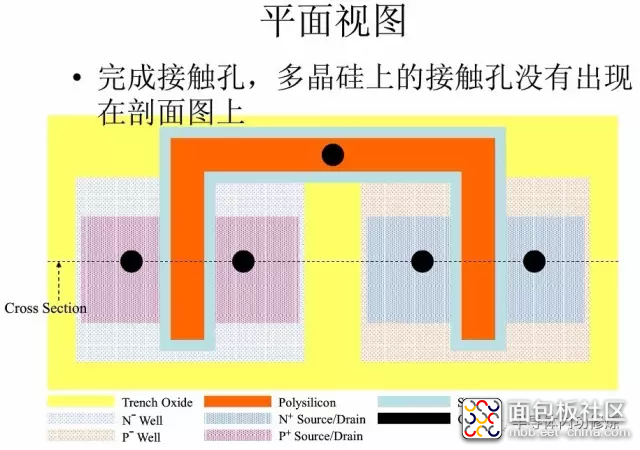

(2)contact孔光刻即刻蚀:

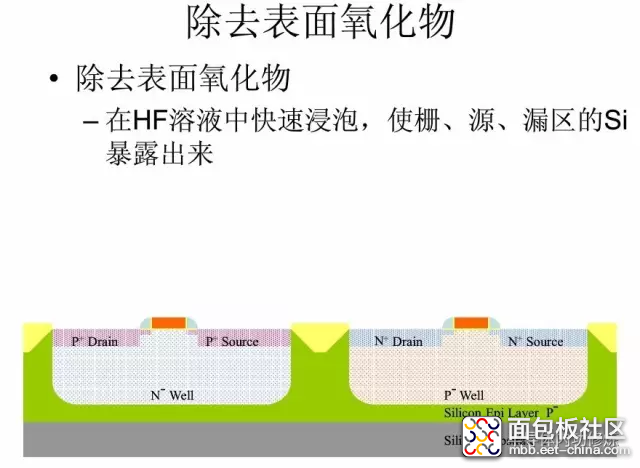

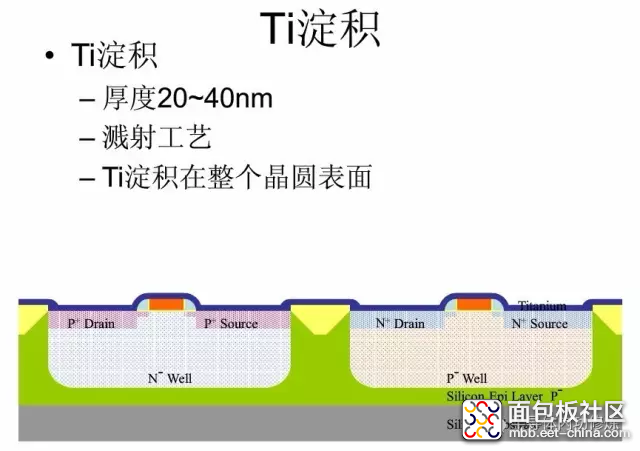

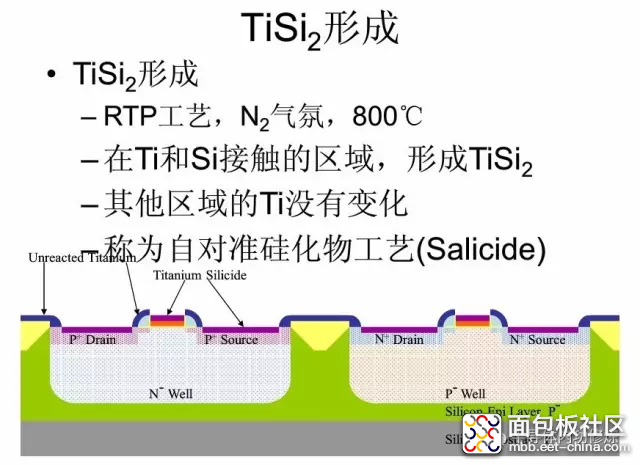

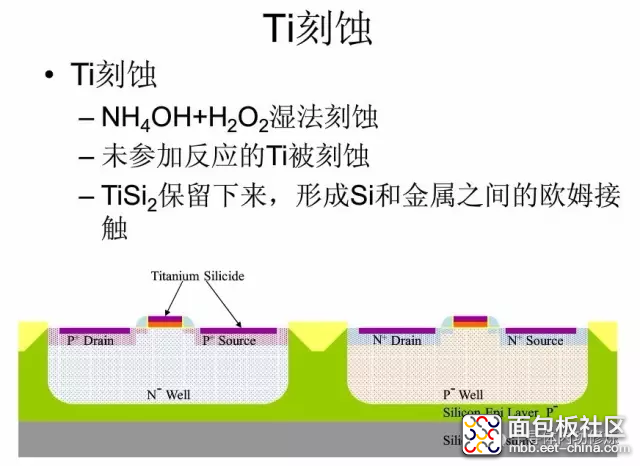

9. Salicide:Ti与硅形成低阻层Salicide;

(2)contact孔光刻即刻蚀:

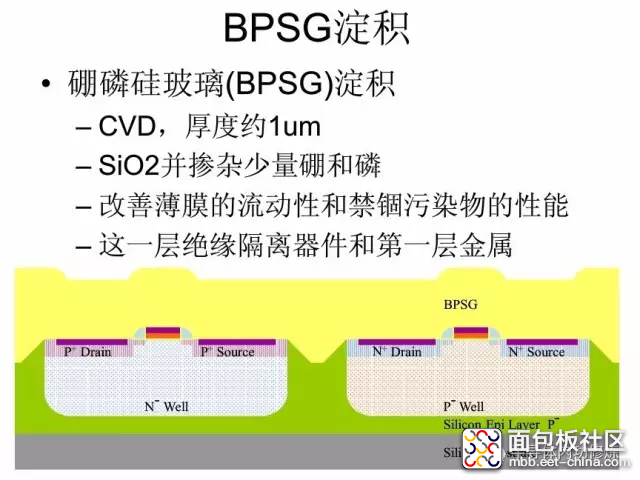

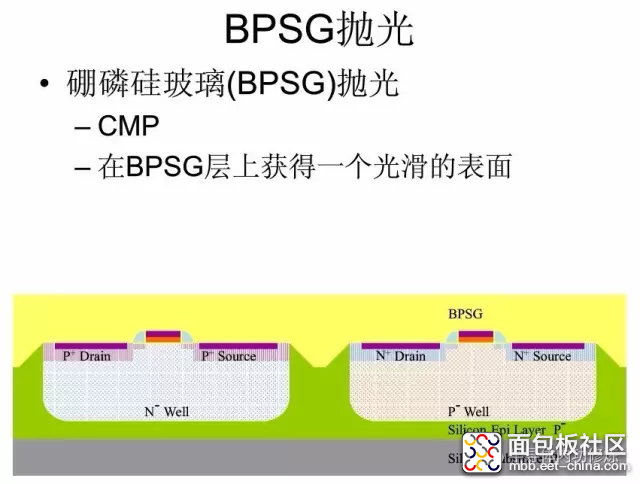

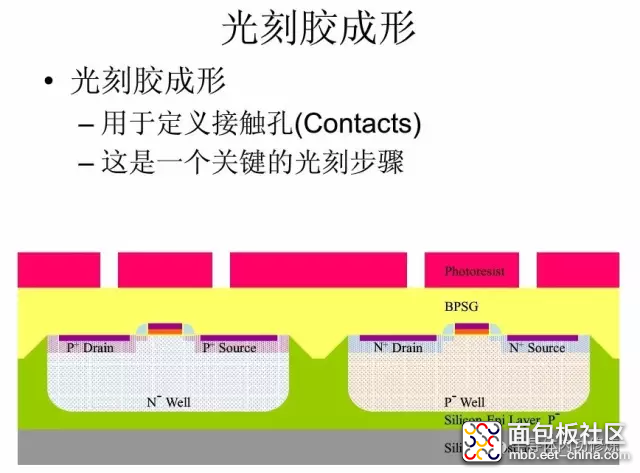

10.ILD淀积及contac形成:

(1)BPSG淀积及CMP抛光。

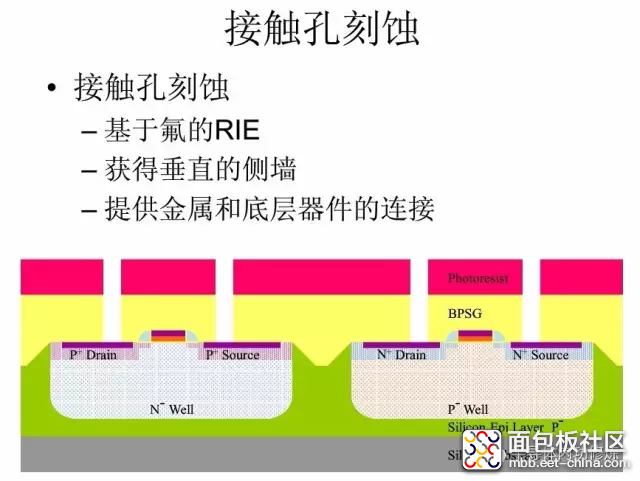

(2)contact孔光刻即刻蚀:

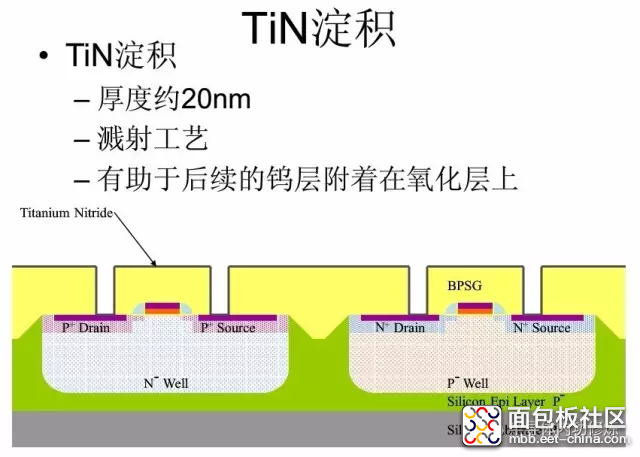

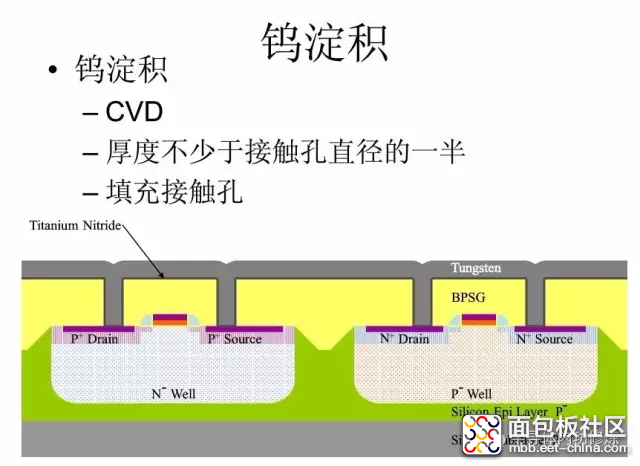

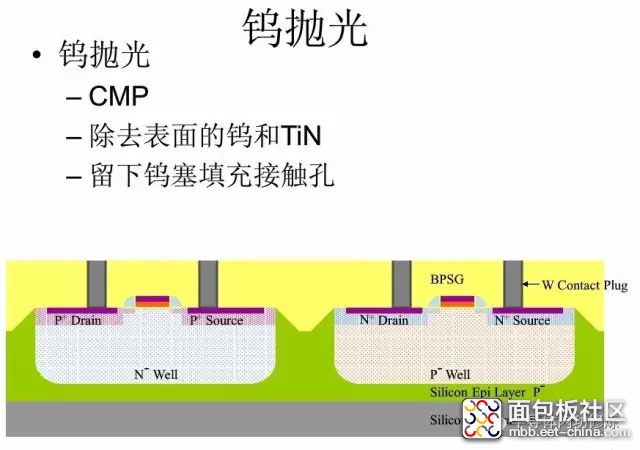

W-plug:W塞淀积及CMP。

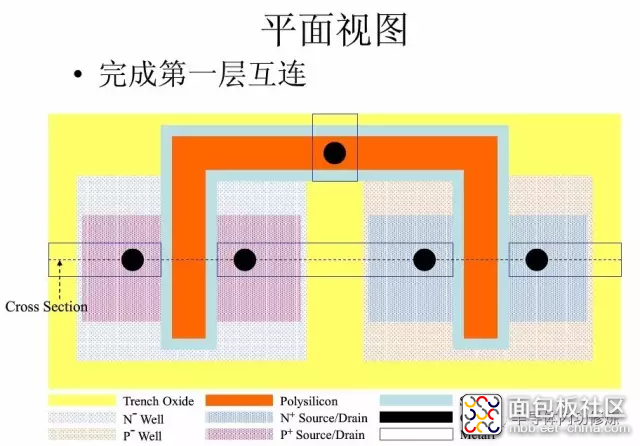

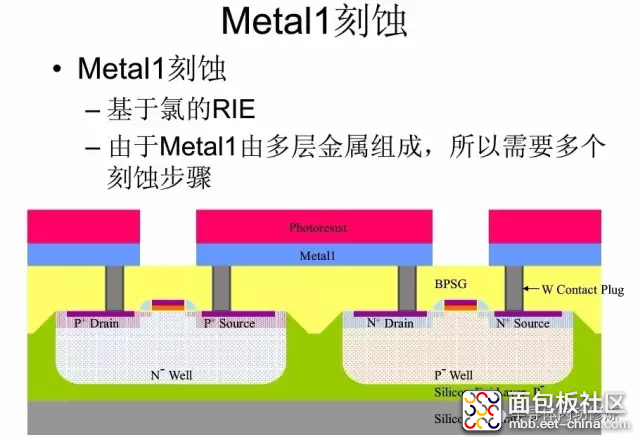

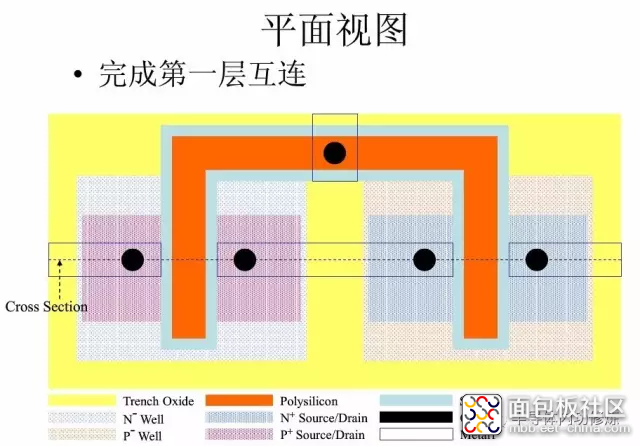

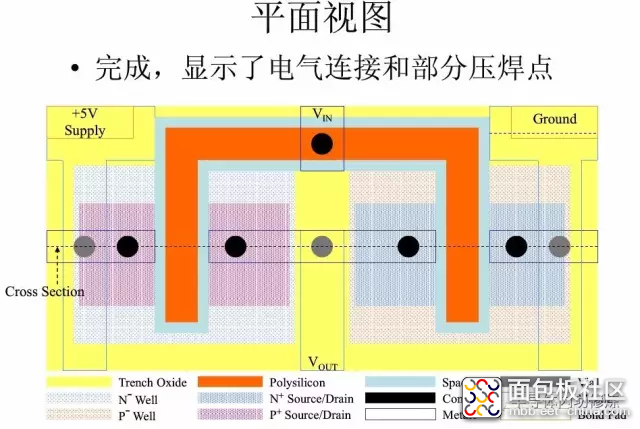

11. Metal-1淀积及光刻,刻蚀:

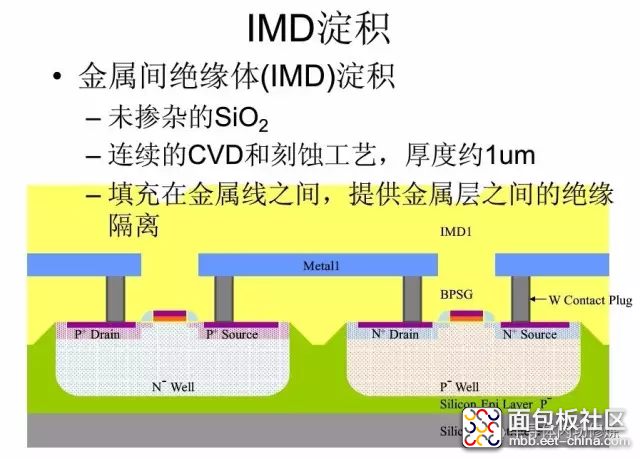

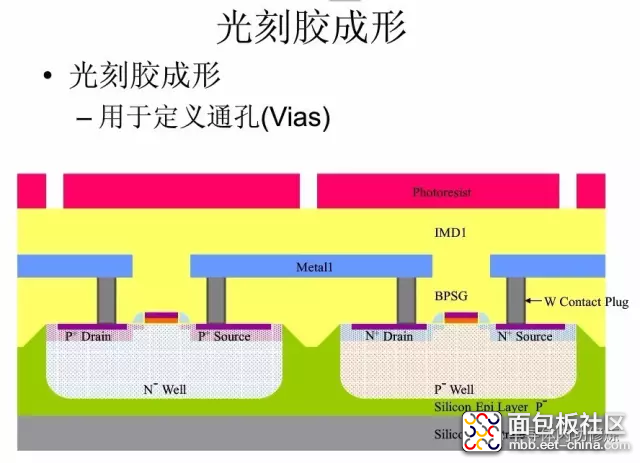

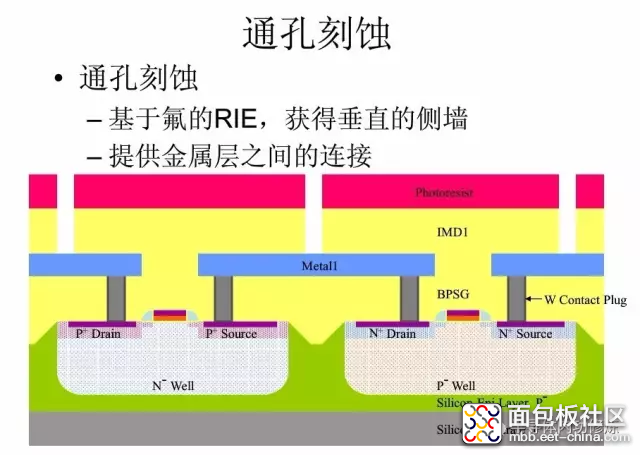

12. IMD淀积, CMP及Via光刻、刻蚀:

(1)IMD淀积,CMP抛光:

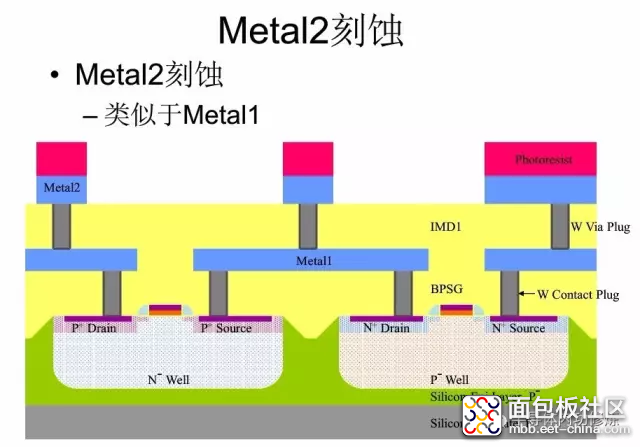

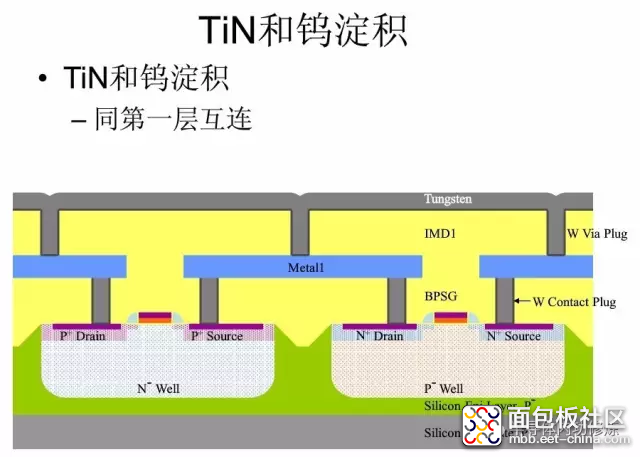

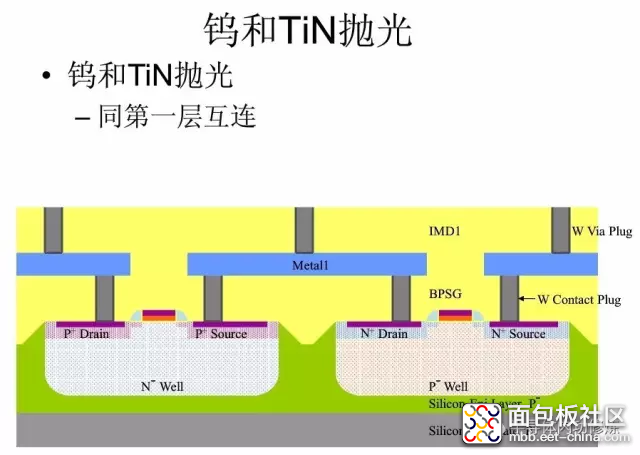

13. Via-W plug淀积,CMP:基本与Conctact W-plug一样的做法;

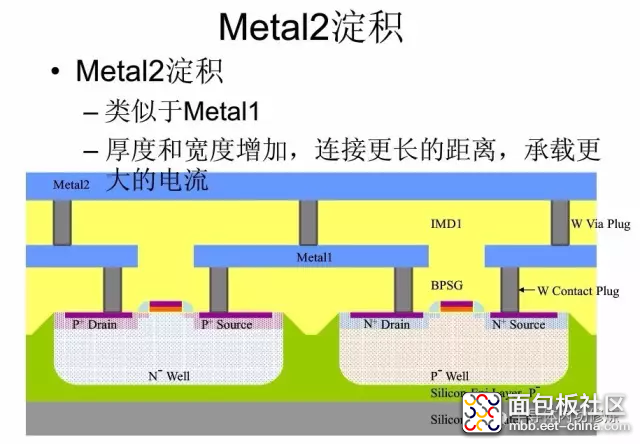

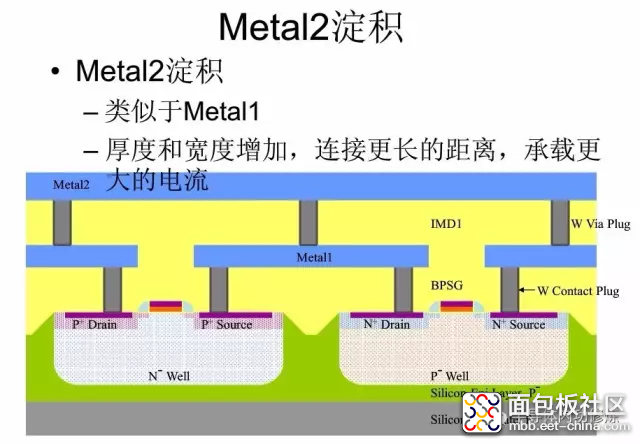

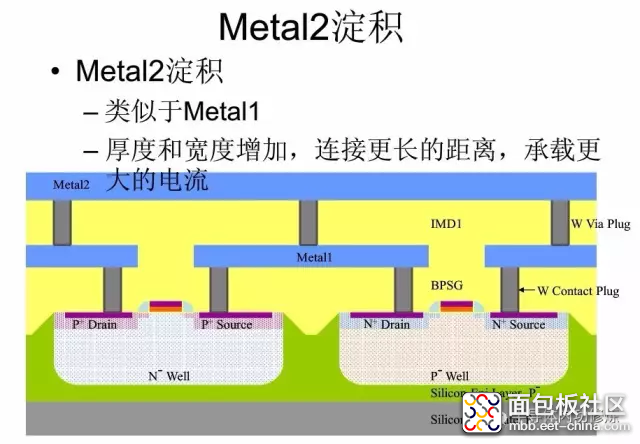

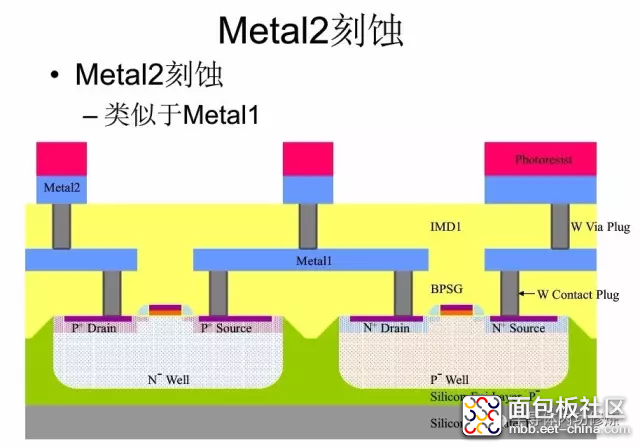

(1)Metal-2淀积:

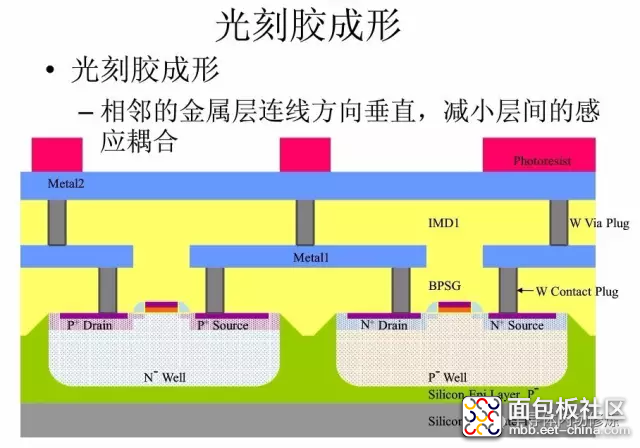

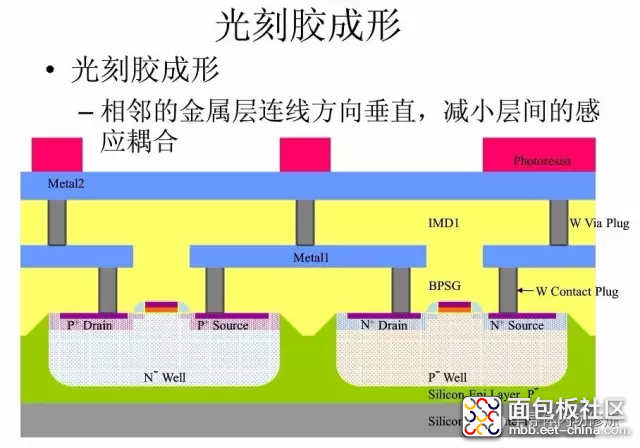

(2)Metal-2光刻刻蚀

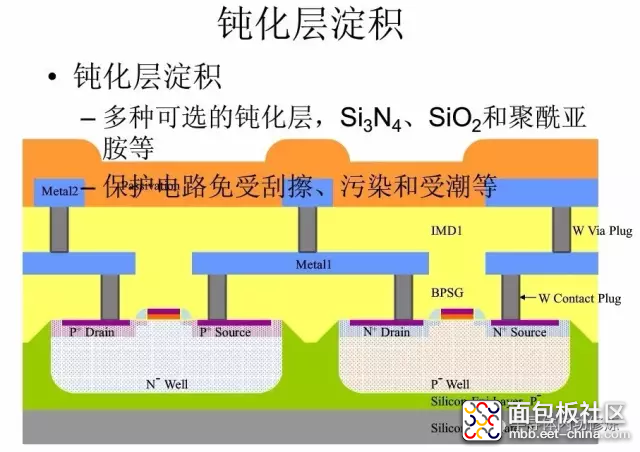

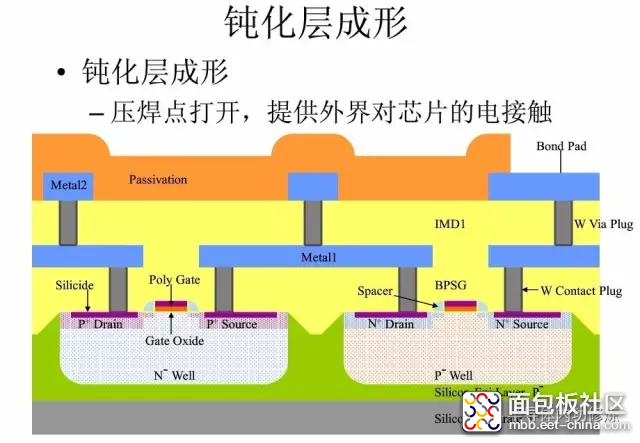

15. 钝化层淀积及钝化层光刻、刻蚀、去胶:钝化刻蚀后一般要做一步alloy。

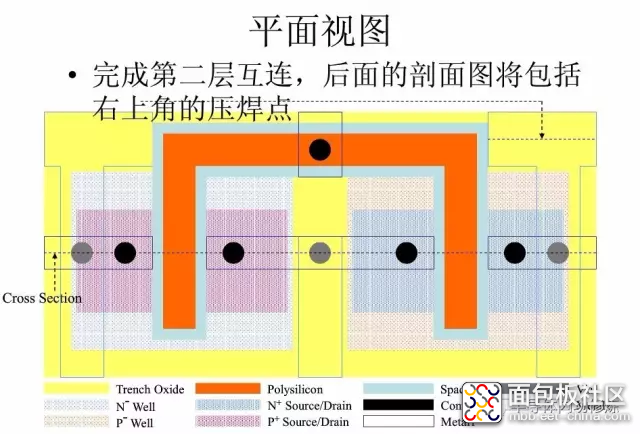

对于高级一点的工艺,可能会有更多层的metal,做法类似,继续Via和Metal的堆叠即可。

会有更多层的metal,做法类似,继续Via和Metal的堆叠即可。

内容转载自网络,仅供学习交流使用,如有侵权,请联系删除。

/4

/4