物理层位于OSI最底层,物理层协议定义电气信号、线的状态、时钟要求、数据编码和数据传输用的连接器。 物理层的器件称为PHY。

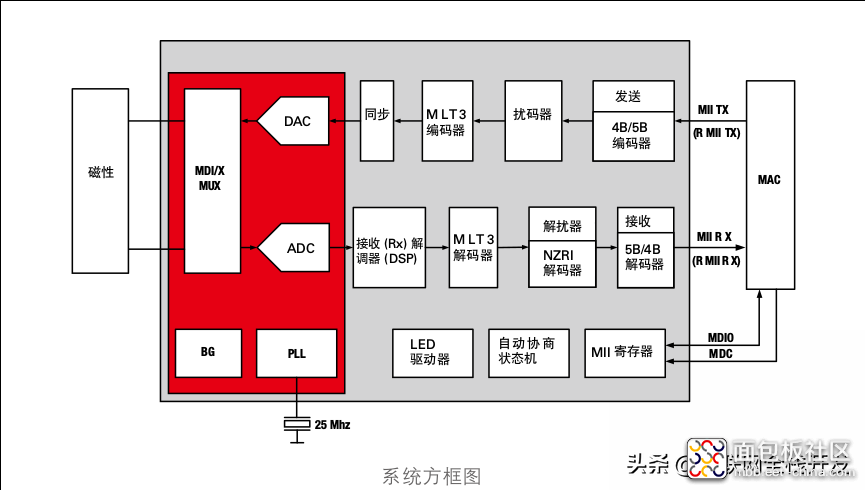

PHY芯片内部框图

上图里的灰色方框图里的就是PHY芯片内部模块图。 MAC器件通过MII接口来与PHY进行数据交换。 从图中可以看到向外发送数据和从外部接收数据时PHY所要做的一些工作。 可以简单理解成:

向外部发送数据时, MAC通过MII向PHY传送数据, 这些数据通过编码等处理, 最后再转成模拟信号发送出去。

从外部接收数据时,模拟信号先转成数字信号,再经过解码得到数据, 经过MII送到MAC。

PHY与MAC的通迅接口PHY与MAC的通过MII(Media Independ Interface)来通迅, 其工作内容包括:

数据接口, 有RX/TX两条独立的通道。

管理接口, 由时钟信号和数据信号组成, 可以用来控制和监视PHY的工作。

在MII的基础上, 后来又有了:

RMII(Reduced Media Independant Interface), 简化了MII, 比MII用的信号线更少。

GMII(Gigabit Media Independent Interface), 即先兆的MII接口

RGMII (Reduced Gigabit Media Independent Interface)

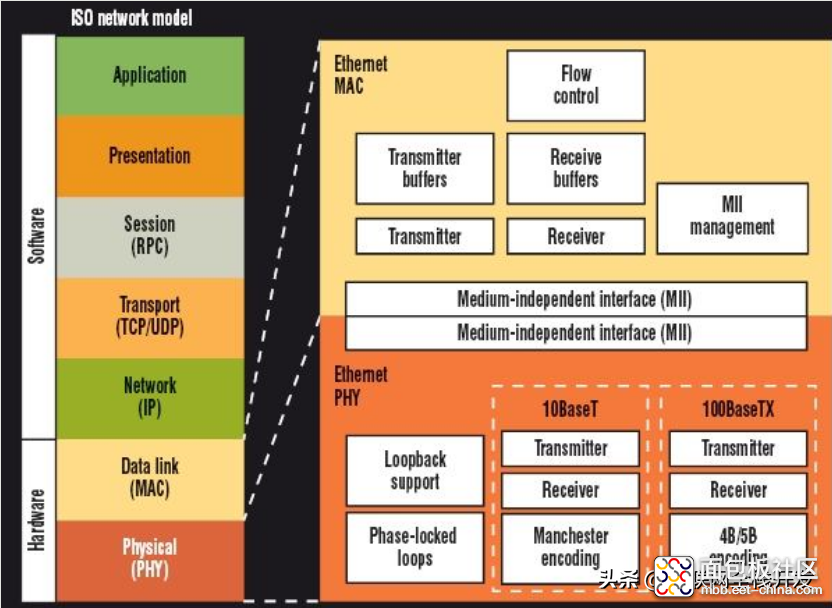

iso7层模型

PHY与RJ45的连接

PHY上有大量模拟器件, MAC是全数字器件, 现在的IC技术已经可以将PHY和MAC集成在单芯片内。

在外部, PHY外部连接RJ45接口, 通常在PHY和RJ45之间放置一个1:1的隔离变压器(Transformer)作为绝缘模块, 有几个考虑:

- 芯片工作时产生的信号传送到很远的地方会有较大的直流分量损失

- 如果PHY和RJ45直连, 电磁感应和静电很容易造成芯片损坏

- 电网环境不同造成连接两端的0V电平不一致, 导致很大的电流会从电势高的设备流向电势低的设备。

作为以太网设备的一部分,MAC是数据链路层的一个子层。 MAC负责执行带冲突检测的载波侦听多路访问协议, 即CSMA/CD协议。 它完成以下功能:

- 把数据封装成帧, 包括对帧进行界定, 实现帧同步

- 对目的MAC地址和源MAC地址进行处理

- 在与PHY发生传输错误时对帧进行处理。

- 对PHY进行控制

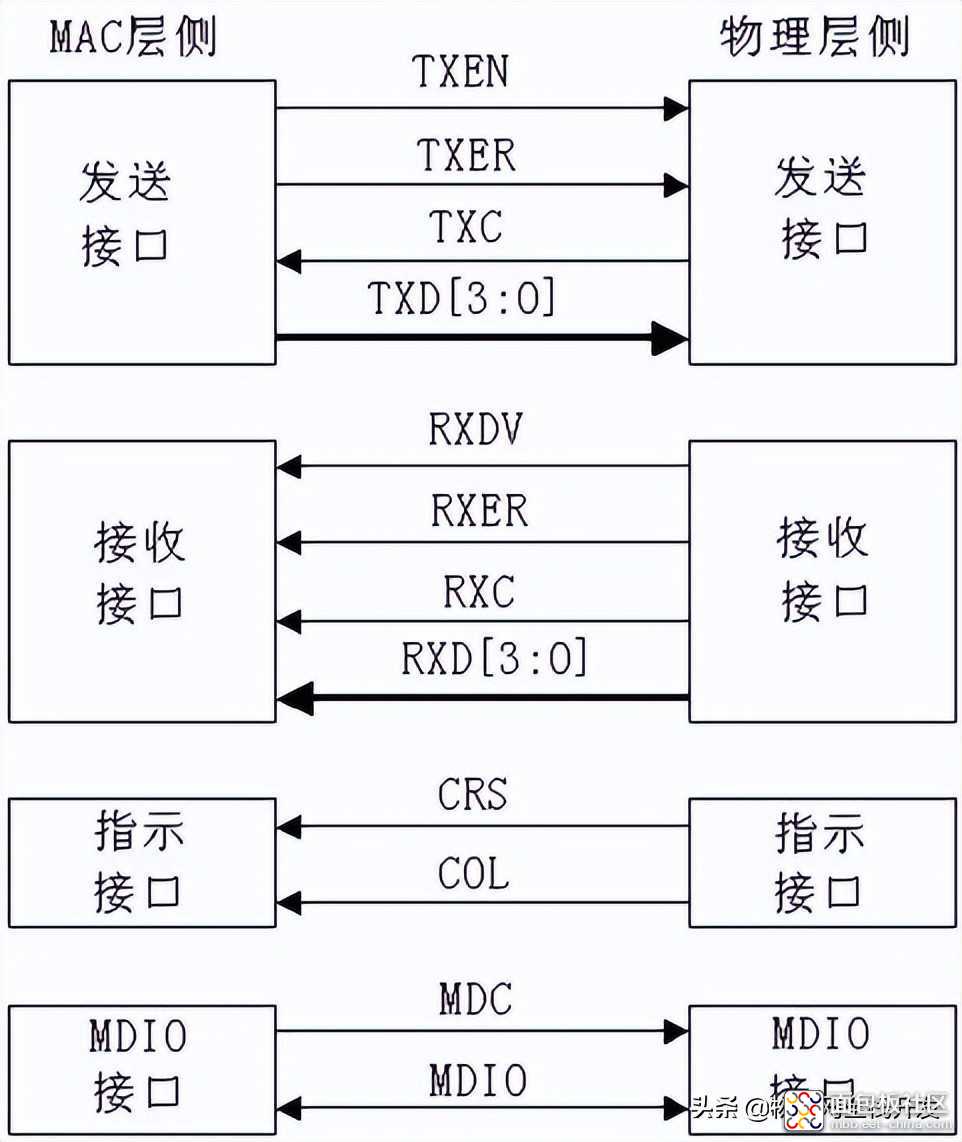

MII接口有18个信号线,所有信号名称都是从MAC层侧说明的,主要包括四个部分。

一是从MAC层到物理层的发送数据接口,

二是从MAC层到物理层的接收数据接口,

三是物理层与MAC层之间状态指示接口,

四是MAC层和物理层之间数据管理的MDIO/MDC接口。

MII接口的定义如图1所示:

MII接口定义

发送时钟(TX-CLK)

发送时钟是由PHY芯片提供并传递给MAC层的一个连接时钟信号。

TX-CLK信号向协调子层提供了一个参考时钟,协调子层将与该时钟信号同步驱动TXD,TX-EN和TX-ER信号,以进行数据发送和状态控制。

TX-CLK工作于25MHz(对于100Mb/s网络操作)。

发送数据(TXD[3:0])

这一组四个引脚用来传递MAC层芯片的半位元组(4位)发送数据,该数据在发送前将被位于介质上的PHY层芯片进行适当的编码。

当TX-EN不活动时RS给出的半位元组数据将被忽略。

发送使能(TX-EN)

该信号由MAC层芯片给出,用来表明TXD引脚上给出了有效数据,且应用PHY层芯片将其向网络介质上进行发送。

发送错误(TX-ER)

该信号由MAC层芯片给出,用来向PHY层芯片表明所收到的信号流中有编码错误。

在TX-EN处于活动状态的时候,如果TX-ER信号在一个或多个TX-CLK周期内处于活动状态,PHY将负责通过生成一个既不是正常数据也不是定界符信息的任意编码,来在介质上生成一个无效的发送帧。

发送帧中错误的相对位置不需要保留。其目的是为了保证接收方的PHY总可以检测到帧中有错误。

接收时钟(RX-CLK)

接收时钟是由PHY层芯片提供并向MAC层芯片传送的一个连接时钟信号。

RX-CLK信号向PHY层芯片提供了一个参考时钟,PHY芯片用它来同步驱动RXD,RX_DV和RX_ER信号,以向协调子层回送从介质上译码得到的接收数据和/或状态信息。

RX_CLK工作于25MHz(对于100Mb/s)或2.5MHz(对于10Mb/s)。该时钟是由PHY芯片从到来的数据流中恢复出来的。

接收数据(RXD[3:0])

这一组四个引脚用于向MAC层芯片传送PHY芯片从介质上译码得到的接收半位元组数据。当RX_EN不活动时给RS的半位元组数据将被忽略。

接收数据有效(RX_DV)

该信号由PHY给出,用于向MAC表明RXD引脚上给出了从介质上译码得到的有效数据。RX_DV必须在第一个SFD半位元组之前给出,且必须在接收帧CRC的最后一个半位元组之后立即撤销(在RX_CLK的下一个上升沿之前)。

接收错误(RX_ER)

该信号由PHY给出,用于向MAC表明在PHY从介质上接收到的数据中检测到了一个编码错误。它可能是一个非法编码或者是其它PHY可以检测到的错误,

这些错误不可能被MAC层芯片检测到。在RX_DV处于活动状态的时候,如果RX_ER信号在一个或多个RX_CLK周期内保持活动,则PHY向RS表明在当前接收帧的某处检测到了一个错误。

当给出RX_ER信号且RX_DV处于不活动状态时,RXD[3:0]引脚的值表明是出现了错误载波事件还是一个正常的包间间隔情况。

错误载波事件是一种由特定介质的PHY检测到的错误,通常情况下是指在介质上检测到了一个错误的帧头。接收帧中错误的相对位置将不被保留。

其目的是为了保证接收方的RS/MAC总可以检测到帧中包含的错误。

MAC上的MII实现应当在对帧进行重发时用RX_ER指示来驱动TX_ER,否则就需要其他方法来保证远端的接收器总能检测到在帧中包含的错误。一般情况下这出现在多端口中继器或交换机实现中,在其中实现了重发过程,来确保在通过MII向PHY传递之前生一个无效的传输帧。

载波侦听(CRS)

CRS由PHY给出,用于表明发送或接收介质处于活动状态,并且在发送和接收介质都空闲时撤销。应注意的是活动和空闲的定义是基于PHY是否检测到有效数据包。

对于某些特定的介质和相对应的PHY而言,即使是在没有数据包时介质上仍有信号(换句话说,帧间空隙有相应的特定信号)。

CRS要求在整个冲突期间给出。CRS和TX_CLK或RX_CLK没有同步关系。

上述是以太网工作于半双工模式的信号关系,在MII口工作于全双方式时不会有冲突也不必载波侦听,但为介绍知识的完整性在此加以简单说明。

冲突(COL)

冲突由PHY给出,用于表明在介质上检测到了冲突状态,并且在冲突情况持续保持不变。COL和TX_CLK或RX_CLK没有同步关系。

如前所述当MAC与PHY工作于全双工方式该信号状态变得无意义。

管理数据时钟(MDC)

该时钟由MAC层芯片输出,并用于通过MDIO引脚从PHY中同步输入和输出数据。

管理数据输入输出(MDIO)

这是一个可以向PHY设备输入输出串行数据的双向信号,需要在MII之上给出了一个管理实体,一般在MAC芯片中实现,由管理实体给出的控制和配置数据和MDC同步地在MDIO线上给出,并且被PHY同步采样。

由PHY给出状态信息,作为对管理实体读取管理寄存器请求的响应,和MDC同步地在MDIO线上给出,并且被管理实体同步采样。

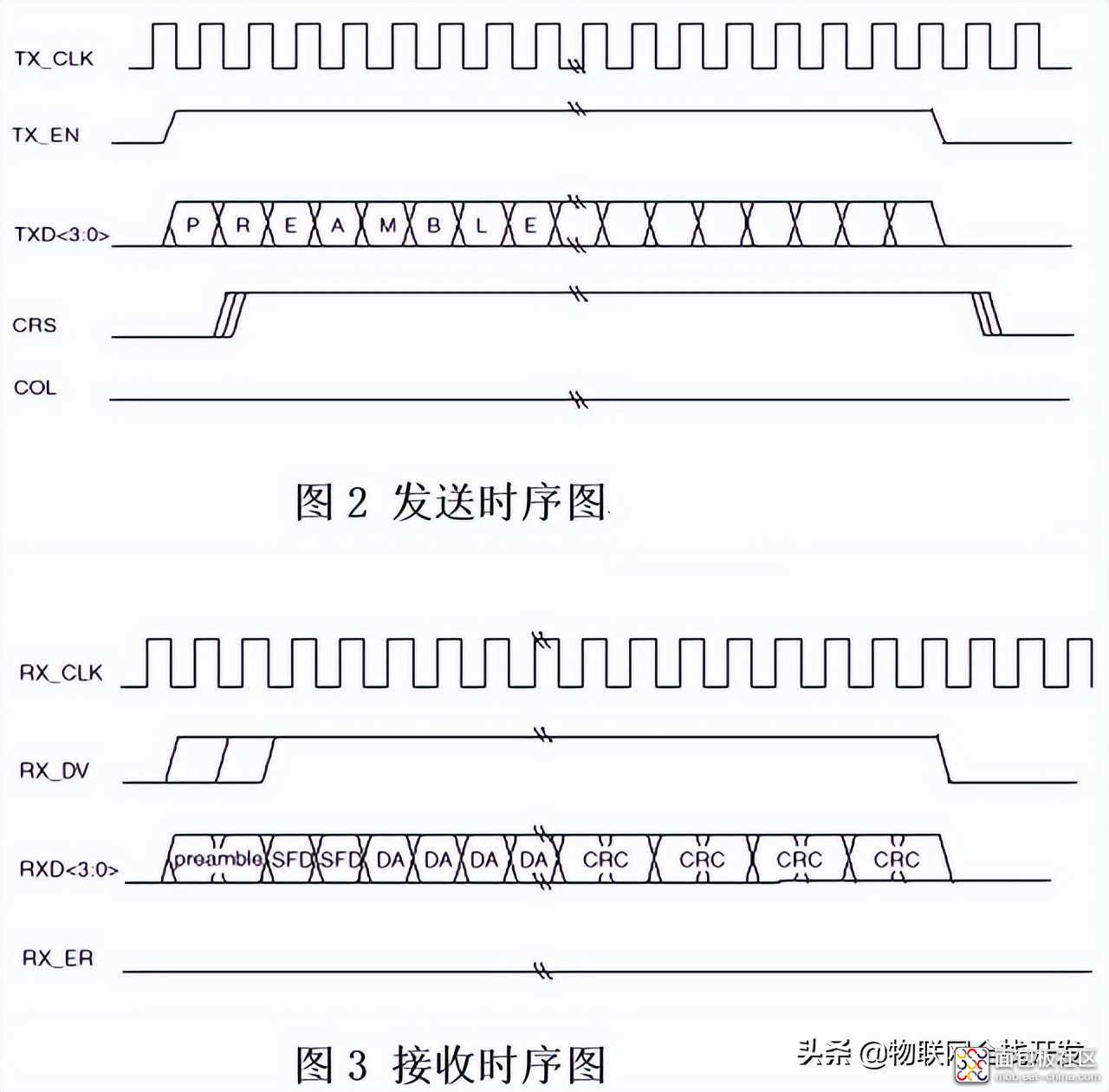

下面给出了简单的MII接口的时序图:

MII接口的时序图

来源:物联网全栈开发

/3

/3