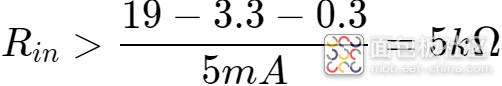

当经过运算放大器隔离之后的信号输入到STM32处理器的模拟输入口时,

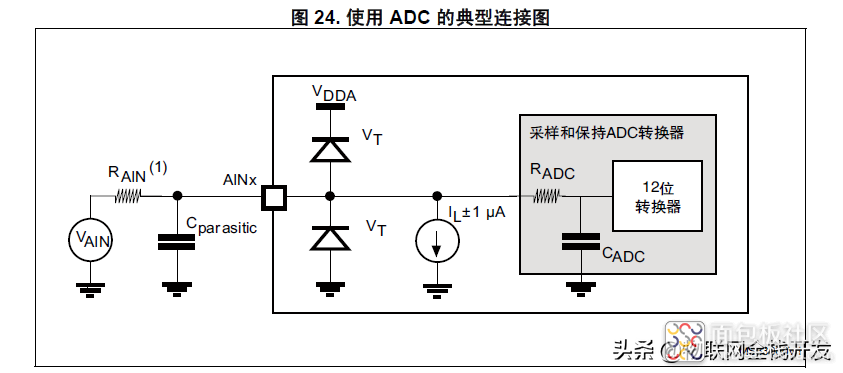

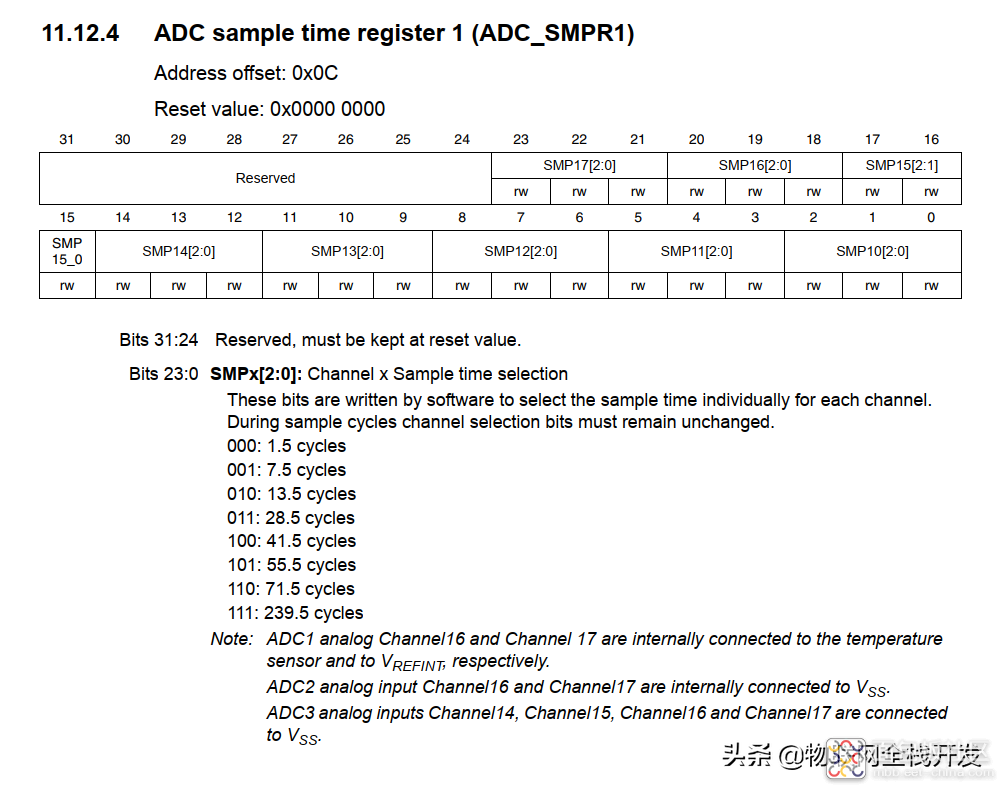

我们需要串联一个电阻,根据规格书的A/D转换电路框图所示,

图1.A/D转换电路框图闪

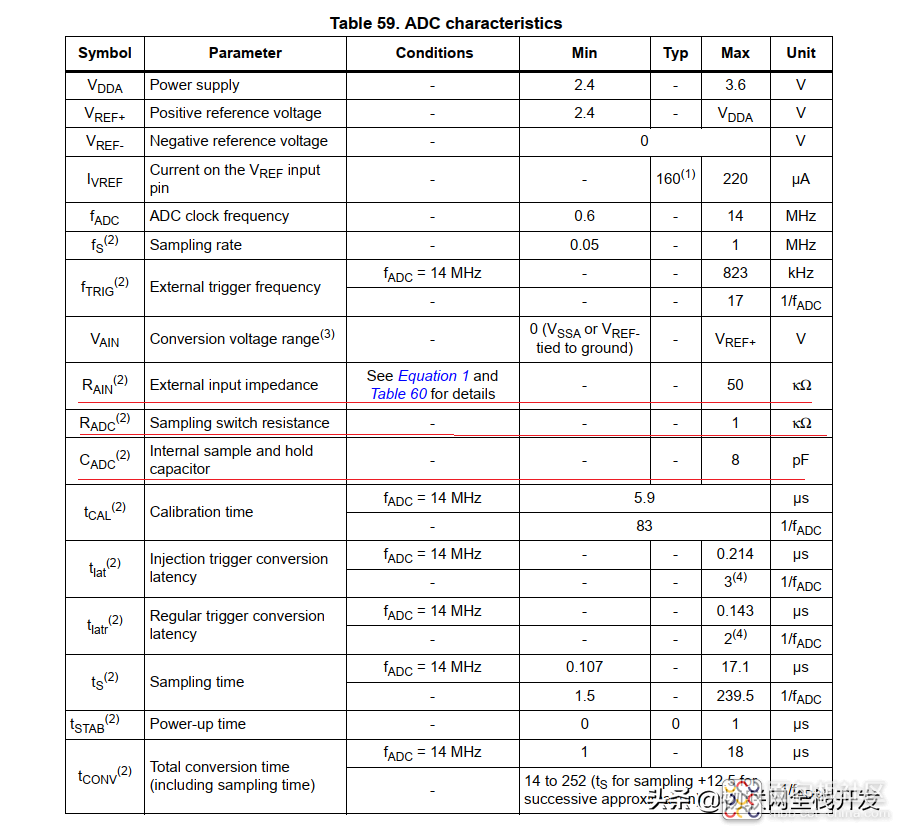

图中RAIN为外部输入电阻,最大值为50KΩ;

RADC为内部采样开关电阻,最大值为1KΩ;

CADC为内部采样和保持电容,最大值为8pF.

图2.ADC特性参数

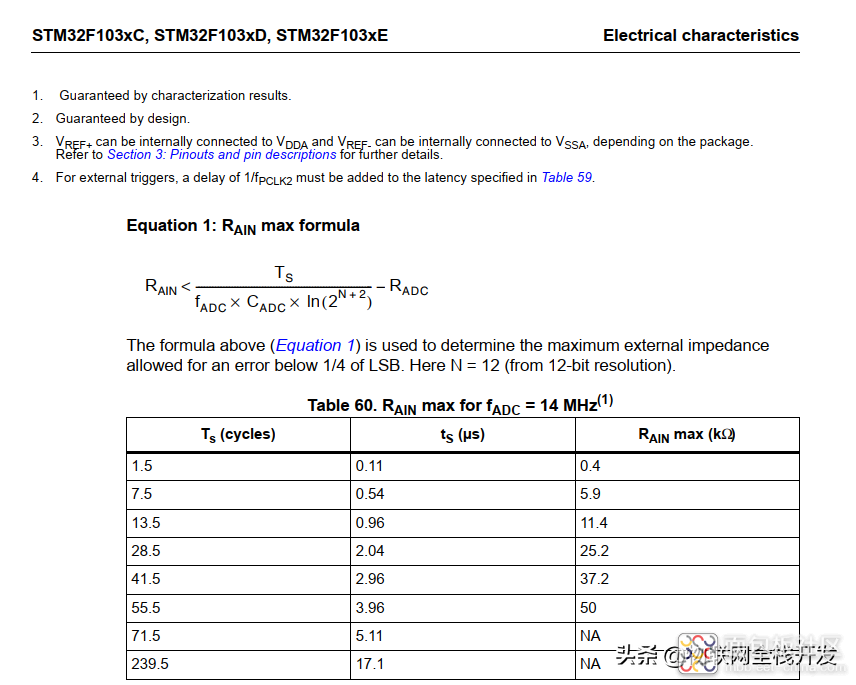

而外部输入电阻的取值与采样时间、采样保持电容有关,如下图:

图3. 外部电容最大取值与采样时间关系

这些取值背后有什么深层的逻辑,外部输入电阻RAIN起到什么作用,应当如何取值?

[size=1.059em]外部输入电阻的作用

[size=1.059em]

一、限流作用

根据图1所示的框图,处理器的模拟输入口内置了上、下拉的保护二极管。

我们所说的输入口阻抗高,是指输入电压在VSS以及VDDA之间时的一种情况。

有些人不求甚解,了解到这一特性,就盲目把外部输入电压或者运放输出的电压不经过任何电阻,直接连接至输入端口。

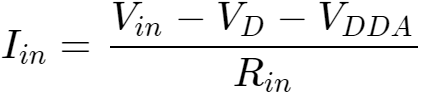

殊不知,这样会导致严重的后果,当输入电压超过处理器模拟电路电源VDDA与二极管导通电压之和时,内部的上拉二极管导通,假设输入电压为Vin, 外部输入电阻为Rin,

此时流过IO口的电流为:

当没有串联限流电阻时,Rin=0,此时流过IO的电流非常大。

会造成IO口的损坏,甚至导致VDDA的电源无法稳压,其输出电压被抬升,造成由其供电的其它器件损坏。

当电压低于0减去二极管导通电压时,下拉二极管可能出现同样的情况。

这种超出输入范围的电压,可能是外界的干扰导致,还有一种可能是用于调整信号的运放跟处理器的VDDA不是由同一个电源供电,而是有不同的上下电顺序。

比如运放先于VDDA供电,此时运放可能输出高电压,而VDDA还没有电压,运放输出通过内部二极管流入VDDA,出现上述分析的情况。

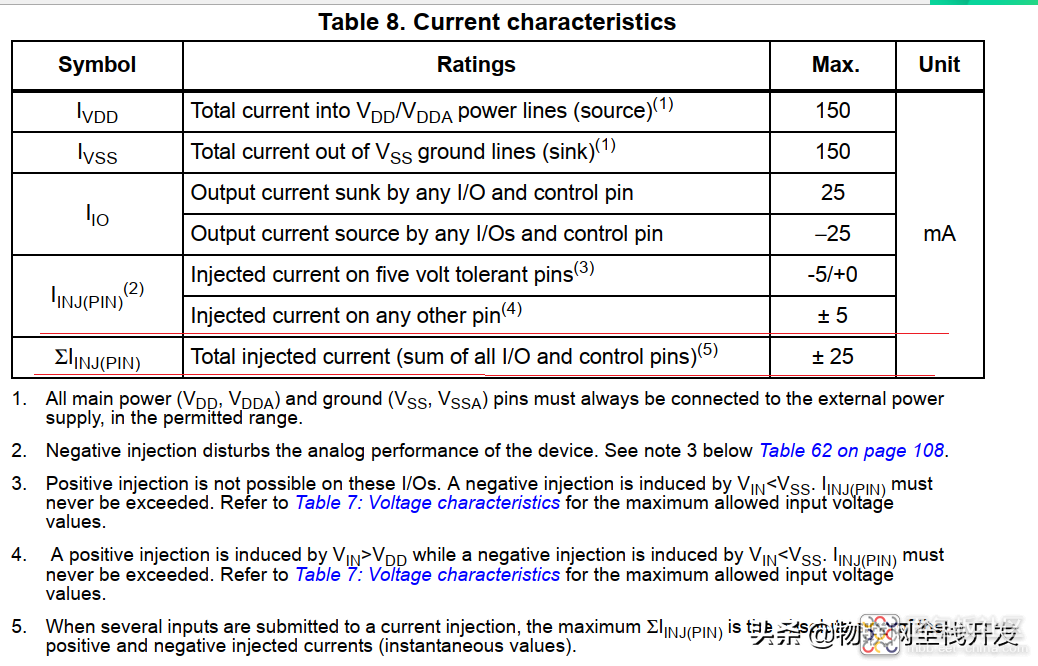

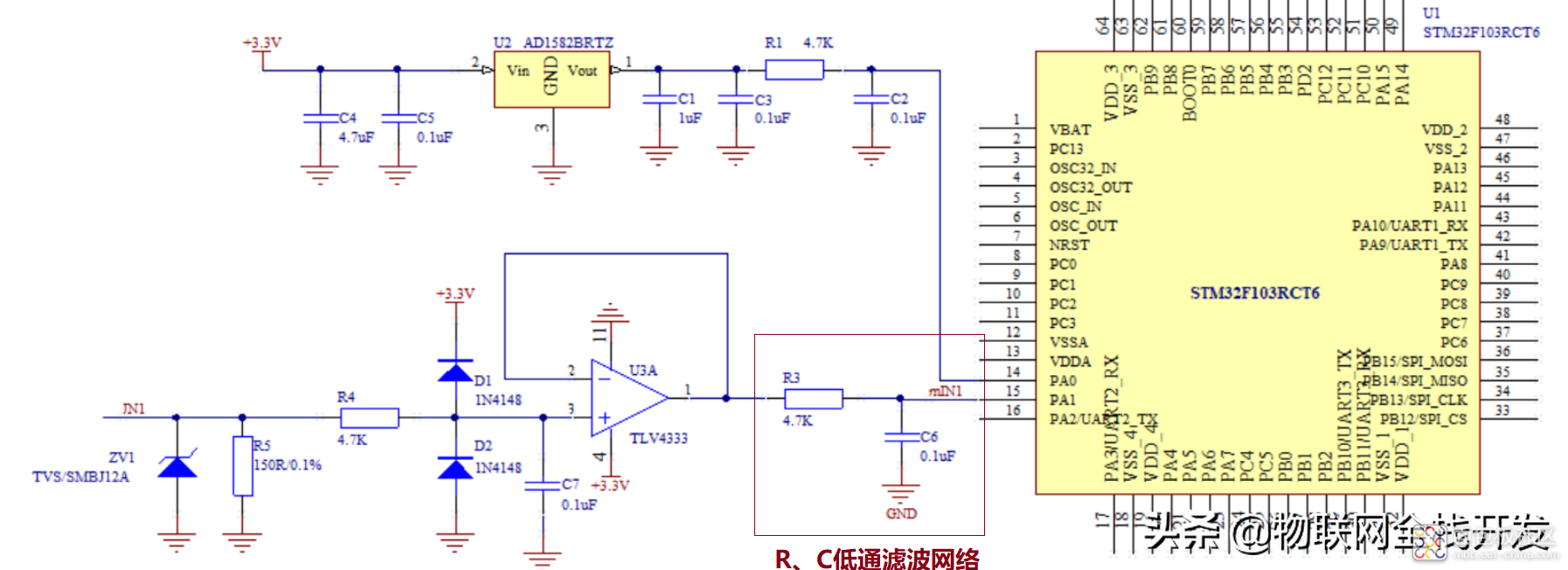

在规格书的最大规格参数中提到,输入到模拟输入口这些非5V兼容的端口的电压不能超过4.0V,另外还有注释说明,在任何情况下,端口的注入电流不得高于5mA,总的注入电流不得高于25mA。

IO口注入电流要求

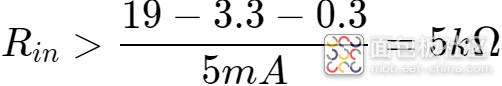

根据这一要求,考虑当外部输入电压通过12V的TVS管最高钳位至19V。

则外部输入电阻

。

二、低通滤波

电阻和电容可以组成一阶滤波器,如下图所示在A/D输入端口加上电阻、电容组成的低通滤波电路,并将电容和电阻靠近端口放置。

可以有效滤除输入信号的干扰,包括运放输出的干扰以及从运放到端口的导线从空间耦合的干扰。

图4.R3、C6组成的低通滤波网络

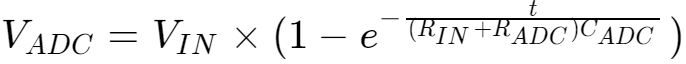

我们知道,R、C低通滤波网络的-6dB截止频率为:

截止频率由R、C的乘积决定,当C固定时,R越小,截止频率越高,对高频干扰的过波效果越差。

因此,需要根据有效信号,选择合适的电阻R以达到最佳的滤波效果。

[size=1.118em]电阻越大越好?

[size=1.118em]

从输入限流的角度来看,输入电容越大越好。

但是我们还需要考虑对A/D转换的影响。

A/D转换器的每一个通道都有模拟开关,分为以下步骤完成一次转换:

1)选通模拟开关,此时外部电压通过外部输入电阻以及模拟开关的电阻向采样保持电容充电(输入端口与地之间没有并联电容);

2) 选通一段时间后,断开模拟开关,由于采样保持电容两端的电压不能突变,所以电容能保持输入电压;

3) 转换器对采样保持电容上的电压与参考电压进行逐次比较,将模拟量转为数字量。

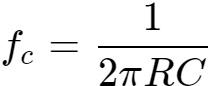

在STM32处理器中,模拟开关的选通时间可以通过寄存器设置,如下图:

图5.采样时间的设置

当图4的电路中,当不存在C6时,在步骤1的采样内,其等效电路为:

图6.充电电路

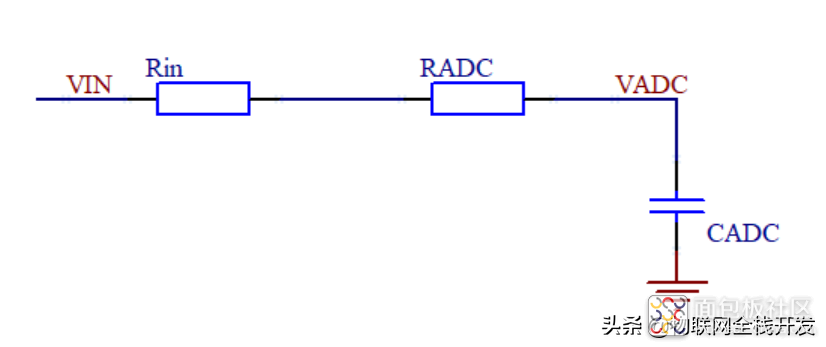

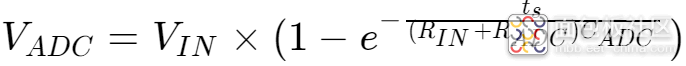

此时,VADC的充电方程表示为:

在步骤1结束时,时间t=ts,得到采样保存电容上的电压为:

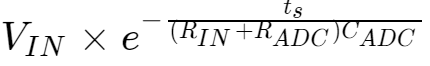

其与输入电压VIN的误差值为:

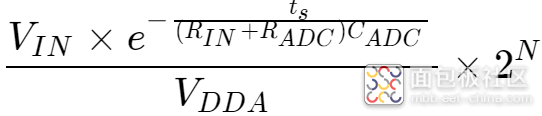

对应的A/D值为:

式中N为A/D转换器的位数,

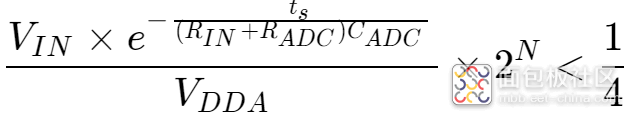

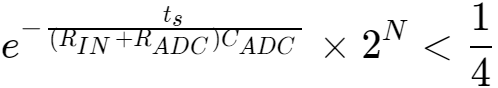

ADC的分辨率为1/2LSB,误差必须比分率更小,考虑小于1/4LSB,得到:

当VIN=VDDA时,所产生的误差最大,所以有:

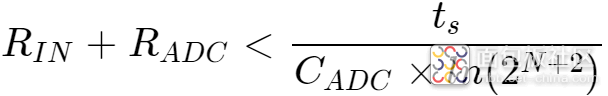

化简得到:

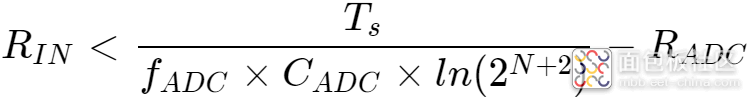

而ts=Ts*1/fADC,最终得到:

在前几天分享的代码中,fADC=14MHz, Ts=28.5cycles ,N=12,则可以算出:

RIN< 25.2kΩ。

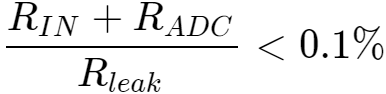

另外还需要考虑到端口的输入漏电流对A/D采样精度的影响;

从图1中可以看到漏电流为1uA,等效于下拉3MΩ的漏电阻。

简单估算为了达到0.1%的精度,

RIN+RADC<3kΩ, RIN<2kΩ。

[size=1.059em]总结

[size=1.059em]

- 当输入电压超过端口允许电压范围时,流过端口电流必须小于5mA,要求电阻必须大于5kΩ。

- 为了滤除高频干扰,在输入端增加R、C低通滤波网络,电阻R的阻值应尽量大,以增强滤波效果,但是需要根据有效信号的频率选择合适的R、C。

- 为了在采样时间内,采样保持电容上的电压与实际输入电压的误差可以被忽略,由采样保持时间,采样频率,ADC的位数计算出最大输入电阻阻值。

- 为了降低ADC转换器的漏电流对测量精度的影响,根据精度要求估算出最大输出电阻。

- 在ADC输入口并联电容,可以再实现一级ADC的充放电的缓冲,使得外部输入电阻增大的情况下,采样保持电容由并联电容充电,仍然可以满足分辨率要求。

来源:物联网全栈开发

/3

/3