原创首发于公众号:射频工程师的日常

对于电流,首先明确2个概念:

1)电流是个闭合环路,流入电流和流出电流相等;

2)电流流过阻抗最小的路径,低频时(KHz或更低),阻抗由电阻控制,因此电流采用电阻最小的路径。高频时(MHz或更高),阻抗由电感控制,因此电流采用电感最小的路径。

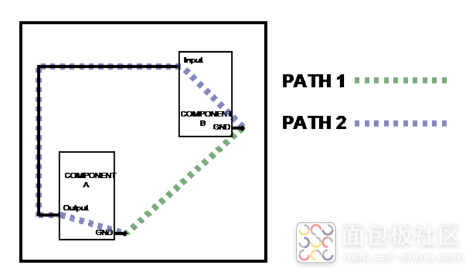

如图1所示,A 输出一个50MHz信号到 B 的输入引脚,此时必须有相同的电流从B流向A。在这种情况下,我们假设该电流离开元器件B的GND,并返回A的GND。由于有一个完整的地平面,并且两个元件的接地引脚都很接近,如果不考虑50MHz的信号,电流在它们之间采用电阻最短的路径(PATH 1)。但是高频电流采用电感最小或环路面积最小的路径。因此,返回平面上的大部分信号电流在信号走线正下方的窄路径(PATH 2)中流动。

图 1:信号返回电流采用哪条路径?

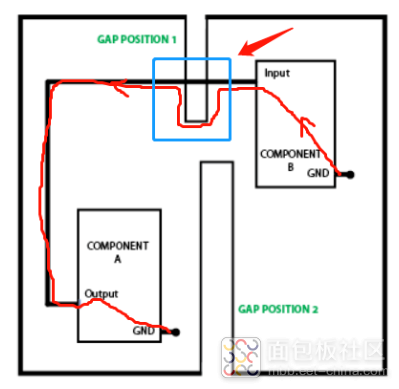

如果地平面做了分割,如图2所示,位置2的间隙对信号完整性或辐射发射几乎没有影响。然而位置1的间隙可能会导致重大问题,在分割间隙下方的返回电流会绕过这段间隙,增加信号环路面积。

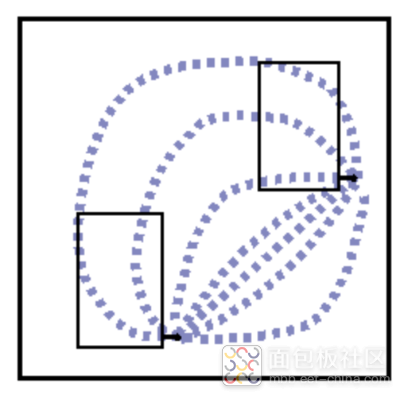

图 2:间隙位置1会影响信号返回电流的流动在低频时(kHz及以下),平面的电阻倾向于将电流分散开来,因此在两个远点之间流动的电流可以覆盖电路板的大部分,如图3所示。在混合信号板上,使用低频模拟和数字元件时可能会产生问题,需考虑到这一点。

图 3:低频返回电流路径

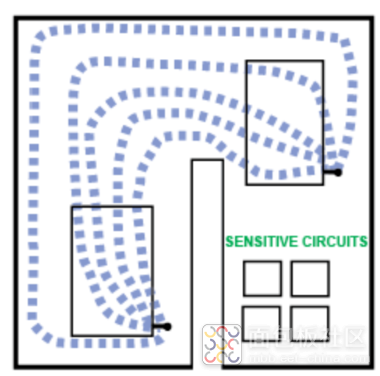

图 4 示范了接地层中放置良好的间隙如何保护位于电路板特定区域的敏感电路,免受平面中流动的低频返回电流的影响。

图 4:带间隙平面的低频返回电流路径

参考文档:LearnEMC - Introduction to Printed Circuit Board Layout for EMC

- MLCC电容、铝电解电容、电感、磁珠的阻抗曲线

- 你的测试电源有问题吗--由DCDC输出短路引起的实验室电源振荡引发的思考

- 输出电容的ESR对DC_DC的影响——电感发烫排查思路

- DC-DC电路的环路补偿的调试经验

- DCDC空载时,静态电流10mA正常吗?

- BUCK实例:同步降压芯片LMR50410-Q1 EN脚电压在Start-up误触问题解决方案

- EMI/EMC设计经典70问答

- 工程师笔记--设计中常忽略的几点问题

- 2个简单的面试问题,请不要为你的想当然买单!

- PCB Layout 才是决定EMC质量的关键

/2

/2