英特尔PowerVia 互连技术展示了 6% 的性能提升

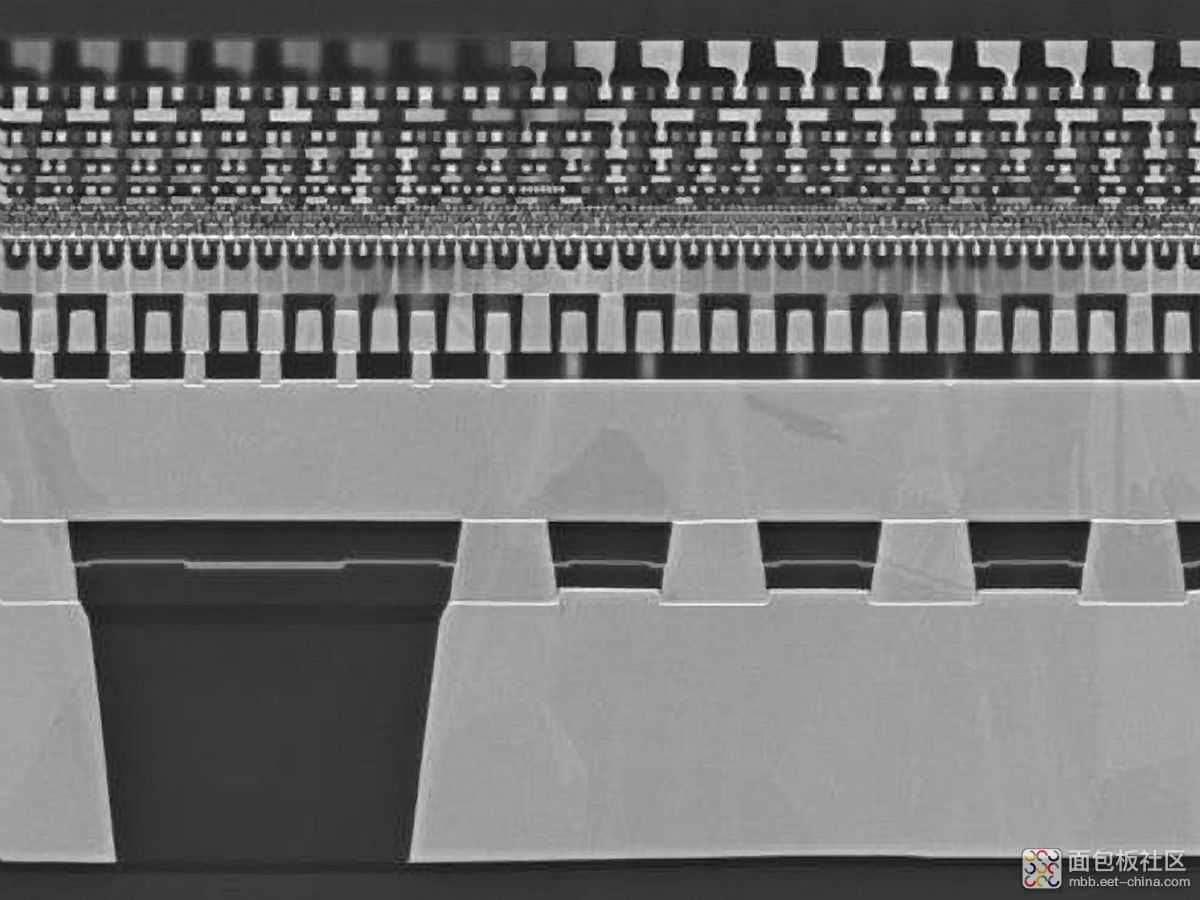

英特尔的 Power Via 演示芯片表明,未来的芯片中将只剩下很少的硅。 纤细的硅部分 [中心白线] 包含所有晶体管。 供电互连位于它们下方,数据传输互连位于上方。

为尖端计算机芯片部署新技术存在很多风险。 因此,英特尔高管在执行明年同时推出新晶体管 RibbonFET 和为其供电的新方法 PowerVia 的计划时持谨慎态度是可以理解的。

为了降低这种走钢丝行为的一些风险,该公司构建并测试了由英特尔当前一代的晶体管与 PowerVia 相结合的处理器内核。 由此产生的内核频率提升超过 6%,设计更紧凑,功耗降低 30%。 同样重要的是,测试证明,包括背面电源不会使芯片成本更高、可靠性更低或更难测试缺陷。 英特尔将于下周在东京举行的 IEEE 超大规模集成电路技术和电路研讨会上介绍这些测试的细节。

英特尔技术开发副总裁 Ben Sell 表示:“我们希望确保我们能够降低风险……了解有关 PowerVia 的一切,然后进行下一步并与 RibbonFET 集成。”

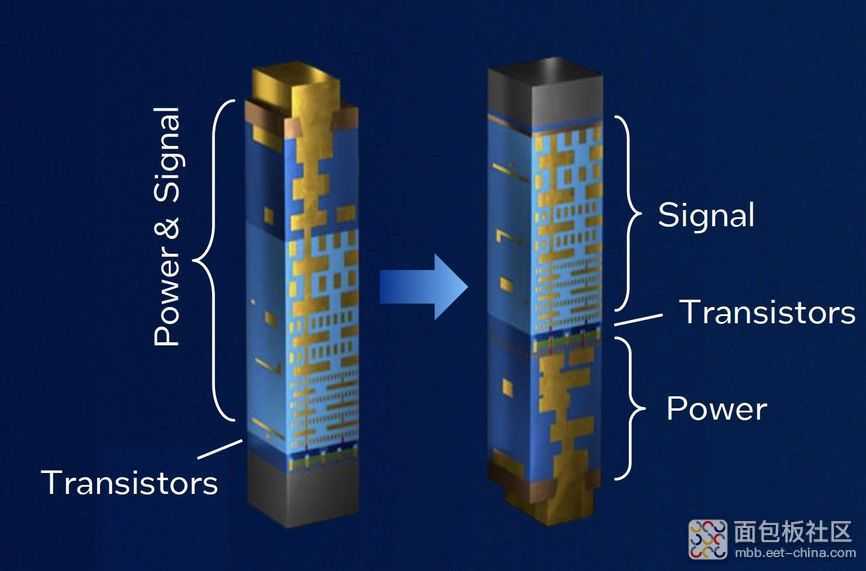

PowerVia 是英特尔版本的一种称为背面供电的技术。 今天,芯片是用硅表面的晶体管和所有为它们供电和传输数据信号的互连构建在它们上面的。 背面电源移除了硅下方的所有供电互连。 这有两个主要影响。 首先,它为硅上方的数据互连留出了更多空间。 其次,电源互连可以做得更大,因此电阻更小。

背面供电将电源互连从硅上方移动到硅下方。

这种组合在几个方面提高了性能。 首先,通过更容易的电源流动路径,CPU 上的电路会经历更少的电压降; 换句话说,当对电流的需求增加时,例如,大块逻辑开关打开时,电压的瞬态下降较小。 随着下降的减少,晶体管可以运行得更快。

其次,核心可以做得更紧凑,减少逻辑单元之间的互连长度,从而加快速度。 当构成处理器核心的标准逻辑单元被布置在芯片上时,互连拥塞使它们无法完美地组合在一起,从而在单元之间留下大量空白空间。 随着数据互连之间的拥塞减少,单元更紧密地结合在一起,一些部分的填充率高达 95%。 Sell 说这是两位数的改进。 更重要的是,由于没有拥塞,一些最小的互连可以散开一点,从而减少了影响性能的寄生电容。

当芯片制造商将晶体管从一个技术节点缩小到下一个技术节点时,这些优势带来的 6% 收益大约是通常收益的一半。 PowerVia 在不改变晶体管的情况下提供它。

PowerVia 是如何制造的

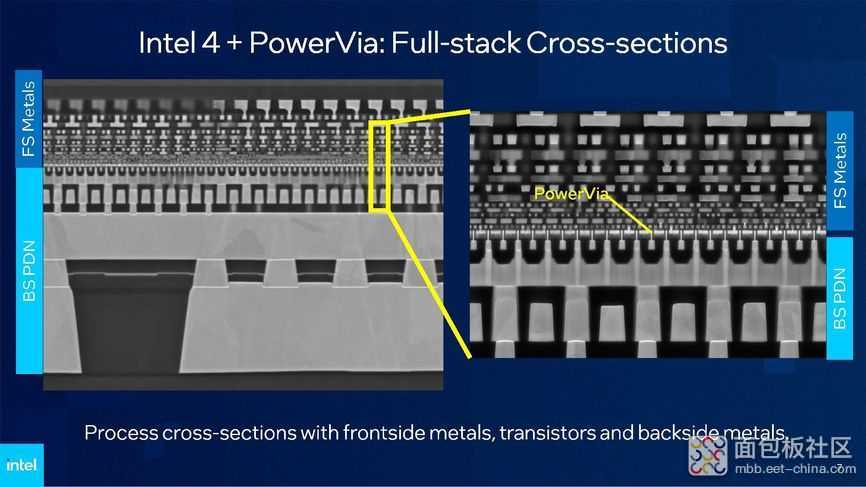

制造支持 PowerVia 的芯片需要几个额外的步骤,并导致芯片中几乎没有剩余硅的不寻常结果。 事情一开始很正常:晶体管,在本例中是使用 Intel 4 工艺制造的 FinFET,像往常一样构建在硅的表面。 主要区别在于,还钻了一组又深又窄的孔,然后用金属填充。 这些纳米 TSV(用于硅通孔)稍后将很重要。 从那里开始,在晶体管上方形成互连层,将它们连接在一起形成逻辑单元和更大的电路。 到目前为止,如此规律。

然后这个过程开始了。 一个空白的硅晶圆,称为载体晶圆,被键合到这些互连的顶部,整个东西被翻转过来。 然后原始晶圆的底部(现在在顶部)被抛光,直到纳米 TSV 的末端暴露出来。 在那一点上,相对厚实的互连层被建立起来以连接到纳米 TSV 并形成背面功率传输网络。 这些互连层终止于将芯片连接到封装和计算机其余部分的焊盘。

因此,最终的芯片由一大层用于支撑的空白硅、一层数据互连、一层极窄的硅晶体管层和一层电源互连组成。

很难在这个支持 PowerVia 的处理器中找到硅。 (提示:这是中间的一点白色。)大部分芯片由上方的信号互连和晶体管下方的更厚实的电源互连组成。

您可能认为必须在硅的两面都建立互连会使芯片的成本飙升。 但很早以前,英特尔就发现了事实并非如此的原因,Sell 说。 最小、最紧密的互连层称为 M0,其生产成本也是最高的。 它们可能需要多次通过芯片制造中最昂贵的步骤,即极紫外光刻。 但由于没有电源互连阻碍,M0 层中的线路可能比现在的距离多 6 纳米。 这可能看起来不多,但这意味着制造它们需要更少的 EUV 努力。 对于明年将推出的工艺及其后继工艺,“我们从不如此积极地扩展中获得的成本节省足以抵消背面功率传输工艺的额外成本,”Sell 说。

消除 PowerVia 的风险

如果 PowerVia 的计划要奏效,该技术必须满足某些标准,其中大部分与不让事情变得更糟有关:尽管存在于更薄的硅层中,但晶体管必须同样工作; 电力传输网络必须与在硅片前端构建的网络一样可靠; 尽管晶体管夹在互连层之间,但硅中产生的热量无法控制; 调试 IC 和发现设计缺陷的能力不受阻碍。

需要做一些工作才能满足这些标准。 例如,必须调整电源互连工艺,以免影响晶体管。 英特尔必须制定一些设计规则来解决散热问题。 它还必须想出新的方法来进行调试。

最重要的是,英特尔工程师必须确保 PowerVia 芯片的良率(每片晶圆上合格芯片的比例)达到实现大批量生产的目标,即使这些特定芯片永远不会出售。 这里的目标是让 Intel 4 PowerVia 芯片的产量与 9 个月前的 Intel 4 芯片相匹配。 PowerVia 芯片总是会滞后,因为对 Intel 4 产量的任何改进都需要时间才能转化为 PowerVia 实验。 “我们做得比那好一点,”塞尔说。 PowerVia 的收益率曲线仅跟随英特尔 4 的 6 个月。

2024 年及以后

随着 PowerVia 工艺的制定,英特尔要完成从英特尔 4 到下一个节点(称为 20A)的迁移,唯一需要做的就是晶体管。 RibbonFET,英特尔对纳米片或环栅晶体管的采用,然后将插入已经建立的互连方案。

如果一切顺利,Sell 表示一切顺利,20A 工艺将在 2024 年制造公司的 Arrow Lake CPU。下一代技术称为 18A,适用于英特尔产品和代工客户。

成功将使英特尔在提供纳米片晶体管和背面电源方面领先于台积电和三星。 三星已经转向环栅设备,目前还不清楚它何时会集成背面电源。 台积电计划在 2025 年提供环栅器件,但至少要到 2026 年才会增加背面供电。

VIA: https://spectrum.ieee.org/backside-power-delivery

/2

/2