问题描述:

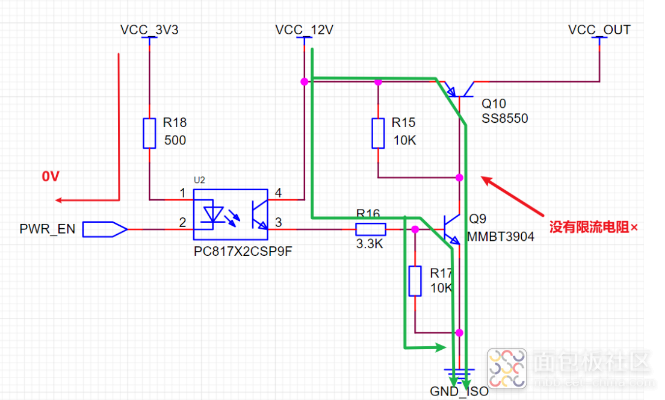

电路图如下,是一个光耦控制输出的电路,电路的本意是PWR_EN输出低电平光耦导通,然后三极管Q9打开,三极管Q10打开,VOUT输出。但是实测下来,不焊接Q10没问题,焊接Q10就有问题。

电路设计问题:

Q10没有基极限流电阻,导致三极管Q9导通后,Q10的基极电流过大导致三极管Q10和三极管Q9烧毁,电流路径如下图:

解决方案:

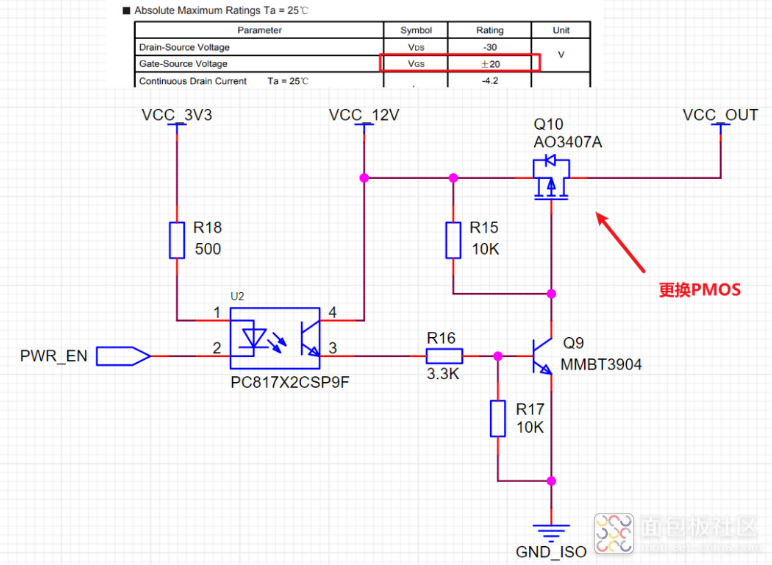

- 不更改PCB,将PNP型三极管更换为PMOS,但是需要注意Vgs需要满足>12V,以防Vgs过压导致PMOS烧毁,例如更改为下图的AO3407(大概挑了一个,可以按照实际需求实际选取合适的PMOS):

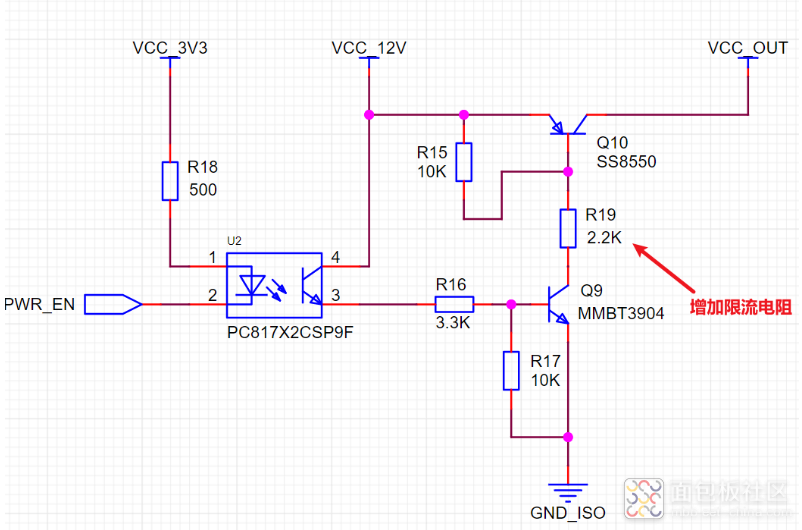

2. 更改PCB,为三极管Q10增加基极限流电阻。电路更改例如下图:

总结:建议更改PCB,增加基极限流电阻。这个电路中,就算是PMOS也建议增加合适的栅极电阻,以防Vgs过压损坏。

/4

/4