以太网电路在嵌入式设计中应用非常多,以前会照着Demo进行设计,但是对很多顶层和底层的东西都不太理解,今天这个笔记是为了整理和梳理以前的知识,为以后继续学习搭建基本框架,这是我把这篇文章放到自学笔记里面的原因。

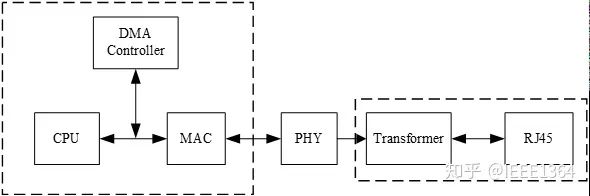

一.以太网电路的基本构成 一般一个嵌入式终端系统的以太网部分如下图

主要有MAC控制器、PHY芯片、网络变压器和RJ45接头组成,有的系统会有DMA控制。一般的系统中CPU和MAC以及DMA控制器都是集成在一块芯片上的,为了节省空间简化设计,很多时候网口的变压器和RJ45的接头集成在一起。

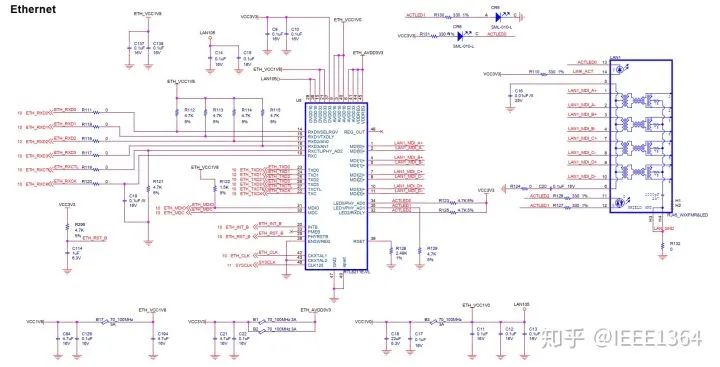

下图就是PYNQ开发板的以太网的原图。

二.技术细节

2.1.MAC

MAC即Media Access Control,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。该层协议是以太网MAC由IEEE-802.3以太网标准定义。

2.2.PHY芯片

PHY是物理接口收发器,它实现物理层。IEEE-802.3标准定义了以太网PHY。包括MII/GMII(介质独立接口)子层,PCS(物理编码子层),PMA(物理介质附加)子层,PMD(物理介质相关)子层,MDI子层。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC。对于100BaseTX因为使用4B/5B编码,每4bit就增加1bit的检错码),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去。收数据时的流程反之。

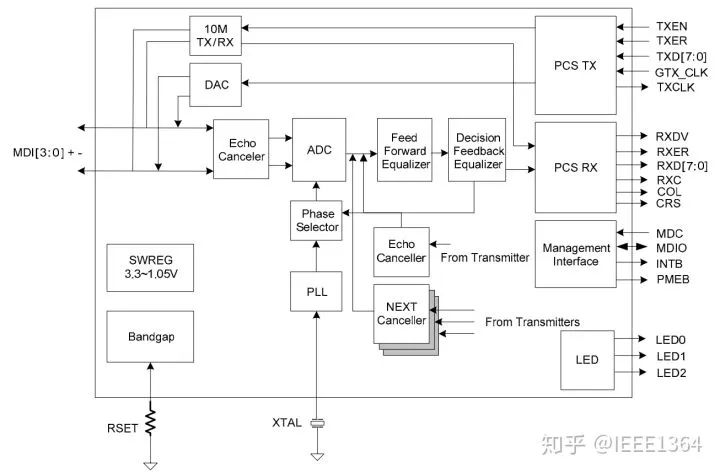

下图就是前面PYNQ开发板中用到的RTL8211E的结构框图,

2.3.MII接口

2.3.1简介

MII即“媒体独立接口”,也叫“独立于介质的接口”。它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。RMII全称为“简化的媒体独立接口”,是IEEE-802.3u标准中除MII接口之外的另一种实现。

2.3.2 MII接口详解

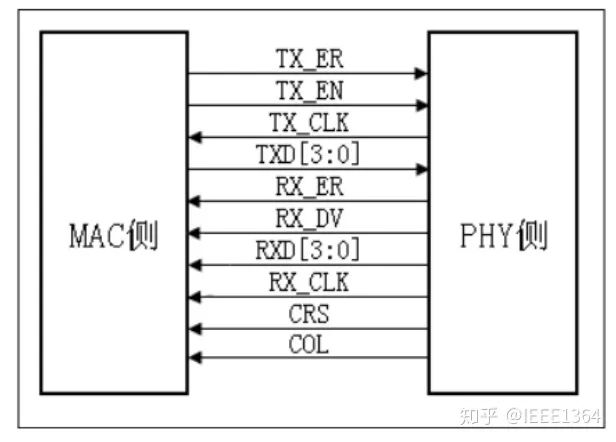

MII支持10M和100M的操作,单向传输的数据线有4根,整个接口由14根线组成。

MII_TX_CLK:发送数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

MII_RX_CLK:接收数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

MII_TX_EN:传输使能信号,此信号必需与数据前导符的起始位同步出现,并在传输完毕前一直保持。

MII_TXD[3:0]:发送数据线,每次传输4位数据,数据在MII_TX_EN信号有效时有效。MII_TXD[0]是数据的最低位,MII_TXD[3]是最高位。当MII_TX_EN信号无效时,PHY忽略传输的数据。

MII_CRS:载波侦听信号,仅工作在半双工模式下,由PHY控制,当发送或接收的介质非空闲时,使能此信号。PHY必需保证MII_CRS信号在发生冲突的整个时间段内都保持有效,不需要此信号与发送/接收的时钟同步。

MII_COL:冲突检测信号,仅工作在半双工模式下,由PHY控制,当检测到介质发生冲突时,使能此信号,并且在整个冲突的持续时间内,保持此信号有效。此信号不需要和发送/接收的时钟同步。

MII_RXD[3:0]:接收数据线,每次接收4位数据,数据在MII_RX_DV信号有效时有效。MII_RXD[0]是数据的最低位,MII_RXD[3]是最高位。当MII_RX_EN无效,而MII_RX_ER有效时,MII_RXD[3:0]数据值代表特定的信息(请参考表194)。

MII_RX_DV:接收数据使能信号,由PHY控制,当PHY准备好数据供MAC接收时,使能该信号。此信号必需和帧数据的首位同步出现,并保持有效直到数据传输完成。在传送最后4位数据后的第一个时钟之前,此信号必需变为无效状态。为了正确的接收一个帧,有效电平不能滞后于数据线上的SFD位出现。

MII_RX_ER:接收出错信号,保持一个或多个时钟周期(MII_RX_CLK)的有效状态,表明MAC在接收过程中检测到错误。具体错误原因需配合MII_RX_DV的状态及MII_RXD[3:0]的数据值。

在上面所列的通信接口外,往往还有一个串行接口用来进行PHY芯片的配置。

MDC——配置接口时钟

MDIO——配置接口I/O

2.3.3 RMII、GMII、RGMII和MII的关联与区别

MII的一个缺点是:它的每个端口用的信号线太多,如果一个8端口的交换机要用112根线,32端口就要用到448根线,如果按个接口做交换机,不太现实,所以现代交换机会采用其它一些从MII简化而来的标准,如RMII、SMII、GMII等。

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线;和MII一样,RMII支持10M的总线接口速度。

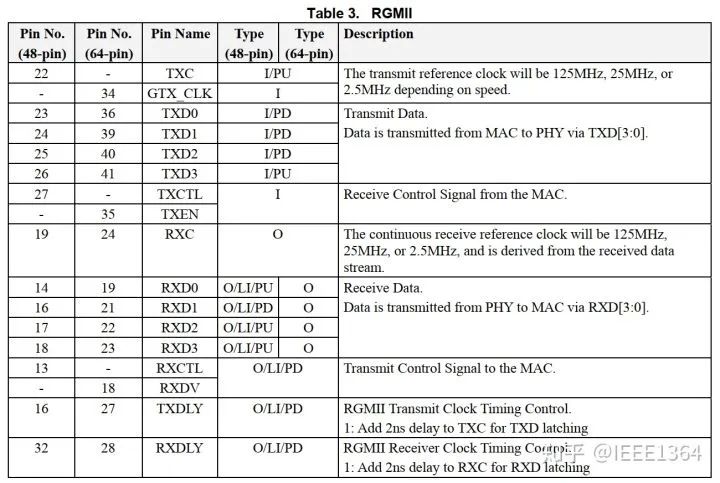

GMII是千兆网的MII接口,RGMII表示简化了的GMII接口。

RGMII接口减少了MAC与PHY之间的走线数量,通过在参考时钟的上升/下降沿同时采样及信号复用得以实现。

下表是RTL8211的RGMII接口的引脚列表。

SMII是由思科提出的一种媒体接口,它有比RMII更少的信号线数目,S表示串行的意思。因为它只用一根信号线传送发送数据,一根信号线传输接受数据,所以在时钟上为了满足100的需求,它的时钟频率很高,达到了125兆,为什么用125兆,是因为数据线里面会传送一些控制信息。SMII一个端口仅用4根信号线完成100信号的传输,比起RMII差不多又少了一倍的信号线。SMII在工业界的支持力度是很高的。同理,所有端口的数据收发都公用同一个外部的125M时钟。

介绍了好几种MII接口,想必有点混乱了,下表简单总结了一下各种MII接口的特征

现在RGMII接口应该是比较主流的接口了。

2.4.以太网变压器

变压器作用是:

1.耦合差分信号,抗干扰能力更强

2.变压器隔离网线端不同设备的不同电平,隔离直流信号

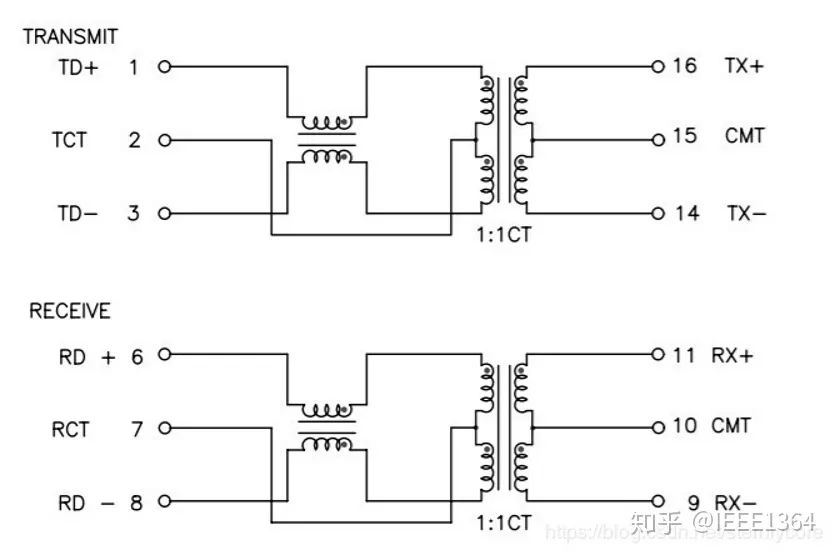

网络变压器一般是由差模线圈,变压器以及中心抽头组成。如下示意:

其中初级中心抽头的接法需要根据PHY芯片来决定,电压驱动的就要接电源,电流驱动直接接个电容到地即可。还需要注意的是有的变压器中间抽头是独立的有的是收发合并在一起的,设计的时候需要注意,为了防止初版硬件设计错误,可以兼容设计。

2.5.RJ45

以太网信号最终是通过RJ45接头接入网络的。

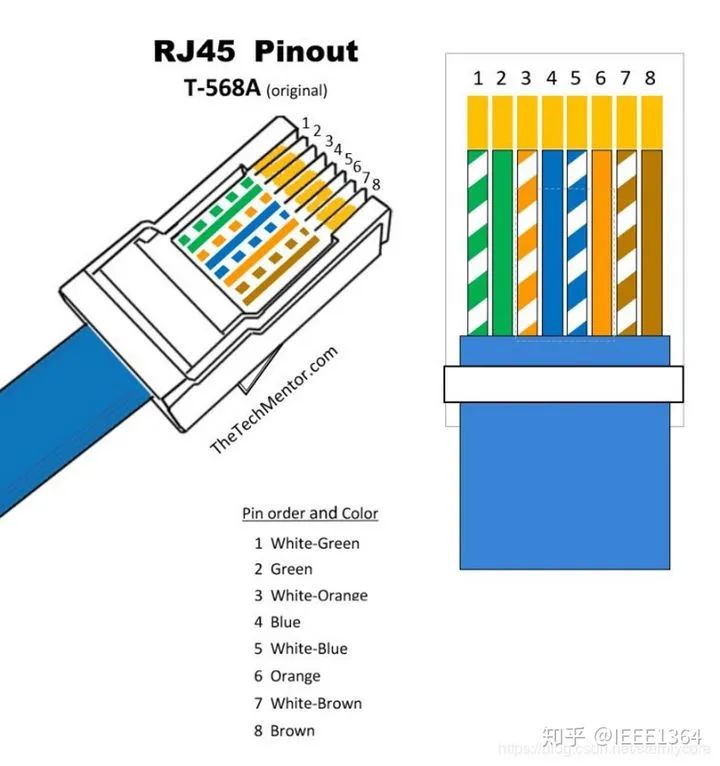

RJ是Registered Jack的缩写,意思是“注册的插座”。在FCC(美国联邦通信委员会标准和规章)中RJ是描述公用电信网络的接口,计算机网络的RJ45是标准8位模块化接口的俗称。连接器由插头(8P8C接头,水晶头)和插座组成。如下图所示:

关于接头引脚定义,目前存在两种标准:T568A和T568B(最通用)。这两者的主要区别是橙色和绿色双绞线进行了交换,如下图所示:

设计这两种标准只是在线缆颜色上有所区别,目的是在线缆侧实现交叉互连。网络直通线常用于异种网络之间的互连(比如计算机交换机之间),交叉线常用于同种网络之间的互联(比如计算机与之间)。不过现在PHY芯片大部分具有自动交叉(auto MDI-X)的能力,只需要直连即可。不同网络速率及网络介质下引脚作用也不相同,如下图示意:

2.6小结

到此,我们就已经了解了一个嵌入式终端以太网物理层的基本设计。当然一篇简单的文章不能包含所有的细节,但是一般不会超出这个框架,以后在某一方面遇到问题基本都可以在这个框架下去看。

3.1.以太网的信号线走线

以太网的信号线是以差分对(Rx±、Tx±)的形式存在,差分线具有很强共模抑制能力,抗干扰能力强,但是如果布线不当,将会带来严重的信号完整性问题。下面我们来一一介绍差分线的处理要点:

a)优先绘制Rx±、Tx±差分对,尽量保持差分对平行、等长、短距,避免过孔、交叉。由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里;

b)当速度要求高时需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%;

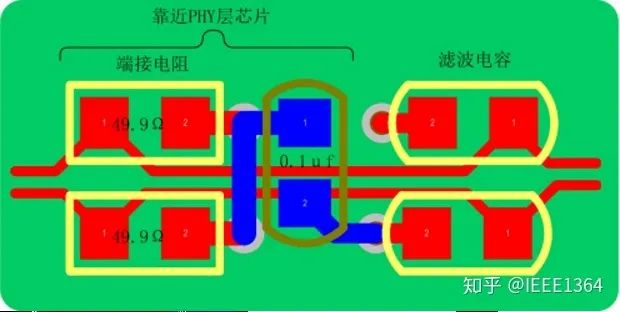

c)差分信号终端电阻(49.9Ω,有的PHY层芯片可能没有)必须靠近PHY层芯片的Rx±、Tx±管脚放置,这样能更好的消除通信电缆中的信号反射;

d)差分线对上的滤波电容必须对称放置,否则差模可能转成共模,带来共模噪声,且其走线时不能有stub ,这样才能对高频噪声有良好的抑制能力。

3.2.RJ45未集成变压器的布局布线

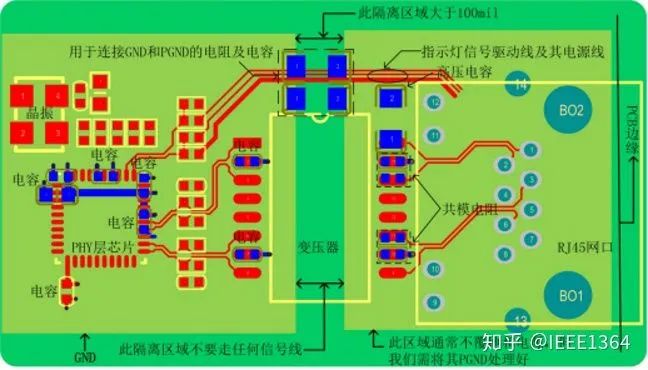

上图是变压器没有集成在网口连接器的电路PCB布局、布线参考,需要注意以下几点

a)RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;

b)PHY层芯片的电源滤波按照要芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小;

c)网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小;

d)网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil);

e)变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。这样做分割处理,就是为了达到初、次级的隔离,控制源端的干扰通过参考平面耦合到次级;

f)指示灯的电源线和驱动信号线相邻走线,尽量减小环路面积。指示灯和差分线要进行必要的隔离,两者要保证足够的距离,如有空间可用GND隔开;

g)用于连接GND和PGND的电阻及电容需放置地分割区域。

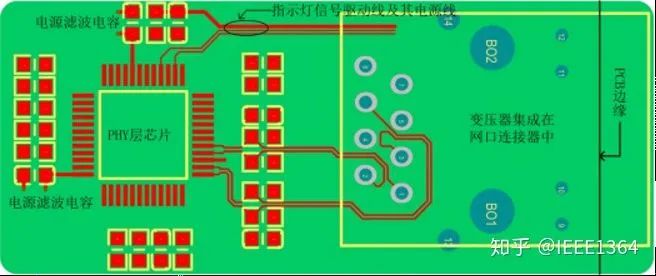

3.3.RJ45集成变压器的布局布线

变压器集成在连接器的以太网电路的PCB布局、布线较不集成的相对简单很多,下图 3是采用一体化连接器的网口电路的PCB布局、布线参考图:

3.4.ESD保护芯片

在一些工业场景下环境恶略需要增添ESD保护器件,ESD器件一版放到靠近连接器位置,对于百兆以太网来说只需要4通道低结电电容器件,根据需要的静电等级进行型号选型。

参考链接 1.揭秘以太网接口在印PCB上的实现2.PHY Transceiver硬件设计注意事项3.Ethenet: MAC PHY MII RMII - QIYUEXIN4.MII与RMII接口的区别5.以太网媒体接口:MII、RMII、SMII、GMII、RGMII6.网口扫盲三:以太网芯片MAC和PHY的关系

本文由编辑推荐,原出处:https://www.eet-china.com/mp/a147126.html

/2

/2