在CMOS集成电路中,以金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称MOS管)作为开关器件。

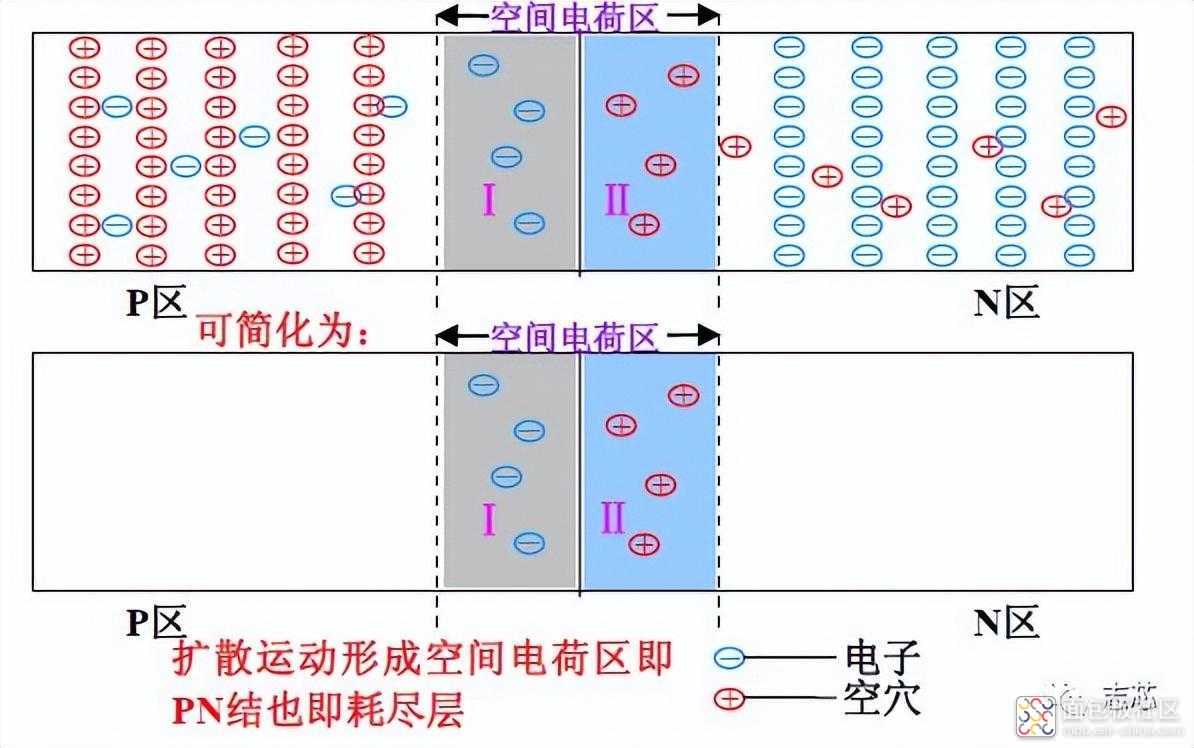

1、扩散、漂移、耗尽层、结电容、PN结

扩散、漂移:多子的运动称为扩散;少子的运动称为漂移。

耗尽层、结电容、PN 结:PN 结中由于p 区和n 区的电子空穴发生中和,在结中会形成耗尽区,PN 结因此可以叫耗尽层,由于PN 结反向不导通,因此可以叫做阻挡层。耗尽层是指PN 结中在漂移运动和扩散作用的双重影响下载流子数量非常少的一个高电阻区域。耗尽层的宽度与材料本身性质、温度以及偏置电压的大小有关。在PN 结中,由于载流子浓度的梯度,空穴、电子会通过扩散作用的形式分别向掺杂浓度低的N 区、P 区移动,P 区流走空穴流进电子并大部分中和P 区空穴,剩下少量电子,N 区流走电子流进空穴并中和N 区电子,剩下少量空穴。扩散作用产生的少数载流子(P 区多出的电子和N 区多出的空穴)会产生一个较强的内建电场。这个电场会使载流子发生漂移运动,这一运动与扩散的方向正好相反,二者会达成动态平衡。

这两种作用的结果是在PN 结处形成一个电子、空穴都很稀少的耗尽层,即其中的载流子——电子和空穴都被耗尽了。因为耗尽层中载流子少,电阻大,其特征类似电容,这一电容也被称为结电容。PN结反偏会使耗尽层变厚。

图1

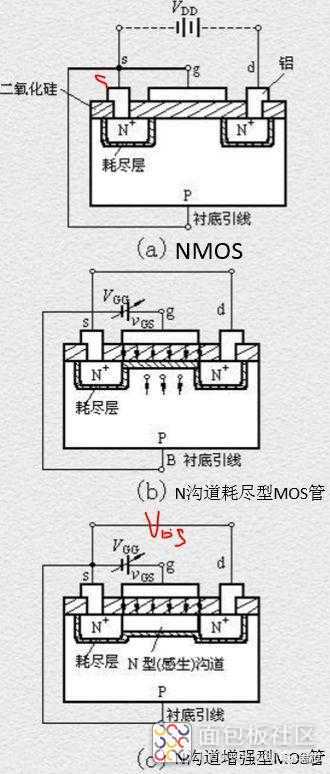

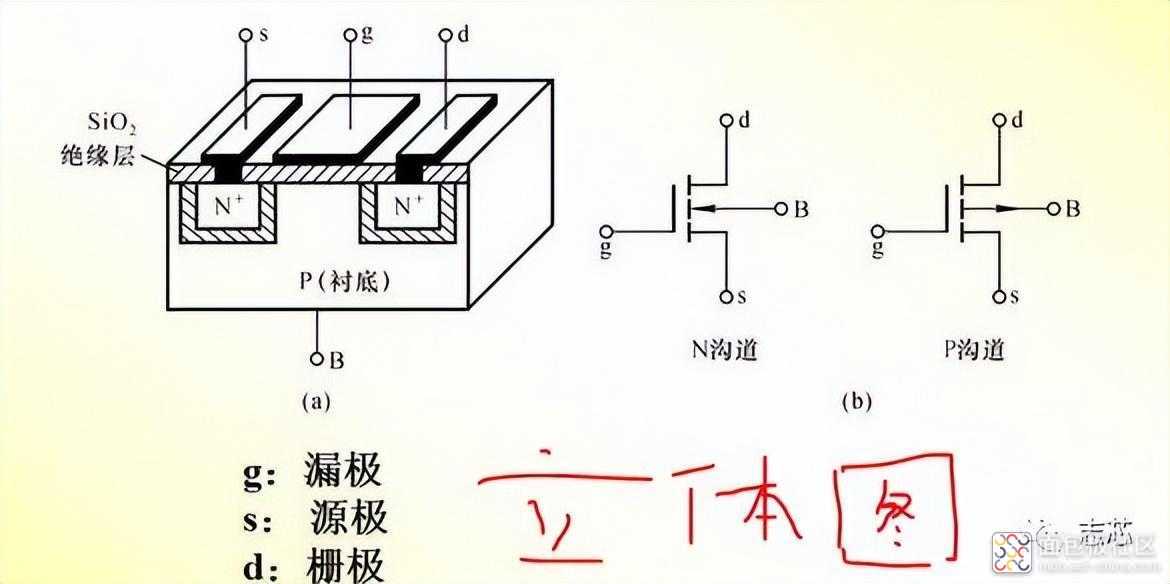

2、CMOS管的结构和工作原理

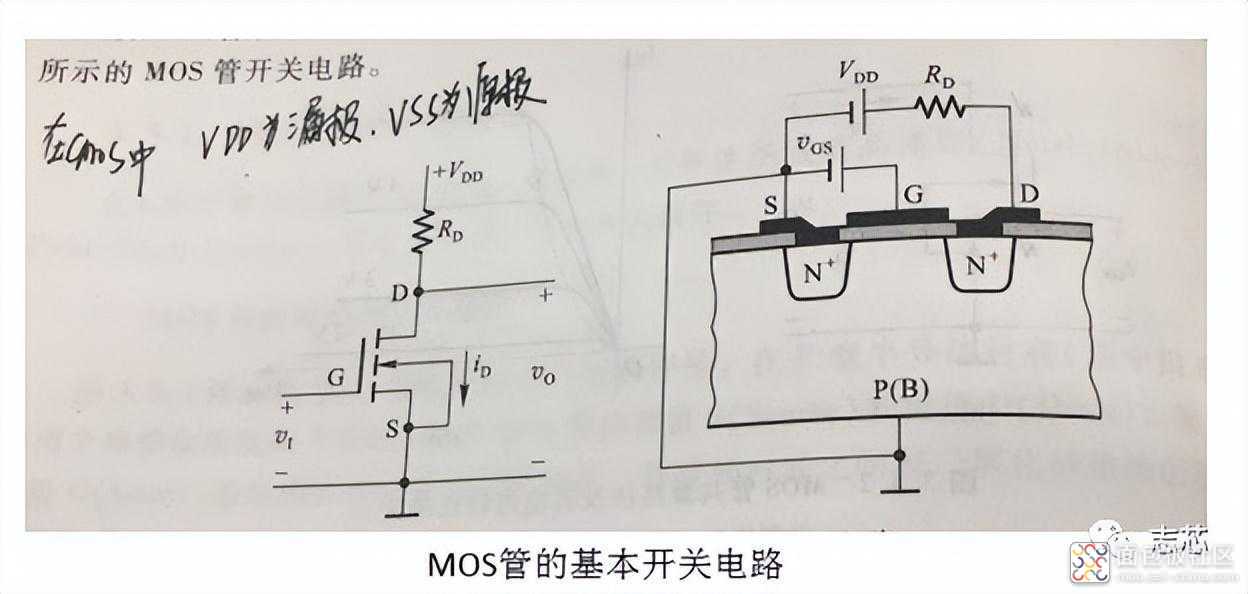

如图所示是MOS管的结构示意图和符号。在P型半导体沉底(图中用B标示)上,制作两个高掺杂浓度的N型区,形成MOS管的源级S(Source)和漏级D(Drain)。第三个电极称为栅极G(Gate),通常用金属铝或多晶硅制作。栅极和衬底之间被二氧化硅绝缘层隔开,绝缘层的厚度极薄,在0.1um之内。

图2

图3

如果在漏级和源极之间加上电压VDS,而令栅极和源极之间的电压VGS,则由于漏级和源极之间相当于两个PN结背向地串联,所以D-S间不导通,iD=0.

当栅极和源极之间加有正电压VGS,而且VGS大于某个电压值VGS(th)时,由于栅极与衬底间电场的吸引,使衬底中的少数载流子——电子聚集到栅极下面的衬底表面,形成一个N型的反型层。这个反型层就构成了D-S间的导电沟道,于是有iD流通。VGS(th)称为MOS管的开启电压。因为导电沟道属于N型,而且在VGS=0时不存在导电沟道,必须加以足够高的的栅极电压才有导电沟道的形成,所以将这种类型的MOS管称为N沟道增强型MOS管。

随着VGS的升高,导电沟道的截面积也将加大,iD增加。因此,可以通过改变VGS控制iD的大小。

为了防止有电源从衬底流向源级和导电沟道,通常将衬底和与源级相连,或将衬底接到系统得的最低电位上。

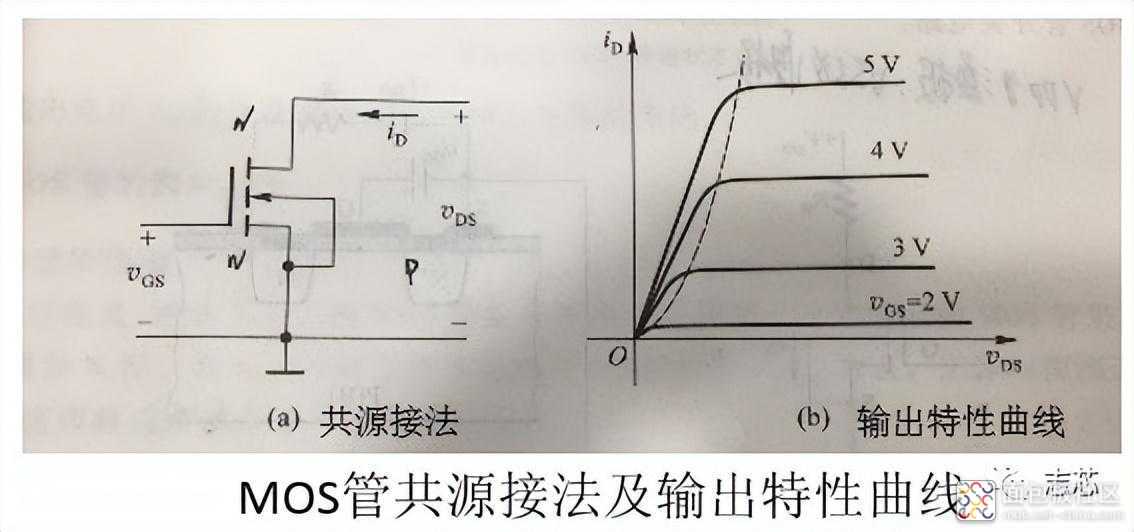

3、MOS管的输入特性和输出特性

若以栅极-源极间的回路为输入电路,以源极-漏极间的回路为输出回路,则称为共源接法,如图a所示。由图2可见,栅极和衬底间被二氧化硅绝缘层所隔离,在栅极和源极间加上电压VGS以后,不会有栅极电流流通,可以认为栅极电流等于零。因此,就不必要再画输入特性曲线来表示了。

图4

上图b给出了共源接法下的输出特性曲线。这个曲线又称为MOS管的漏极特性曲线。漏极特性曲线分为三个工作区。当VGS小于VGS(th)时,漏极和源极之间没有导电沟道,iD≈0.这时D-S间的内阻非常大,可达10的9次方Ω以上。因此将曲线上VGS<VGS(th)的区域称为截止区。当VGS>VGS(th)以后,D-S间出现导电沟道,有iD产生。曲线上VGS>VGS(th)的部分又可分成两个区域。

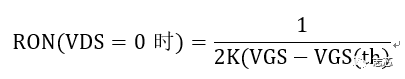

上图b所示的漏极特性曲线上虚线左边的区域称为可变电阻区。在这个区域内,当VGS一定时,iD与VDS之比近似地等于一个常数,具有类似于线性电阻的性质。等效电阻的大小和VGS的数值有关。在VDS≈0时,MOS导通电阻RON和VGS的关系由下式给出:

上式表明,在VGS>>VGS(th)的情况下,RON近似地与VGS成反比。为了得到较小的导通电阻,应尽可能取大的VGS值。

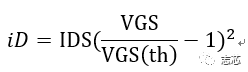

上图b中漏级特性曲线上虚线以右的区域成为恒流区。恒流区里漏极电流iD的大小基本由VGS决定,VDS的变化对iD的影响很小。iD与VGS的关系由下式给出。

其中IDS是VGS=2VGS(th)时iD的值。

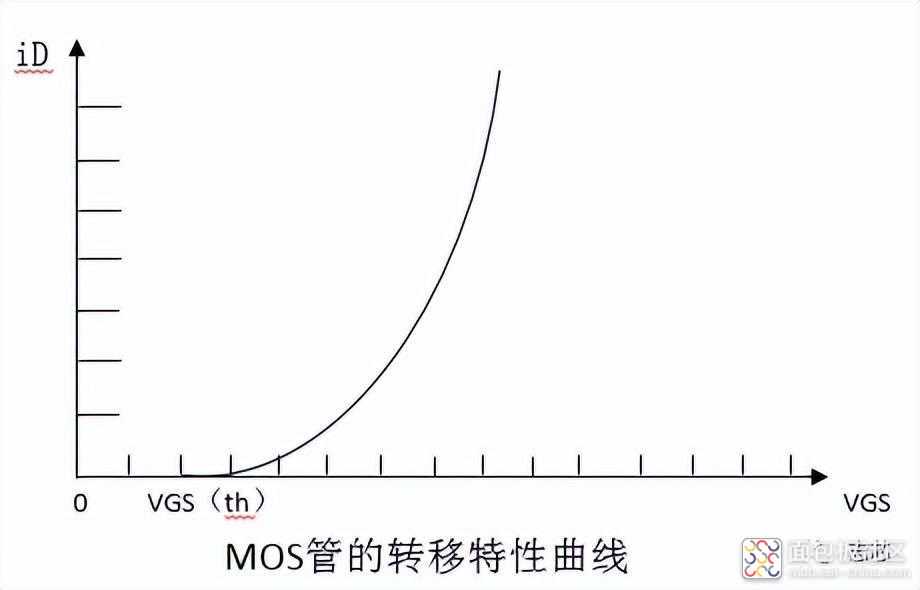

不难看出,在VGS>>VGS(th)的条件下,iD近似地与VGS^2成正比。表示iD与VGS的关系曲线称之为MOS管的转移特性曲线,如图5所示。这条曲线也可以从漏极特性曲线做出。在恒流区中VDS为不同数值时对转移特性的影响不大。

图5

4、MOS管的基本开关电路

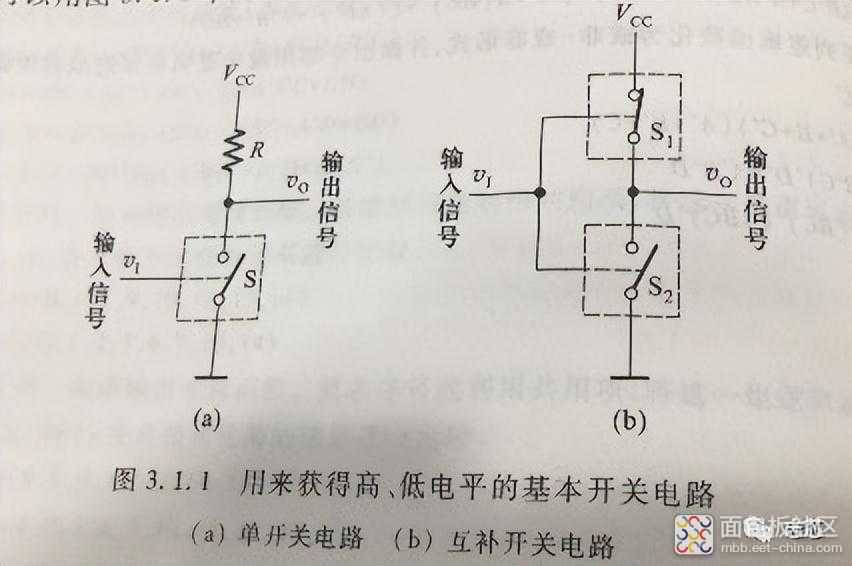

在电子电路中,用高低电平分别表示二值逻辑的1和0两种状态。获得高低输出电平的基本原理用图6所示的两个电路说明。在图6(a)所示的单开关电路中,当开关S断开时,输出电压v0为高电平(VCC);而当S接通以后,输出便为低电平(等于零)。开关S是用半导体三极管组成的。只要能通过输入信号v1控制三极管工作在截止和导通两个状态,它们就可以起到图中开关S的作用(VCC表示接入电路的电压,VDD表示器件内部工作电压,VSS表示公共接地端电压)。

图6

单开关电路的的主要缺点是功耗比较大。当S导通使v0为低电平时,电源电压全部加在电阻R上,消耗在R上的功率为〖VDD〗^2/R。为了克服这个这个缺点,将开关电路中的电阻用另外一个开关代替,就形成了图6(b)所示的互补开关电路。在互补开关电路中,S1和S2两个开关虽然受同一个输入信号v1控制,但是它们的开关状态是相反的。当V1使得S2接通的同时,使S1断开,则v0为低电平;当v1使得S1接通的同时,使得S2断开,则v0为高电平。因为无论v0是高电平还是低电平,S1和S2总有一个是断开的,所以流过S1和S2的电流始终为零,电路的功耗极小。因此这种互补式的开关电路在数字集成电路中得到广泛应用。

以MOS管取代图6(a)中的开关S,便得到图7所示的MOS管开关电路。

图7

当v1=VGS<VGS(th)时,MOS管工作在截止区。只要负载电阻RD远远小于MOS管的截止内阻ROFF,在输出端为高电平VOH,且VOH≈VDD。这时MOS管的D-S间就相当于一个断开的开关。

当v1>VGS(th)并且在VDS较高的情况下,MOS管工作在恒流区,随着v1的升高iD增大,而v0随之下降。由于iD与v1变化量之比不是正比关系,所以v1的大小变化时,△v0与△ v1之比(即电压放大倍数)也不是常数。这时电路工作在放大状态。

当v1继续升高以后,MOS管的导通内阻RON变得很小(通常在1KΩ以内,有的甚至可以小于10Ω),只要RD》RON,则开关电路的输出端将为低电平VOL,且VOL≈0.。这时MOS管的D-S间相当于一个闭合的开关。

综上所述,只要参数选择合理,就可以做到输入为低电平时MOS管截止,开关电路输出高电平;而输入为高电平时MOS管导通,开关电路输出为低电平。

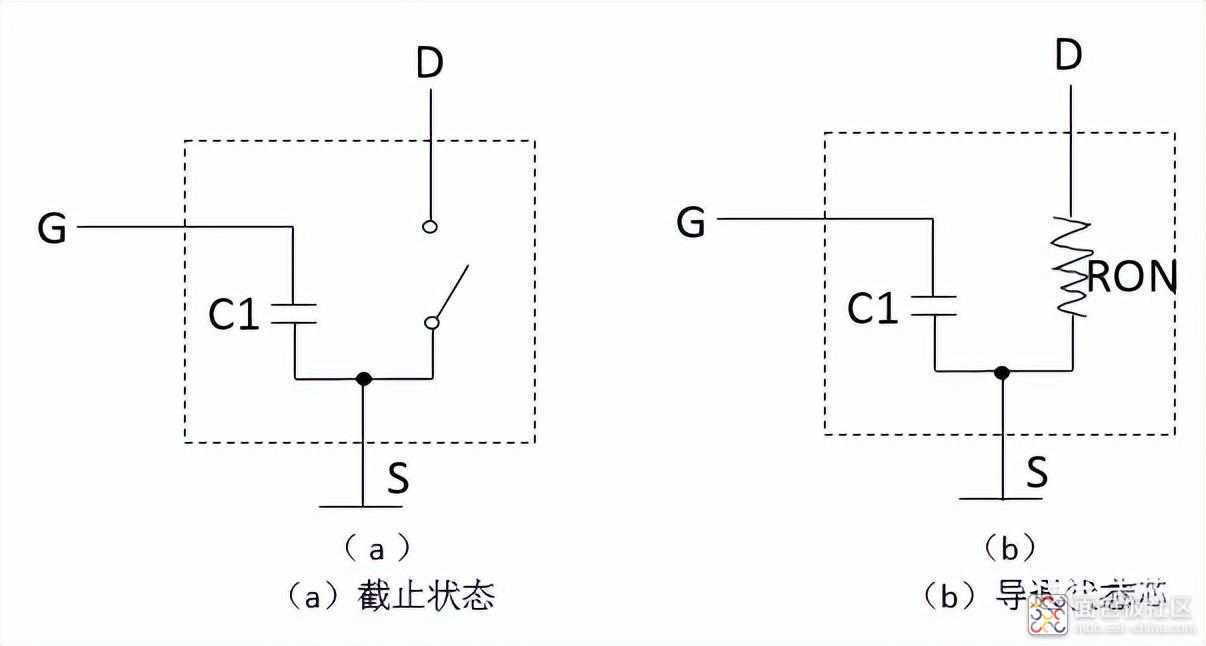

5、MOS管的开关等效电路

由于MOS管截止时漏极和源级之间的内阻ROFF非常大,所以截止状态下的等效电路可以用断开的开关代替,如图8(a)所示。MOS管导通状态下的内阻RON约在1KΩ以内,而且与VGS的数值有关。因为这个电阻阻值有时不能忽略不计,所以在图8(b)导通状态的等效电路中画出了导通电阻RON。

图中的C1代表栅极的输入电容。C1的数值约为几皮法。由于开关电路的输出端不可避免地会带有一定的负载电容,所以在动态工作情况下(即v1在高、低电平跳变时),漏极电流iD的变化和输出电压VDS的变化都将滞后于输入电压的变化。

图8

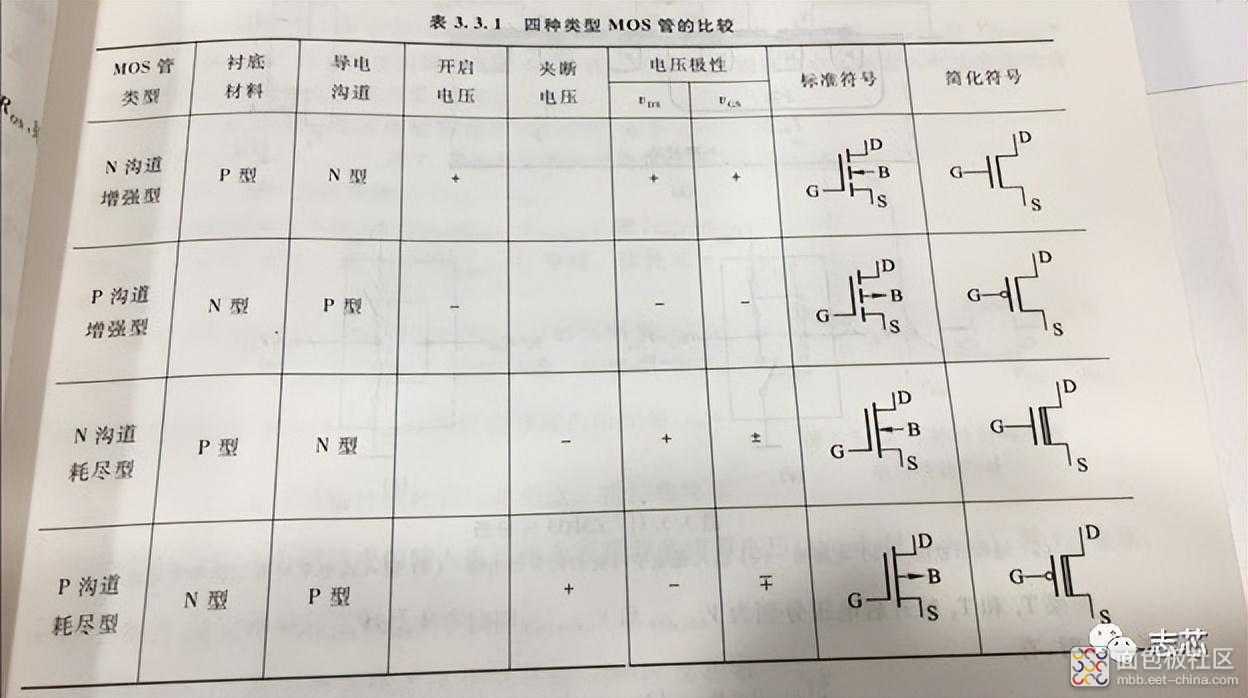

6、MOS管的四种类型

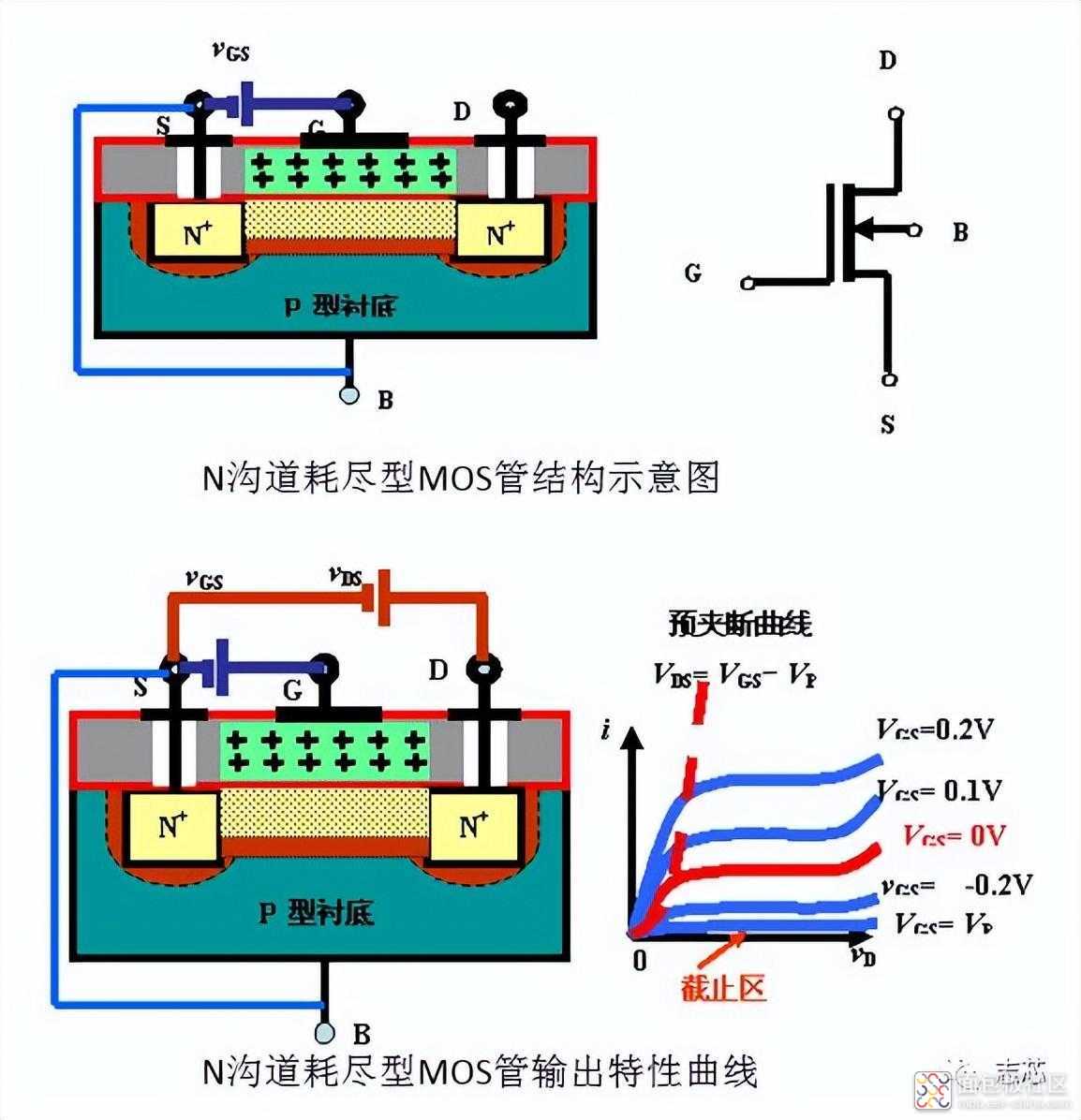

MOS管分为N沟道增强型,P沟道增强型,N沟道耗尽型,P沟道耗尽型四种。N沟道增强型MOS管如前所述。N沟道耗尽型MOS管的结构形式与N沟道增强型MOS管的相同,都采用P型衬底,导电沟道为N型。所不同的是在耗尽型MOS管中,栅极下面的二氧化硅绝缘层中掺进了一定浓度的正离子。这些正离子所形成的电场足以将衬底中的少数载流子——电子吸引到栅极下面的衬底表面,在D-S之间形成导电沟道。因此,在VGS=0时就已经有导电沟道的存在了。VGS为正时导电沟道变宽,iD增大;VGS为负时导电沟道变窄,iD变小。直到VGS小于某一个负电压值VGS(off)时,导电沟道才消失,MOS管截止。VGS(off)称为N沟道耗尽型的MOS管的夹断电压。P沟道耗尽型的MOS管的结构与P沟道增强型的MOS管类似,但是在栅极的绝缘层预先掺杂了一定的负离子,原理与N沟道耗尽型的MOS管类似。

图9

图10

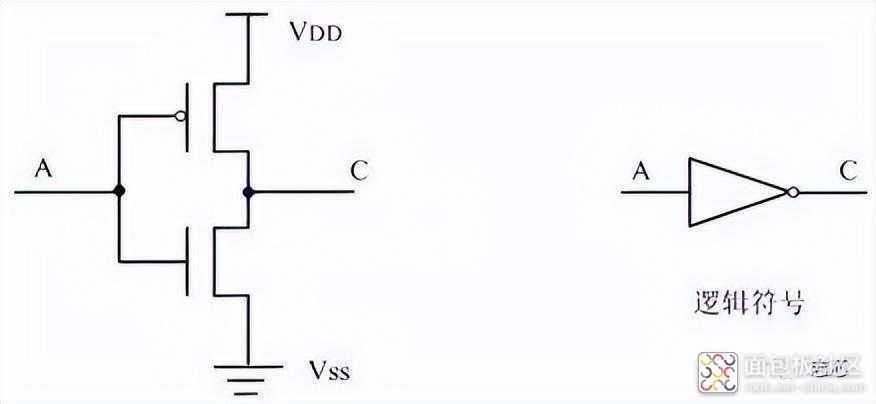

7、非门

非门(反向器)是最简单的门电路,由一对CMOS管组成。其工作原理如下:

A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

图11

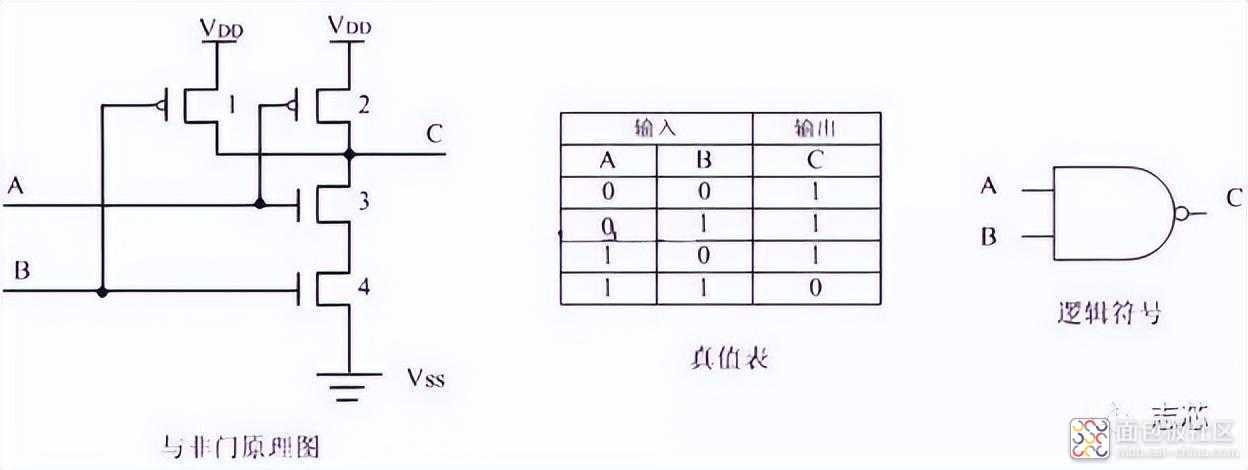

8、与非门

与非门工作原理:

A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

A输入低电平,B输入高电平时,情况与②类似,亦输出高电平。

A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

图12

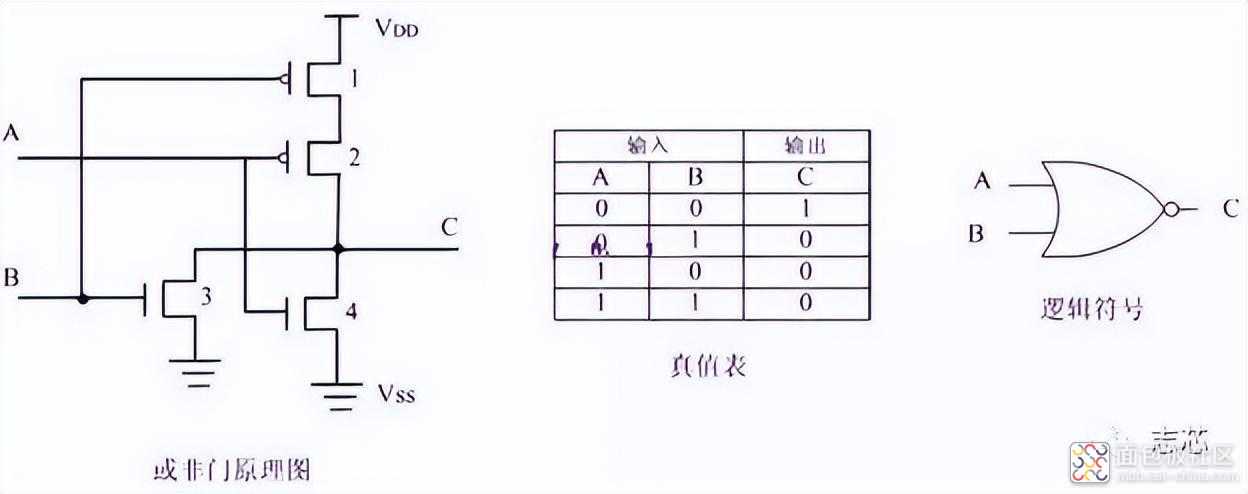

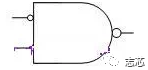

9、或非门

或非门工作原理:

A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

A输入高电平,B输入低电平时,1、4管导通,2、3管截止,C端输出低电平。

A输入低电平,B输入高电平时,情况与②类似,亦输出低电平。

A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平

图13

tips:

将上述“与非”门、“或非”门逻辑符号的输出端的小圆圈去掉,就成了“与”门、“或”门的逻辑符号。而实现“与”、“或”功能的电路图则必须在输出端加上一个反向器,即加上一对CMOS管,因此,“与”门实际上比“与非”门复杂,延迟时间也长些,这一点在电路设计中要注意。

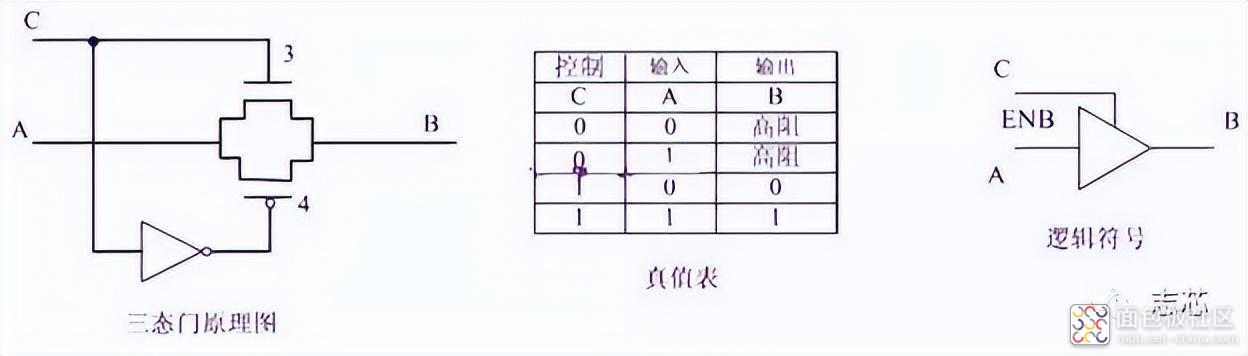

10、三态门

三态门的工作原理:

当控制端C为“1”时,N型管3导通,同时,C端电平通过反向器后成为低电平,使P型管4导通,输入端A的电平状况可以通过3、4管到达输出端B。

当控制端C为“0”时,3、4管都截止,输入端A的电平状况无法到达输出端B,输出端B呈现高电阻的状态,称为“高阻态”。

这个器件也称作“带控制端的传输门”。带有一定驱动能力的三态门也称作“缓冲器”,逻辑符号是一样的。

图14

tips:

从CMOS等效电路或者真值表、逻辑表达式上都可以看出,把“0”和“1”换个位置,“与非”门就变成了“或非”门。对于“1”有效的信号是“与非”关系,对于“0”有效的信号是“或非”关系。

上述图中画的逻辑器件符号均是正逻辑下的输入、输出关系,即对“1”(高电平)有效而言。而单片机中的多数控制信号是按照负有效(低电平有效)定义的。例如片选信号CS(Chip Select),指该信号为“0”时具有字符标明的意义,即该信号为“0”表示该芯片被选中。因此,“或非”门的逻辑符号也可以画成下图。

图15

11、组合逻辑电路

“与非”门、“或非”门等逻辑电路的不同组合可以得到各种组合逻辑电路,如译码器、解码器、多路开关等。

组合逻辑电路的实现可以使用现成的集成电路,也可以使用可编程逻辑器件,如PAL、GAL等实现。

/4

/4